**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<u>www.tesisenxarxa.net</u>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<u>www.tesisenred.net</u>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<u>www.tesisenxarxa.net</u>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

# The MPI/OmpSs Parallel Programming Model

Vladimir Marjanović Department of Computer Architecture Universitat Politècnica de Catalunya

Supervisor: Jesùs Labarta Co-supervisor: Josè Gracia Doctor of Philosophy in Computer Architecture

11th of November, 2015

This page is intentionally left empty.

## Abstract

Even today supercomputing systems have already reached millions of cores for a single machine, which are connected by using a complex network interconnection. Reducing communication time across processes becomes the most important issue in order to achieve the highest possible performance. The Message Passing Interface (MPI), which is the most widely used programming model for large distributed memory, supports asynchronous communication primitives for overlapping communication and computation. However, these primitives are difficult to use and increase code complexity. which then requiring more development effort and making less readable programs.

This thesis presents a new programming model, which allows the programmer to easily introduce the asynchrony necessary to overlap communication and computation. The proposed programming model is based on MPI and tasked based shared memory framework, namely OmpSs.

The thesis further describes implementation details which in order to allow efficient inter-operation of the OmpSs runtime and MPI. The thesis demonstrates the hybrid use of MPI/OmpSs with several applications of which the HPL benchmark is the most important case study. The hybrid MPI/OmpSs versions significantly improve the performance of the applications compared with their pure MPI counterparts. For the HPL we get close to the asymptotic performance at relatively small problem sizes and still get significant benefits at large problem sizes. In addition, the hybrid MPI/OmpSs approach substantially reduces code complexity and is less sensitive to network bandwidth and operating system noise than the pure MPI versions.

In addition, the thesis analyzes and compares current techniques for overlapping computation and collective communication, including approaches using point-to-point communications and additional communication threads, respectively. The thesis stresses the importance of understanding the characteristic of a computational kernel that runs concurrently with communication. Experimental evaluations is done using the Communication Computation Concurrent (CCUBE) synthetic benchmark, developed in this thesis, as well as the HPL.

# Contents

| Co | Contents        |                                     |    |  |  |

|----|-----------------|-------------------------------------|----|--|--|

| Li | List of Figures |                                     |    |  |  |

| Li | st of ]         | ables                               | X  |  |  |

| 1  | Intr            | oduction                            | 1  |  |  |

|    | 1.1             | Goals                               | 2  |  |  |

|    | 1.2             | Methodolgy                          | 4  |  |  |

|    | 1.3             | Contributions                       | 5  |  |  |

|    | 1.4             | Document structure                  | 6  |  |  |

| 2  | Bacl            | ground                              | 9  |  |  |

|    | 2.1             | Parallel machines                   | 9  |  |  |

|    |                 | 2.1.1 Processor architecture trends | 10 |  |  |

|    |                 | 2.1.2 Memory Types in HPC Systems   | 12 |  |  |

|    | 2.2             | Parallel programming models         | 14 |  |  |

|    |                 |                                     | 15 |  |  |

|    |                 | 2.2.2 OpenMP                        | 20 |  |  |

|    |                 | 2.2.3 OmpSs                         | 22 |  |  |

| 3  | Mot             | vation                              | 28 |  |  |

|    | 3.1             | Development Cost                    | 29 |  |  |

|    | 3.2             | MPI Tuning and Its Challanges       | 30 |  |  |

|    |                 |                                     | 31 |  |  |

#### CONTENTS

|   |                    | 3.2.2                                                                | Transfer Issue                                                                                        | 32                                                                                                                     |

|---|--------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   |                    | 3.2.3                                                                | Scalability Issue and Fork/Join Issue                                                                 | 33                                                                                                                     |

|   | 3.3                | Autom                                                                | natic overlap                                                                                         | 35                                                                                                                     |

| 4 | Ana                | lysis an                                                             | d Evaluation of Existing Overlapping Techniques                                                       | 37                                                                                                                     |

|   | 4.1                | Introdu                                                              | action and Motivation                                                                                 | 37                                                                                                                     |

|   | 4.2                | Overla                                                               | pping Techniques and The Nature of Computational Kernels                                              | 39                                                                                                                     |

|   |                    | 4.2.1                                                                | Overlapping Collectives                                                                               | 40                                                                                                                     |

|   |                    | 4.2.2                                                                | Computational Kernels                                                                                 | 43                                                                                                                     |

|   | 4.3                | A Case                                                               | e Studies: Synthetic benchmark and HPL                                                                | 44                                                                                                                     |

|   |                    | 4.3.1                                                                | The C-CUBE benchmark                                                                                  | 44                                                                                                                     |

|   | 4.4                | Result                                                               | s                                                                                                     | 47                                                                                                                     |

|   |                    | 4.4.1                                                                | Platform                                                                                              | 47                                                                                                                     |

|   |                    | 4.4.2                                                                | C-CUBE Evaluation                                                                                     | 48                                                                                                                     |

|   |                    | 4.4.3                                                                | HPL Evaluation                                                                                        | 53                                                                                                                     |

|   | 4.5                | Conclu                                                               | usion                                                                                                 | 55                                                                                                                     |

| 5 | Desi               | gn and                                                               | Implementation of the MPI/OmpSs Programming Model                                                     | 57                                                                                                                     |

|   | 5.1                | Taskifi                                                              | ed MPI calls                                                                                          | 57                                                                                                                     |

|   | 5.2                | 0 1                                                                  | pping Approaches                                                                                      | 58                                                                                                                     |

|   |                    | Overla                                                               |                                                                                                       |                                                                                                                        |

|   |                    | 5.2.1                                                                | Restart mechanism                                                                                     | 58                                                                                                                     |

|   |                    |                                                                      |                                                                                                       | 58<br>61                                                                                                               |

|   | 5.3                | 5.2.1<br>5.2.2                                                       | Restart mechanism                                                                                     |                                                                                                                        |

|   | 5.3<br>5.4         | 5.2.1<br>5.2.2<br>MPI S                                              | Restart mechanism                                                                                     | 61                                                                                                                     |

|   |                    | 5.2.1<br>5.2.2<br>MPI S<br>OmpS                                      | Restart mechanism       Communication thread       erialization and Its Challanges                    | 61<br>65                                                                                                               |

|   | 5.4                | 5.2.1<br>5.2.2<br>MPI S<br>OmpS                                      | Restart mechanism       Communication thread       erialization and Its Challanges       sMPI Library | 61<br>65<br>68                                                                                                         |

|   | 5.4                | 5.2.1<br>5.2.2<br>MPI S<br>OmpS<br>Impler                            | Restart mechanism                                                                                     | 61<br>65<br>68<br>69                                                                                                   |

|   | 5.4                | 5.2.1<br>5.2.2<br>MPI S<br>OmpS<br>Impler<br>5.5.1                   | Restart mechanism                                                                                     | 61<br>65<br>68<br>69<br>69                                                                                             |

| 6 | 5.4<br>5.5         | 5.2.1<br>5.2.2<br>MPI S<br>OmpS<br>Impler<br>5.5.1<br>5.5.2<br>5.5.3 | Restart mechanism                                                                                     | <ul> <li>61</li> <li>65</li> <li>68</li> <li>69</li> <li>69</li> <li>70</li> </ul>                                     |

| 6 | 5.4<br>5.5         | 5.2.1<br>5.2.2<br>MPI S<br>OmpS<br>Impler<br>5.5.1<br>5.5.2<br>5.5.3 | Restart mechanism                                                                                     | 61<br>65<br>68<br>69<br>69<br>70<br>71                                                                                 |

| 6 | 5.4<br>5.5<br>Eval | 5.2.1<br>5.2.2<br>MPI S<br>OmpS<br>Impler<br>5.5.1<br>5.5.2<br>5.5.3 | Restart mechanism                                                                                     | <ul> <li>61</li> <li>65</li> <li>68</li> <li>69</li> <li>69</li> <li>70</li> <li>71</li> <li>74</li> </ul>             |

| 6 | 5.4<br>5.5<br>Eval | 5.2.1<br>5.2.2<br>MPI S<br>OmpS<br>Impler<br>5.5.1<br>5.5.2<br>5.5.3 | Restart mechanism                                                                                     | <ul> <li>61</li> <li>65</li> <li>68</li> <li>69</li> <li>69</li> <li>70</li> <li>71</li> <li>74</li> <li>74</li> </ul> |

#### CONTENTS

|     |                 | 6.1.4 OmpSs HPL                                               | 82  |  |

|-----|-----------------|---------------------------------------------------------------|-----|--|

|     |                 | 6.1.5 Results                                                 | 84  |  |

|     | 6.2             | MPI/OmpSs LINPACK                                             | 91  |  |

|     |                 | 6.2.1 1D Decomposition                                        | 91  |  |

|     |                 | 6.2.2 2D Decomposition                                        | 92  |  |

|     |                 | 6.2.3 Results                                                 | 93  |  |

|     | 6.3             | Matrix Multiplication                                         | 99  |  |

|     | 6.4             | CG 1                                                          | 02  |  |

| 7   | Eval            | ation of Tolerance to Low Bandwidth and OS noise by Using the |     |  |

|     | MPL             | OmpSs approach 1                                              | 106 |  |

|     | 7.1             | Platform                                                      | 07  |  |

|     | 7.2             | Tolerance to OS noise                                         | 07  |  |

|     |                 | 7.2.1 Results                                                 | 08  |  |

|     |                 | 7.2.2 Conclusion                                              | 09  |  |

|     | 7.3             | Tolerance to low bandwidth                                    | 11  |  |

|     |                 | 7.3.1 Results                                                 | 11  |  |

|     |                 | 7.3.2 Conclusion                                              | 15  |  |

| 8   | Rela            | red Work 1                                                    | 19  |  |

| 9   | Conc            | lusion 1                                                      | 22  |  |

|     | 9.1             | Future Work                                                   | 23  |  |

| 10  | Publ            | ications 1                                                    | 26  |  |

| Bił | Bibliography 12 |                                                               |     |  |

# List of Figures

| 2.1 | Example MPI code                                                        | 17 |

|-----|-------------------------------------------------------------------------|----|

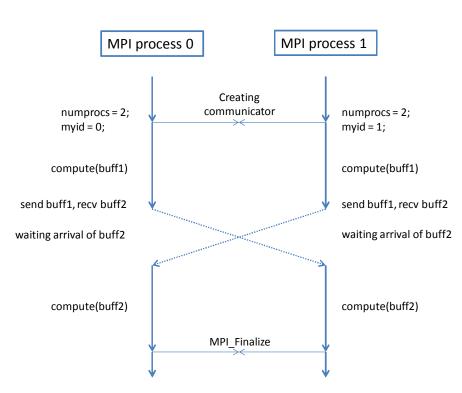

| 2.2 | Execution of the example MPI code                                       | 18 |

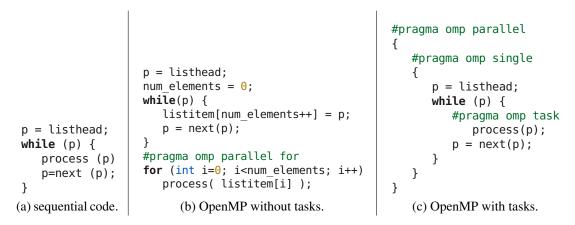

| 2.3 | Pointer chasing application parallelized with OpenMP                    | 21 |

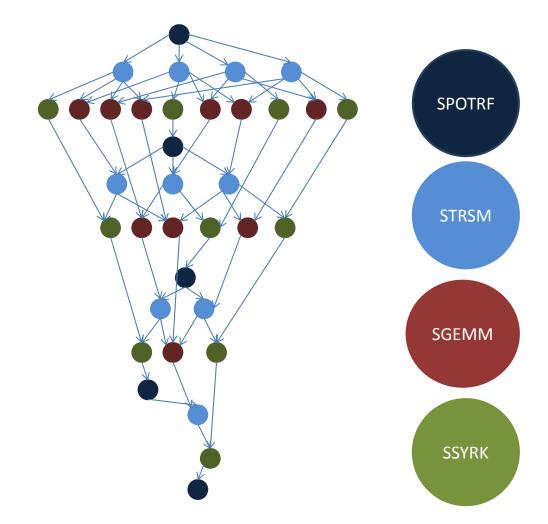

| 2.4 | OmpSs implementation of Cholesky                                        | 26 |

| 2.5 | Dependency graph of Cholesky                                            | 27 |

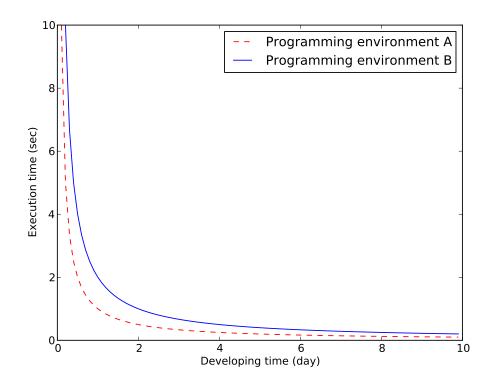

| 3.1 | Modeling programming environments. A curve presents the properties      |    |

|     | of the programming environment                                          | 30 |

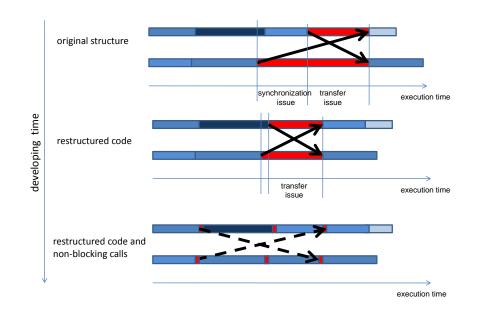

| 3.2 | Tuning challenges: Synchronization Issue and Transfer Issue and how     |    |

|     | to address them. X axis is the exuction time, Y axis is the development |    |

|     | time. Red chunks are idle state. Blue chunks are running state          | 32 |

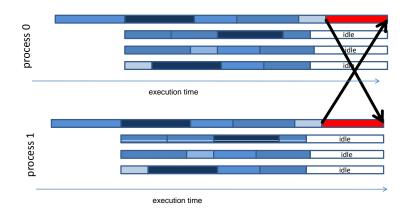

| 3.3 | Scalability Issue: MPI/OpenMP improves the scalability issue but in-    |    |

|     | troduces fork/join issue. First four lines present a process 0 with for |    |

|     | 4 threads, second four lines present the process 1 with 4 threads. Red  |    |

|     | chunks are idle state. Blue chunks are running state. White chunks are  |    |

|     | idle states due to fork/join issue                                      | 34 |

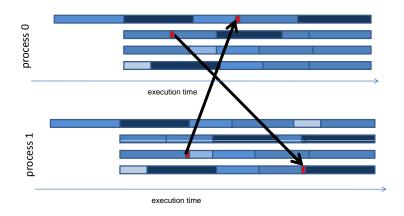

| 3.4 | The execution with automatic overlapping and reordering. Blue chunks    |    |

|     | are running states                                                      | 36 |

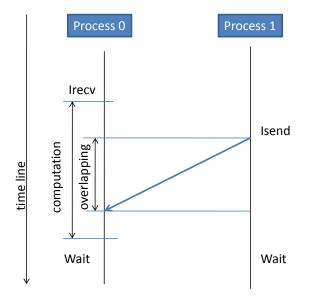

| 4.1 | Overlapping communication and computation by using nonblocking          |    |

|     | point-to-point calls.                                                   | 40 |

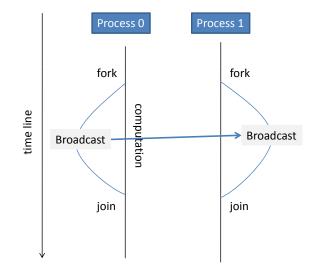

| 4.2 | Overlapping communication and computation by using blocking thread.     | 42 |

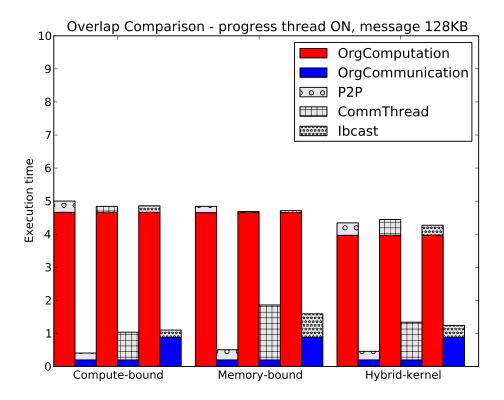

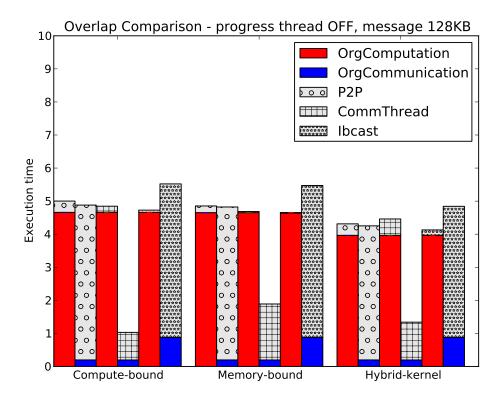

| 4.3 | The execution time of communication and computation for various         |    |

|-----|-------------------------------------------------------------------------|----|

|     | computation kernel and overlapping techniques when the progress thread  |    |

|     | is disabled and the message size is 128KB                               | 50 |

| 4.4 | The execution time of communication and computation for various         |    |

|     | computation kernel and overlapping techniques when the progress thread  |    |

|     | is disabled and the message size is 128KB                               | 52 |

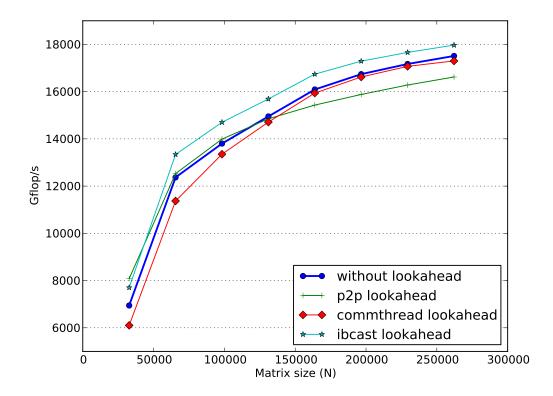

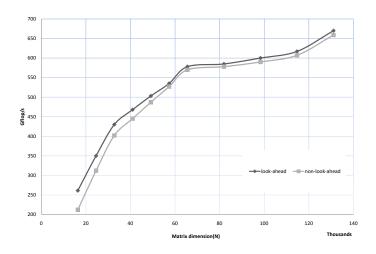

| 4.5 | Performance comparison of look-ahead techniques for different prob-     |    |

|     | lem sizes.                                                              | 54 |

| 5.1 | Execution stages of the restart mechanism.                              | 59 |

| 5.2 | Receive operation implemented by using the restart mechanism            | 60 |

| 5.3 | Broadcast operation implemented by using the restart mechanismm         | 60 |

| 5.4 | Distribution of the OmpSs threads across cores                          | 62 |

| 5.5 | Broadcast operation implemented by using commucanition thread           | 63 |

| 5.6 | Usage of cpu cycles by using commucanition thread                       | 64 |

| 5.7 | Data Flow Graph of the HPL; MPI task serialized                         | 67 |

| 5.8 | Implementation of OmpSs_MPI_Recv                                        | 68 |

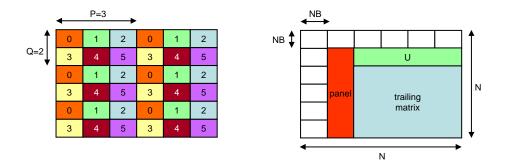

| 6.1 | P by Q partitioning of the matrix in 6 processes (2x3 decomposition)    |    |

|     | (a) and one step in the LU factorization (panel, U and trailing matrix) |    |

|     | (b)                                                                     | 75 |

| 6.2 | Simplified version of the main loop in HPL                              | 76 |

| 6.3 | Version of the HPL pseudocode with look-ahead equals to one             | 77 |

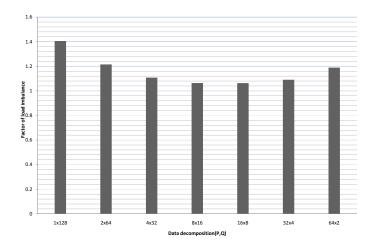

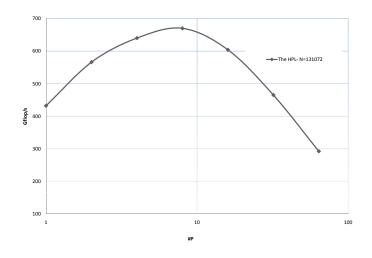

| 6.4 | Performance analysis of HPL of look-ahead and load balancing            | 80 |

| 6.5 | Performance analysis of HPL for different problem size and block size.  | 81 |

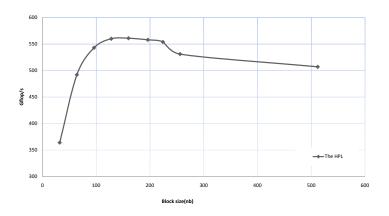

| 6.6 | Taskifying the factorization and the update.                            | 83 |

| 6.7 | Data dependency graph of the OmpSs HPL                                  | 84 |

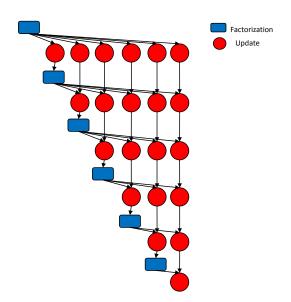

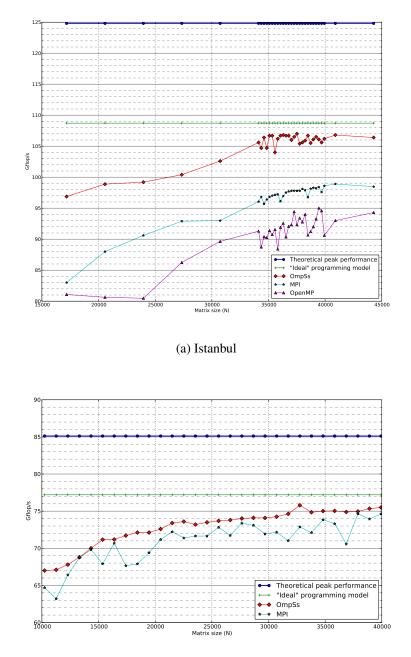

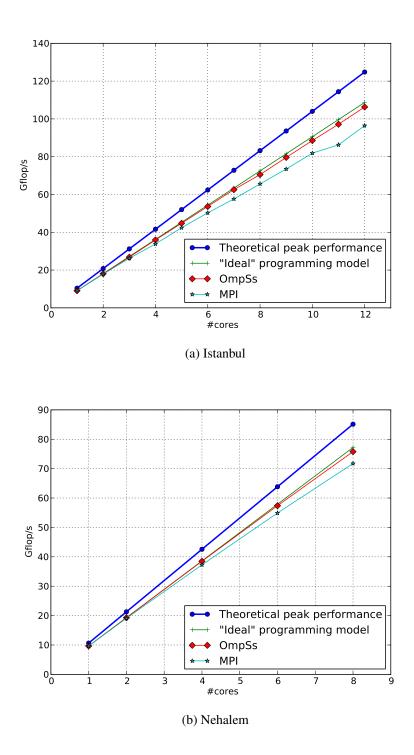

| 6.8 | Istanbul 12 cores and Nehalem 8 cores. Performance results of the       |    |

|     | HPL for different problem size NB=242. Theoretical peak perfor-         |    |

|     | mance, "Ideal" programming model, MPI, OmpSs and OpenMP                 | 87 |

| 6.9 | Istanbul and Nehalem Evaluation. Scalability N=16384 and NB=242.        |    |

|     | Theoretical peak performance, "Ideal" programming model, MPI, OmpSs     |    |

|     | and OpenMP                                                              | 88 |

|     |                                                                         |    |

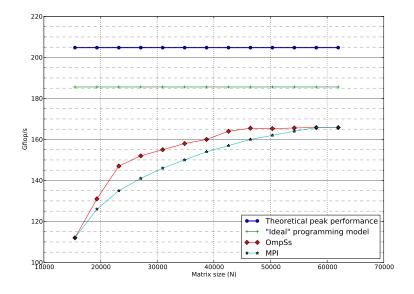

| 6.10 | 0 Altix 32 cores. Performance results of the HPL for different problem      |    |

|------|-----------------------------------------------------------------------------|----|

|      | size NB=242. Theoretical peak performance, "Ideal" programming              |    |

|      | model, MPI and OmpSs                                                        | 89 |

| 6.11 | 1 Altix. Scalability. Performance results of the HPL for different prob-    |    |

|      | lem size NB=242. Theoretical peak performance, "Ideal" program-             |    |

|      | ming model, MPI and OmpSs                                                   | 90 |

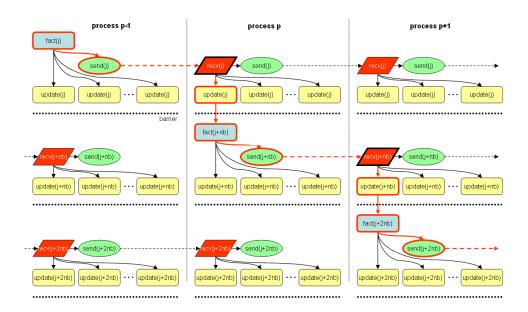

| 6.12 | 2 Partial dataflow graph in the execution of HPL: MPI process execution     |    |

|      | in vertical and iteration j of main loop in horizontal. Nodes correspond    |    |

|      | to the different tasks: fact (panel factorization), send (panel send), recv |    |

|      | (panel receive) and update (panel update)                                   | 92 |

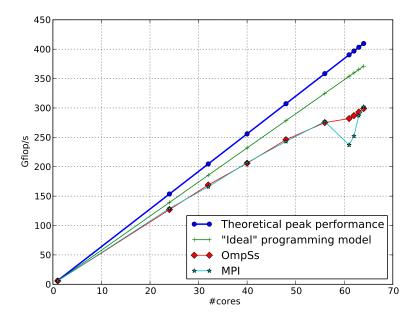

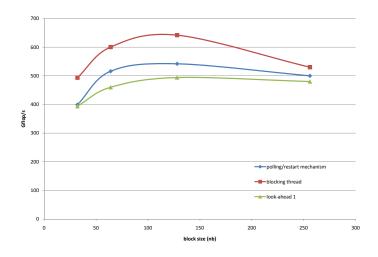

| 6.13 | 3 Performance comparison of overlapping technique: the restart mecha-       |    |

|      | nism, the communication thread and the look-ahead technique                 | 95 |

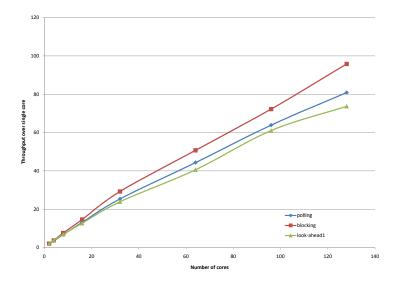

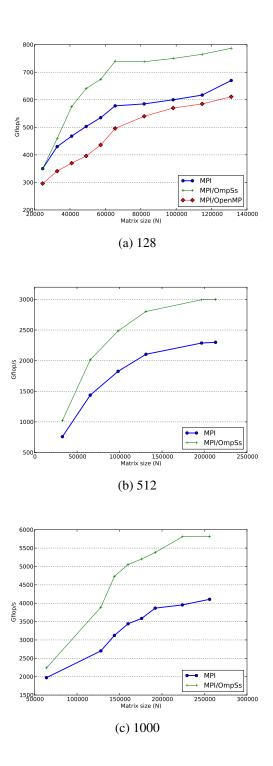

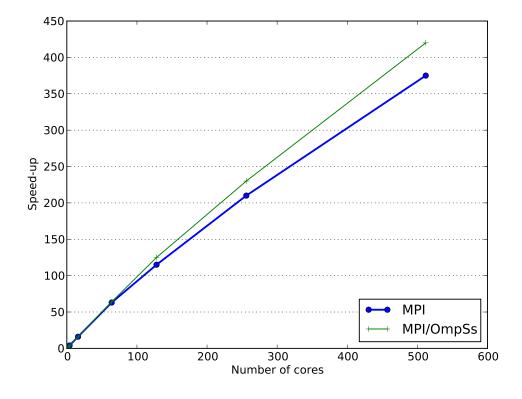

| 6.14 | 4 HPL: performance in Gflops for original MPI version with look-ahead       |    |

|      | and for the hybrid MPI/OmpSs. Results are presented for 128, 512 and        |    |

|      | 1000 processors                                                             | 96 |

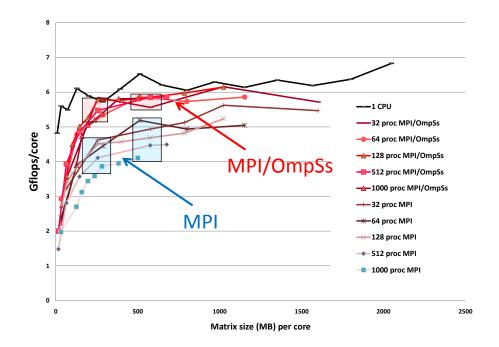

| 6.15 | 5 Gflops/core                                                               | 98 |

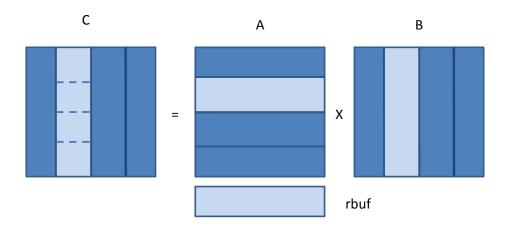

| 6.16 | 6 Serial implementation of the matrix multiplation                          | 99 |

| 6.17 | 7 MPI implementation of the matrix multiplation 1                           | 00 |

| 6.18 | 8 Data distribution for matrix multiplation acrooss 4 MPI process. Each     |    |

|      | process contains a part of matrix A and matrix B                            | 00 |

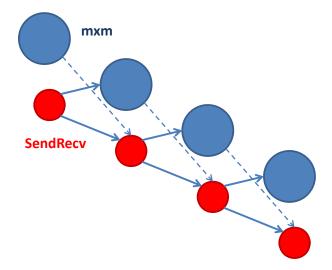

| 6.19 | 9 Task Dependence Graph of matrix multiplation. White nodes cor-            |    |

|      | respond to mxm instances, blue nodes correspond to SendRecv in-             |    |

|      | stances, solid edges correspond to true data dependences and dashed         |    |

|      | edges correspond to antidependences (due to the reuse of data storage       |    |

|      | for communication). The data renaming done at runtime eliminates            |    |

|      | these antidependences and the execution of successive SendRecv invo-        |    |

|      | cations without waiting for the termination of previous mxm invocations.    | 01 |

| 6.20 | 0 data distribution. $\ldots$ $\ldots$ $\ldots$ $1$                         | 02 |

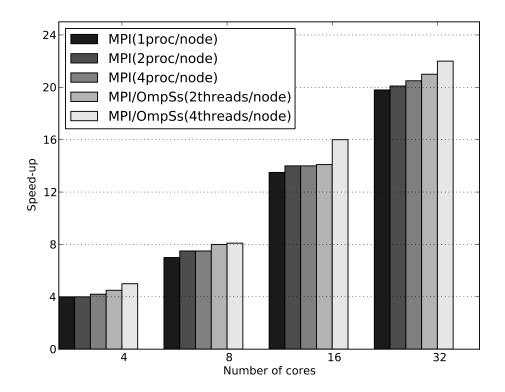

| 6.21 | 1 Matrix multiply: performance comparison of pure MPI (running differ-      |    |

|      | ent number of MPI processes per node) and hybrid MPIOmpSs (with             |    |

|      | different number of OmpSs threads per node). Results are for a matrix       |    |

|      | size of 8192x8192                                                           | 03 |

| 6.22 | Main loop in conjugate gradient using blocking and non-blocking col-   |     |

|------|------------------------------------------------------------------------|-----|

|      | lectives                                                               | 104 |

| 6.23 | Hybrid MPI/OmpSs version of the CG.                                    | 104 |

| 6.24 | Conjugate gradient: performance comparison of pure MPI and hybrid      |     |

|      | MPI/OmpSs.                                                             | 105 |

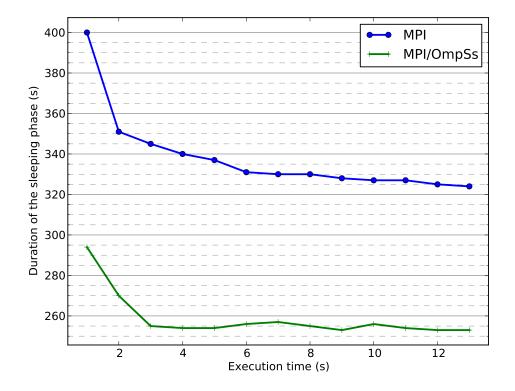

| 7.1  | HPL: sensitivity to process preemptions. Results are for 128 proces-   |     |

|      | sors. Problem size N=65536, NB=256. Decomposition 8x16                 | 110 |

| 7.2  | HPL: sensitivity to process preemptions. Results are for 512 proces-   |     |

|      | sors. Problem size N=131072, NB=256. Decomposition 16x32               | 111 |

| 7.3  | Loop body for the iterative jacobi in the Poisson equation solver. An- |     |

|      | notated functions using OmpSs.                                         | 113 |

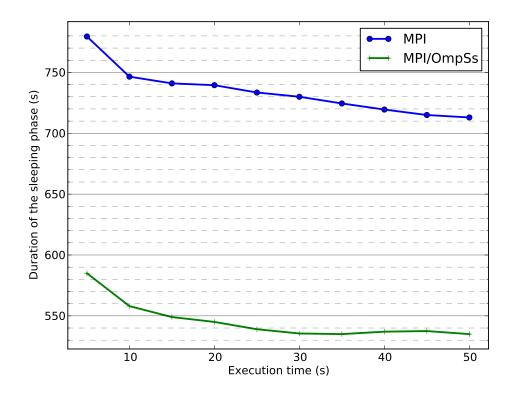

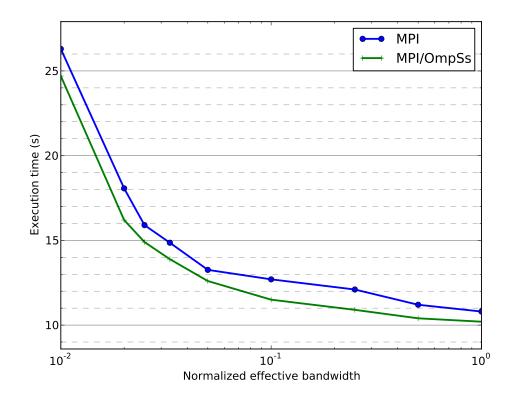

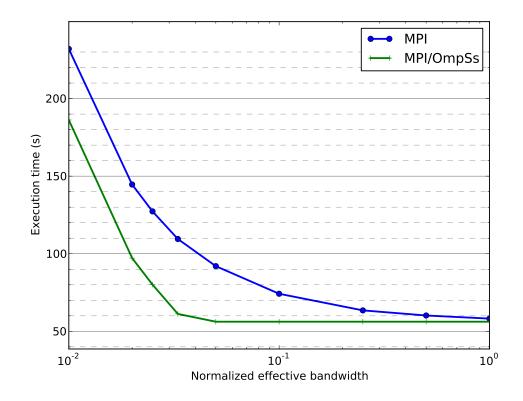

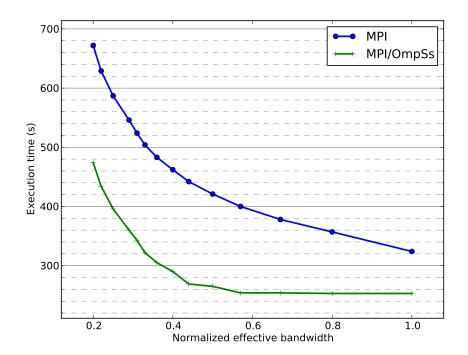

| 7.4  | NAS BT: sensitivity to low network bandwidth. Results are for class    |     |

|      | B and 64 processors.                                                   | 115 |

| 7.5  | Jacobi Solver: sensitivity to low network bandwidth. Results are for   |     |

|      | 64 processors                                                          | 116 |

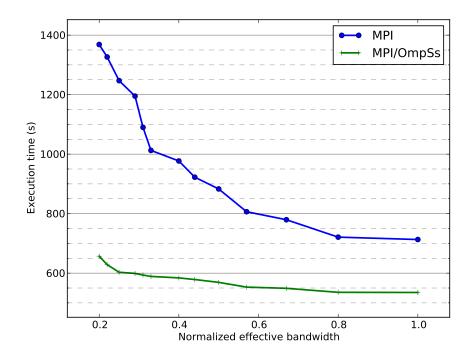

| 7.6  | HPL: sensitivity to low network bandwidth. Results are for: 128 pro-   |     |

|      | cessors. Problem size N=65536, NB=256. Decomposition 8x16              | 117 |

| 7.7  | HPL: sensitivity to low network bandwidth. Results are for: 512 pro-   |     |

|      | cessors. Problem size N=131072, NB=256. Decomposition 16x32            | 118 |

|      |                                                                        |     |

# List of Tables

| 4.1 | The exection time of computation and communication for various over-   |    |

|-----|------------------------------------------------------------------------|----|

|     | lapping techniques, computational kernels, mode of the progress thread |    |

|     | and message size                                                       | 49 |

| 4.2 | Frequency polling of asynchronous broadcasts for dirrent problem sizes |    |

|     | and the thread progress mode.                                          | 53 |

# Introduction

Scientists and engineers recognize that computers can help solving problems that would be too complex and expensive with other methods. Computational modeling and simulation of these problems became a new methodology and standard tool in academia and industry. Dealing with these applications requires powerful systems in terms of raw cpu speed, main memory and data store. A single workstation as a desktop machine would never fulfill these requirements due to size of problem. Demand for high performance parallel machines is a logical step in order to address these issues. High-Performance Computing (HPC) systems delivers much higher performance than one could get out of a typical desktop computer or workstation in order to solve large problems in science, engineering, or business. The HPC systems with a very high-level computational capacity, also called supercomputer, could efficiently deal with a large non-embarrassingly parallel problems of earth and life since.

In contrast to large data center, an HPC machine contains thousands of processors and complex interconnection networks between these processors. Raw computational power of large data centers, e.g. Amazon data center [23] cannot processes large nonembarrassingly problems within reasonable time-frame, due to low performance of interconnection network. This lack of high bandwidth and low latency interconnection network is the main difference between computational data centers and HPC systems. Efficient hardware and software approaches of communication between processors are the biggest challenges for computer scientist in HPC world.

Hardware of HPC system is very robust, expensive and complex and requires a software stack for users with specialized expertise to use. Regarding interconnection network, hardware designers try to minimize latency and maximize bandwidth, while software designers try to exploit hardware properties as efficiently as possible and minimize communication and synchronization cost between processors. Complexity of HPC systems grows constantly and programming effort become expensive in terms of time to solution, pushing users to understand hardware and software of machines. Software layer should provide easy to use interface for programmers and keep high efficiency of HPC systems.

To tackle productivity, in this thesis we explore software techniques for efficient communication between processors and propose a hybrid programming model based task based programming model OmpSs and the distributed programming model MPI. The programming model offers high performance and high productivity at the same time. Finding well balanced ratio between programability/performance, porting time for already existing codes, and portability drive the work of the thesis to the MPI/OmpSs programming approach as a future tool for scientist.

# **1.1 Goals**

HPC aims a high performance, thus the main goal of this thesis is to propose a programming model that achieves high efficiency. While a single thread performance execution leans on compiler optimization and a single thread optimization techniques, parallel programming focuses on efficiency of parallel execution. The following challenges are addressed by this work:

• *Increase Parallelism* - making all available computing resources busy is the first step to high performance. Parallel programming models should offer a flexible execution model, where idle states of computing units are minimize. Introducing

a term '*degree of resource utilization*' as the ratio between the number of independent task and a number of computing units. A degree of resource utilization greater than 1 leads to the perfect parallelism. The goal is to keep the degree as high as possible in every moment of execution.

- *Scalability* The goal of programming models is customization and a scalable execution model, that matches complex node architecture and schedules task in a fashion that N, cores speed up N times sequential execution

- *Hiding communication overhead* Tasks need communication operations, accelerating and hiding communication operation is the key. The communication overhead is the biggest challenge for parallel programming paradigm and capability of programming model to minimize communication costs determines its efficiency. The main goal of the thesis is to reduce communication cost during execution.

- *Tolerance to network contention* HPC systems contain powerful interconnection network, in order to move data across distributed nodes and fulfill task dependencies. Nevertheless, nonuniform utilization of network stresses interconnection throughput and slows down execution. The programming model should distribute communication over time, relax the interconnection network while overall performance does not suffer.

- *Tolerance to OS jitters* driving applications across large number of cores increase possibility that unpredictable performance drops might appear on any core caused by system noise. The performance drop of one thread propagates to overall performance and lowers efficiency. The goal of parallel execution modeling is to filter non-deterministic noise and smoothly muffle performance degradation.

- *Code Complexity* once the parallel programming model shows a successful improvement in term of performance, programming effort stays a big challenge. There is no clear metric that evaluates programming productivity and ranks parallel programming approaches. Programmers usually focus on expressing an algorithm, once the code gives correct results tuning optimization phase take

place. Improving performance increases code complexity while new radical programming approaches discharge programmers to learn them. The goal of the programming model is a friendly, easy-to-use interface, where codes stays as close as possible to an initial version where the algorithm has been described. The syntax of a programming model should be as natural as possible.

The overall goal of the thesis aims at a future way of thinking regarding parallel programming on HPC systems, both for, programmers and programming model developers.

# **1.2 Methodolgy**

Proposing a future programming model requires review of state-of-the art programming model. De facto, Message Passing Interface (MPI), is the most accepted programming model for distributed memory systems. Almost all applications have been written using the MPI paradigm. MPI is a library that can be used with C/C++ or FORTRAN. MPI forms a basis for the thesis and can be considered as a one of the low level programming layer for the proposed programming model.

On shared memory, level the most used parallel programming approach is OpenMP annotations of C/C++ or FORTRAN. The OmpSs interface extends OpenMP features and introduces flexibility and task based view. Nevertheless, OmpSs is not as widely accepted as OpenMP. It presents the state of the art and a new way of approaching parallelism on shared memory level. OmpSs together with MPI are future of programming in HPC world and are the starting point of the thesis research.

Selecting MPI and OmpSs programming models, would help programmer productivity and smooth transition of existing codes. Improving performance and exploring capabilities of combined MPI and OmpSs approach present a real challenge. In order to understand optimization technique of MPI and reducing communication overhead by using MPI. The thesis does detailed analysis of already existing overlapping technique of communication and computation. Understating both computation and communication lead to an optimal time to solution execution.

Once performance techniques of the chosen programming model has been understood, the thesis defines easy to use interface that combines MPI and OmpSs. A clear metric for friendly use interface does not exist, and feedback of potential users and already experience developers play the key role.

In order to address performance goals, the thesis shows a novel idea that merges features of MPI and OmpSs and software optimization techniques.

Portability across different HPC systems, requires customization of the run-time. Understanding hardware architecture, OS system implementation and implementation of MPI libraries show potential capabilities of MPI/OmpSs programming approach where the run-time implementation proves ideas.

Experiments and proof of concept of programming model, require well written highly optimized and widely known HPC applications. In order to compare results the thesis uses several HPC applications on different platforms and focuses on the High Performance Linpack (HPL) benchmark [15]. The fact that the HPL is used to order TOP500 [48] supercomputer places it to the most important HPC benchmark.

## **1.3 Contributions**

This work makes the following contributions:

- 1. Investigation of techniques to overlap communication and computations in MPI applications.

- 2. Analysis and demonstration of the impact of a computational kernel on overlapping techniques and time to solution.

- 3. Demonstration that granularity of computational routines effects overlapping efficiency and thus needs to be tuned.

- 4. Proposing a hybrid MPI and OmpSs programming model, define user interface for MPI/OmpSs.

- 5. Propose overlapping techniques and their implementation by using MPI/OmpSs programming model.

- 6. Address implementation challenges of overlapping techniques on various HPC architectures.

- 7. Propose OmpSs\_MPI library, a message passing library for MPI/OmpSs programming model.

- 8. Demonstration of porting by using MPI/OmpSs programming model on different HPC applications.

- 9. Evaluate of MPI/OmpSs on different HPC applications and their basic comparison with original MPI versions.

- 10. Comment a high efficiency of MPI/OmpSs for small problem sizes.

- 11. Investigate a tolerance to low bandwidth and OS jitters by using MPI/OmpSs.

This work makes the three main contributions:

- Investigation of techniques to overlap communication and computations in MPI applications. Analysis and demonstration of the impact of a computational kernel on overlapping techniques and time to solution.Demonstration that granularity of computational routines effects overlapping efficiency and thus needs to be tuned.

- Proposing a hybrid MPI and OmpSs programming model, define user interface for MPI/OmpSs. Propose overlapping techniques and their implementation by using MPI/OmpSs programming model. Address implementation challenges of overlapping techniques on various HPC architectures. Propose OmpSs\_MPI library, a message passing library for MPI/OmpSs programming model.

- 3. Demonstration of porting by using MPI/OmpSs programming model on different HPC applications. Evaluate of MPI/OmpSs on different HPC applications and their basic comparison with original MPI versions. Comment a high efficiency of MPI/OmpSs for small problem sizes. Investigate a tolerance to low bandwidth and OS jitters by using MPI/OmpSs.

# **1.4 Document structure**

The document is organized as follows:

- Chapter 2 presents the state-of-the-art technology related to the topic of this thesis. It provides a survey on the hardware architecture and parallel programming models. First, it introduces parallel computers and their benefits over single thread computing approaches. Then it reviews the software stack which is used on parallel computers.

- Chapter 3 illustrates the performance issues in current parallel programming environment and criticizes inefficient approaches that solves the performance issues. The Chapter 3 criticizes a poor programming productivity of proposed software optimization.

- In Chapter 4, the thesis analyses and compares overlapping technique of collective communication and computation based nonbloking interface, point-to-point approach and additional thread approach. It also emphasizes characteristics of computational kernels which overlap communication. The Chapter 4 outputs results that give clear guidelines for the MPI/OmpSs programming model.

- Chapter 5 is the kernel of the thesis. It proposes the MPI/OmpSs programming model, defines an user interface of the model, adds overlapping techniques to the OmpSs run-time, and explains implementation of the OmpSs run-time on different architectures.

- Furthermore Chapter 6 evaluates the proposed programming model in terms of performance. It introduces applications used for experiments and their characteristics. The Chapter presents and discusses results of ported HPC applications on different platforms and shows performance advantages of MPI/OmpSs programming model.

- In addition Chapter 7 proofs and demonstrates the high tolerance to low bandwidth networks and OS jitters of the MPI/OmpSs programming model. It describes a method to mimic low bandwidth network and simulates OS noise. It comments performance results of the MPI/OmpSs application affected by mentioned phenomenon.

- Chapter 8 presents previous work related to the research covered in this thesis, while Chapter 9 draws conclusion of this thesis and presents the direction of the

future research in this field.

• Finally, Chapter 10 lists the papers published as the results of this thesis.

# 2 Background

This Chapter presents the state-of-the-art technology related to the topic of this thesis. Section 2.1 gives background on the architecture of parallel machines in HPC. It explains parallel machines on shared-memory and distributed-memory level, the section also reviews architectures specially build for HPC systems. Section 2.2 describes the parallel programming approaches for HPC systems. It focuses on the Message Passing Interfaace(MPI) library as the most widely accepted approach for distributed-memory parallel machines. The section introduces task based programming model called the OmpSs that extends OpenMP.

# 2.1 Parallel machines

Modern science stimulates the rapid growth of high performance computing. When experimental and theoretical science join to computational science, large and powerful machines became a basic tool for them. The constant need for higher performance caused the appearance of machines with parallel architecture. Single core machines have not been able to fulfill scientific requirements. Multiplying single compute units, efficiently solved embarrassingly parallel problems but more likely real problems requires interconnection network between compute nodes due to dependent work across parallel machines. Building parallel machines brought challenges in hardware and software design. In the rest of this section, we present concepts related to HPC parallel computing for hardware and software.

### 2.1.1 Processor architecture trends

In the early 1960 there ware sever factors where experimental science evolved into computation science, and required large computer resources to solve their problems. The price of the advantage single-processor computer increases faster than its computational power. So, the price/performance ratio points to the direction of parallel computers. During the '80 PC (personal computers) has increased the performance and price of single-processor computers has fallen. Also the price of interconnection network have fallen , thus a PC workstation has provided a significant computer power on a small budget.

Manufacturing more powerful PC computers was building processors with higher operational frequency. The straight-forward approach for making faster computers is making a computer that operates at a higher clock frequency. During the '90 the vendors increased frequency, which makes all software running faster. The HPC systems followed the same trend by building the system out of commercial processors made for servers. However, increased frequency dramatically increases chip's power consumption. Therefore, computing platforms have hit the "power wall", so frequency scaling stopped at around 3 GHz.

From then on, improving single core performance introduces more computational unit additional functional units, additional registers, wider path, cache size etc. Exploring new resources required new chip design and lead to instruction level parallelism (ILP).

The following hardware approches appeared:

1. **Instruction pipelining** (ILP) where the execution of multiple instructions can be partially overlapped.

- 2. **Superscalar execution**, and the closely related explicitly parallel instruction computing concepts, in which multiple execution units are used to execute multiple instructions in parallel.

- 3. Out-of-order execution where instructions execute in any order that does not violate data dependencies. Note that this technique is independent of both pipe-lining and super-scalar. Current implementations of out-of-order execution dynamically (i.e., while the program is executing and without any help from the compiler) extract ILP from ordinary programs. An alternative is to extract this parallelism at compile time and somehow convey this information to the hardware. Due to the complexity of scaling the out-of-order execution technique, the industry has re-examined instruction sets which explicitly encode multiple independent operations per instruction.

- 4. **Register renaming** which refers to a technique used to avoid unnecessary serialization of program operations imposed by the reuse of registers by those operations, used to enable out-of-order execution.

- 5. **Speculative execution** which allow the execution of complete instructions or parts of instructions before being certain whether this execution should take place. A commonly used form of speculative execution is control flow speculation where instructions past a control flow instruction (e.g., a branch) are executed before the target of the control flow instruction is determined. Several other forms of speculative execution have been proposed and are in use including speculative execution driven by value prediction, memory dependence prediction and cache latency prediction.

- 6. **Branch prediction** which is used to avoid stalling for control dependencies to be resolved. Branch prediction is used with speculative execution.

However, since the techniques of implicit parallelism showed only limited potential, new computer architectures targeted higher performance by allowing the programmer to explicitly expose parallelism. The presented techniques exposed parallelism without any involvement of the programmer – the user programmed a sequential control flow but the underlying system automatically exposed parallelism. However, the implicit parallelism turned on to be insufficient. An alternative approach puts multiple independent cores in one chip and allows the programmer to have a different control flow in each of the cores. These parallel architectures provided more flexibility in using the computation resources, but also increased the complexity of programming.

## 2.1.2 Memory Types in HPC Systems

HPC systems tend to be multi-core systems that access memory in two different ways: first shared-memory systems where cores are sharing physical memory and a single instance of operating systems control threads and processes, second distributed memory systems where several instances of operating system control local threads and processes while communication protocol allows communication between distributed memory system. Machines can also contain both approach where locally shared memory system are connected between each other as a big distributed memory system.

#### **Shared-Memory Systems**

Shared memory system appears as a solution for parallel computing where a single operation system and its adress space work on top of multicore hardware. The shared memory hardware connects all processing units and main memory, each processing unit can access the whole memory directly. Processors read and write to shared variables and communication throught them. Programming model and operation system provide a framework and programmer uses the shared variables in order to enforce correct exectution.

Parallel machines through shared variables is the easiest way to build parallel program because inter-process communication is implicit. Programmer should not be concerned with data locality. Shared variables create easy perspective on the global memory space. These machines is very difficult to build in terms of fast access to all addresses of memory from all processes. Reaching low latency in shared memory machines is the biggest challenge for hardware designers. Programmer does not need to provide any hints about data locality and thus a hardware cannot predict and overlap communication between memory and processing unit.

The Multi-threading execution model is widely used for shared memory machines. A single process launches several threads within the same address space. Threaded programming approach introduces a shared variable concept. Threads read and write to shared variable and a system preforms implicit communication. Valid shared variable is stored in the single address location within memory.

Accessing time from processing units to memory can be uniform or nonuniform, so there are two type of memory architecture: uniform memory access (UMA) architecture and nonuniform memory access (NUMA) architecture.

- UMA access time to a memory location is independent of which processor makes the request or which memory chip contains the shared variable. Thus, UMA platforms are often called symmetric multiprocessors (SMP). The main disadvantage of UMA architecture is scalability. Bandwidth of a single memory bank becomes the bottleneck for large number of processors.

- NUMA: Noways, shared memory systems are based on NUMA memory architecture. Instead of a single memory bank, NUMA contains several memory banks where the memory access time depends on the memory location relative to the processor. Accessing to its local memory is faster than non-local memory. NUMA attempts to address UMA single memory bank issue by providing separate memory for each processor, a voiding the performance penalty when several processors attempt to address the same memory. NUMA improves scalability compared with UMA architecture.

#### **Distributed Memory Systems**

Distributed memory machines (DMM) are computers with physically distributed memory. Each node is an independent unit that consists of a processor and a local memory. An interconnection network connects all the nodes and allows communication among them. Each node can only access its local memory. If a node needs data that is not in its local memory, the data needs to be transferred using message-passing.

Distributed memory machines evolve by improving the interconnection network and decoupling the network from the nodes. The nodes are usually connected by pointto-point interconnection links. Each node connects to a finite number of neighboring nodes. The network topology is regular, often a hypercube or a tree. Since each node can send the message only to its neighboring nodes, limited connectivity significantly restricts programming. Initially, communication between nodes that have no direct connection had to be controlled by software of the intermediate nodes. However, new intelligent network adapters enabled data transfers to or from the local memory without participation of the host processor. This allowed that the host processor can be efficiently computing while, in background, there is a transfer to/from it. Furthermore, the state-of-the-art networks optimize communications by dedicating special links for executing multicast transfers.

A distributed memory machine consists of loosely coupled processing units, making it easy to assemble but difficult to program. DMMs can be assembled using offthe-shelf desktop computers. However, to achieve high performance, the nodes must be interconnected using a fast network. On the other hand, DMMs are very difficult to program. The programmer must explicitly specify the data decomposition of the problem across processing units with separate address spaces. Also, the programmer must explicitly organize inter-processor communication, making both the sender and the receiver aware of the transfer. Moreover, the programmer must take special care about data partitioning among the nodes, because delivering some data from one node to another may be very expensive. Thus, the data layout must be selected carefully to minimize the amount of the exchanged data.

# 2.2 Parallel programming models

There is no efficient and highly applicable automatic parallelization. The biggest idea of parallel computation was to find techniques that would automatically expose parallelism in the applications. However, despite decades of work, automatic parallelization showed very limited potential. Today, the only viable solution is to rely on the programmer to expose parallelism.

For distributed memory machines, the mainstream programming models are message passing (MP) and partitioned global address space (PGAS). The most popular implementation of MP model is message passing interface (MPI) [44]. In MPI, the programmer must partition the workload among processes with separate address spaces. Also, the programmer must explicitly define how the processes communicate and synchronize in order to solve the problem. Conversely, PGAS model is implemented in languages such as UPC [10], X10 [12] and Chapel [11]. PGAS model provides a global view for expressing both data structures and the control flow. Thus, as opposed to message passing, the programmer writes the code as if a single process is running across many processors.

On the other hand, OpenMP [14] is a de-facto starndard for programming shared memory machines. OpenMP extends the sequential programming model with a set of directives to express shared-memory parallelism. These directive allow exposing fork-join parallelism, often targeting independent loop iterations. Nevertheless, OmpSs programming model [17] extends OpenMP offering semantics to express dataflow parallelism. Compared to fork-join parallelism exposed by OpenMP, the parallelism of OmpSs can be much more irregular and distant. Throughout this thesis, we focus mainly on OmpSs as a programming model for shared memory machines.

#### 2.2.1 MPI

Message Passing Interface (MPI) [44] is the most widely used programming model for programming distributed parallel machines. To facilitate writing message-passing programs, MPI standard defines the syntax and semantics of useful library routines. Today, MPI is the dominant programming model in high-performance computing.

In the MPI programming model, multiple MPI processes compute in parallel and communicate by calling MPI library routines. At the initialization of the program, a fixed set of processes is created. Typically, the optimal performance is achieved when each MPI process is mapped on a separate core. For easier coordination among processes, MPI interface provides functionality for communication, synchronization and virtual topology.

The most essential functionality of MPI is point-to-point communication. The most popular library calls are: MPI\_Send to send a message to some specified process; and MPI\_Recv to receive a message from some specified process. Point-to-point operations are especially useful for implementing irregular communication patterns. A point-to-point operation can be in synchronous, asynchronous, buffered, and ready form, providing stronger and weaker synchronization among communicating processes. The ability to probe for messages allows MPI to support asynchronous communication. In asynchronous mode, the programmer can issue many outstanding MPI operations.

Collective operations allow communication of all processes in a process group. The process group may consist of the entire process pool, or it may be user defined subset of the entire pool. A typical operation is MPI\_Bcast (broadcast), in which the specified root process sends the same message to all the processes in the specified group. A reverse operation is MPI\_Reduce, in which the specified root process receives one message from all the processes in the specified group. Additionally, the root performs an operation on all the received messages. MPI\_Alltoall is the most expensive routine where all processes send and receive message from all processes. Other collective operations implement more sophisticated communication patterns.

Throughout its evolution, MPI standard introduces new features to facilitate easier and more efficient parallel programming. The initial MPI-1 specification focused on message passing within a static runtime environment. Additionally, MPI-2 includes new features such as parallel I/O, dynamic process management, one-sided communication, etc. While MPI-3 introduces non-blocking collective operations [24].

#### A simple program

In this section, we present a simple program and explain the runtime properties of MPI execution. The example shows a simple code with only two sections of useful work (function *compute*) and one section that exchanges data (function *MPI\_S endrecv*). Each MPI process executes function *compute* on local buffer *buff*1, then sends the calculated buffer *buff*1 to its neighbor. At the same time, each process receives buffer *buff*2 from other neighbor, and again executes function *compute* on the received buffer. The processes communicate in one-sided ring pattern – each process receives the buffer from the process with rank for 1 lower, and sends the calculated buffer to the process with rank for 1 higher.

All the processes start independently, learning more about the parallel environment by calling  $MPI_Init$ . MPI execution starts by calling MPI agent (*mpirun* – nx./binary.exe) that spawns the specified number (x) of MPI processes. In the studied case (Figure 2.2), the MPI execution starts with 2 independent MPI processes. By calling  $MPI_Init$ , each process learns about the MPI parallel environment. All the MPI processes are grouped into the universal communicator ( $MPI_COMM_WORLD$ ). Using the universal communicator, each process identifies the total number of MPI pro-

```

1 #include <mpi.h>

2 #include <stdio.h>

3 #include <string.h>

4

5 int main(int argc, char *argv[])

6 {

float buff1[BUFSIZE], buff2[BUFSIZE];

7

8

int numprocs;

int myid;

9

10

int tag = 1;

11

12

MPI Status stat;

13

MPI_Init(&argc,&argv);

14

15

/* find out how big the SPMD world is */

16

MPI Comm size(MPI COMM WORLD,&numprocs);

17

/* and this processes' rank is */

18

MPI Comm rank(MPI COMM WORLD,&myid);

19

20

21

/* At this point, all programs are running equivalently,

the rank distinguishes the roles of the programs in the SPMD model */

22

23

/* compute on the local data (buff1) */

24

25

compute(buff1);

26

27

/* exchange data (send buff1 and receive buff2 )*/

28

my_dest = (myid + 1) % numprocs;

29

my_src = (myid + numprocs - 1) % numprocs;

MPI Sendrecv( /* sending buffer */ buff1, BUFSIZE, MPI FLOAT,

30

/* destination MPI process */ my_dest, tag,

31

/* receiving buffer */ buff2, BUFSIZE, MPI_FLOAT,

32

/* source MPI process */ my_src, tag,

33

34

MPI_COMM_WORLD, &stat);

35

36

/* compute on the received data (buff2) */

37

compute(buff2);

38

39

/* MPI programs end with MPI Finalize; this is a weak synchronization point */

40

MPI Finalize();

41

42

return ₀;

43 }

44

```

Figure 2.1: Example MPI code

cesses in the system (*MPI\_comm\_size*) and gets the unique rank of the process (*MPI\_comm\_rank*).

Each MPI process, knowing its rank and the size of the universal communicator, identifies its role in the execution of the parallel program. Each process identifies the part of the total workload that is assigned to it. Also, each process identifies the

Figure 2.2: Execution of the example MPI code

ranks of the neighboring processes with which it should communicate in order to make the job done. In the presented example, based on *myid* and *numprocs*, each process calculates ranks of its neighboring processes (*my\_dest* and *my\_src*) to generate the one-sided ring communication pattern.

When the computation on the local data finishes, the processes communicate to exchange the data and start the next phase of computing on the local data. Each process calculates the buffer buff1 in the function *compute*. Then, the process sends the processed buff1 to the neighboring process. At the same time, the process receives a message from some other neighboring process and stores the content of that message into local buffer buff2. Then, the process locally computes on buff2 in another instantiation of function *compute*. Thus, MPI process 0 calculated on its local buff1, and then after the  $MPI\_S$  endrecv call, it calculated on its local buff2 (that was buff1 local to MPI process 1).

When the useful work finishes, all the processes call *MPI\_Finalize* to announce the end of the parallel section. *MPI\_Finalize* implicitly calls a barrier, waiting for all the MPI processes from *MPI\_COMM\_WORLD* to come to this point. When all

the processes reach the barrier, the joint work is guaranteed to be finished, and all the processes can exit the parallel execution independently. The parallel execution finishes.

This simple example also illustrates one of the main topics of this thesis – communication delays caused by MPI execution. When both processes finish executing compute(buf f 1), they initiate their transfers in the same moment. While the messages are in transit, both processes are stalled without doing any useful work. Chapter 3 further illustrates this problem and presents some of the possible solutions.

#### **Relevant features of MPI implementation**

MPI standard defines a high-level user interface, while low-level protocols may vary significantly depending of the implementation. MPI provides a simple-to-use portable interface for a basic user, setting a standard for hardware vendors what they need to provide. This opens space for various MPI implementations that have different features and performances.

First, depending on the implementation, MPI messaging may use different messaging protocols. An MPI message passing protocol describes the internal methods and policies employed to accomplish message delivery. Two common protocols are

- **eager** an asynchronous protocol in which a send operation can complete without an acknowledgement from the matching receive; and

- **rendezvous** a synchronous protocol in which a send operation can complete only upon the acknowledgement from the matching receive.

Eager protocol is faster, as it requires no "handshaking" synchronization. However, this relaxation of synchronization compensates with the increased memory usage for message buffering. Thus, a common implementation uses eager protocol only for messages that are shorter than the specified threshold value. On the other hand, messages larger than the threshold are transferred using rendezvous protocol. Also, it is common that a very long message is partitioned into chunks, with each chunk being transferred using outstanding rendezvous protocol.

Also, MPI implementations provide different interpretation of independent progress of transfers. Independent progress defines whether the network interface is responsible for assuring progress on communications, independent of making MPI library calls. This feature is especially important for the messages that use rendezvous protocol. For example, rank 0 sends a non-blocking transfer to rank 1 using rendezvous protocol. If rank 0 comes to its *MPI\_Isend* before rank 1 comes to the matching receive, rank 0 issues handshaking request and leaves the non-blocking send routine. Later, when rank 1 enters its corresponding *MPI\_Recv*, it acknowledges the handshake, allowing rank 0 to send the message. The strict interpretation of the independent progress mandates that rank 0 sends the actual message as soon as it receives the acknowledgement from rank 1. Conversely, the weak interpretation mandates that rank 0 must enter some MPI routine in order to process the acknowledgement and prepare for the actual message transfer. Here, the weak interpretation of independent progress will be very performance degrading if after the non-blocking send, rank 0 enters a very long computation with no MPI routine calls. Most of the state-of-the-art networks provide the strict implementation of progress by introducing interrupt-driven functionality in the network interface.

Depending on the computation power of the network interface, an MPI implementation can provide different ability for communication/computation overlap. MPI standard specifies semantic for asynchronous communication that offers significant performance opportunities. However, in some machines, the processors are entirely responsible for assuring that the message reaches its destination. Still, most of the state-of-the-art networks provide intelligent network adapters that take care of delivering the message, allowing the processor to dedicate to useful computation. This way it is possible to achieve overlap of communication and computation – a feature that is considered of a major importance for high parallel performance.

## 2.2.2 OpenMP

OpenMP (Open Multi-Processing) [14] is the mainstream programming model for programming shared memory parallel systems. OpenMP is an application programming interface (API) that supports multi-platform shared memory programming in C, C++, and Fortran. It uses a portable model that provides to programmers a simple and flexible interface for developing parallel applications for platforms ranging from the standard desktop computer to the supercomputer. OpenMP allows integration with MPI, providing a hybrid MPI/OpenMP model for parallel programming at large scale.

Figure 2.3: Pointer chasing application parallelized with OpenMP

OpenMP is a programming model based on fork-join parallelism. On reaching a parallel section, a master thread forks a specified number of slave threads. All the threads run concurrently, with the runtime environment mapping threads to different processors. When the parallel section finishes, the slave threads join back into the master. Finally, the master continues through the sequential section of the program.

It remains a question whether OpenMP loop parallelization could be widely applicable. OpenMP is tailored for applications with array-based computation. These application have very regular parallelism and regular control structures. Thus, OpenMP can identify all work units in the compile time and statically assign them to multiple threads. However, irregular parallelism is inherent in many applications such as tree data structure traversal, adaptive mesh refinement and dense linear algebra. These applications would be very hard to parallelize using only basic OpenMP syntax.

Let us consider possible OpenMP parallelization of the sequential code from Figure 2.3a. The program consists of a while loop that updates each element of the list. The code cannot be parallelized just by adding parallel loop construct, because the list traversal would be incorrect. Thus, in order to use parallel loop construct, the list first has to be translated into an array (Figure 2.3b). However, this translation causes the inadmissible overhead.

In order to tackle this issue, OpenMP introduces support for tasks. Tasks are code segments that may be deferred to a later time. Compared to the already introduced work units, tasks are much more independent from the execution threads. First, a task is not bound to a specific thread – it can be dynamically scheduled on any of

the active threads. Also, a task has its own data environment, instead of inheriting the data environment from the thread. Moreover, tasks may be synchronized among themselves, rather than synchronizing only separate threads. This implementation of OpenMP tasks allows much higher expressibility of irregular parallelism.

Figure 2.3c illustrates the possible parallelization of the studied code using OpenMP tasks. The master thread runs and dynamically gives a raise to each instantiation of the task *process*. On each instantiation, the content of pointer p is copied into the separate data environment of the task. Since the inputs to the task are saved, the task can execute later in time. Thus, the master thread sequentially traverses the list and dynamically spawns tasks. The spawned tasks are executed by the pool of worker threads. When the main thread finishes spawning all tasks, it joins the workers pool. Therefore, despite of irregular control structures, OpenMP tasks allow elegant parallelization.

## 2.2.3 **OmpSs**

Omp Superscalar (OmpSs) [17] is a parallel programming model based on dataflow execution. OmpSs is an effort to extend OpenMP with new directives to support dataflow parallelism. Compared to fork-join parallelism exposed by OpenMP, the parallelism of OmpSs can be much more irregular and distant.

The OmpSs programming model extends the standard C, C++ and Fortran programming languages with a set of pragmas/directives to declare functions that are potential tasks and the intended use of the arguments of these functions.

There are two essential annotations needed to port a sequential application to OmpSs function-header | function-definition

With the following possible clauses:

- in(data-reference-list)

- out(data-reference-list)

- inout(data-reference-list)

The name, Superscalar, came from the same idea as a superscalar CPU where out-of-order execution of instructions mapping out-of-order execution of annotated functions. Superscalar programming family uses concepts mentioned in the section 2.1 which explains the ILP techniques. What is an instruction for ILP, it is an annotated function for OmpSs. Hardware implementation allows instruction level parallelism while OmpSs runtime as a software implementation provides function level parallelism.

Based on the in/out specifications and the actual arguments in function invocations, the runtime system is able to determine the actual data dependencies between tasks and schedule their parallel execution such that these dependencies are satisfied. The dependencies derived at runtime replace the use of barriers in most of the cases, allowing the exploitation of higher degrees of distant parallelism. Given the OmpSs annotations, the runtime can schedule all tasks out-of-order, as long as the data dependencies are satisfied.

The OmpSs environment consists of a source-to-source compiler that substitutes the original invocations of the annotated functions with calls to an add\_task runtime call, specifying the function to be executed and its arguments. The resulting source code is compiled using the platform native compiler and linked to the OmpSs runtime library. The add\_task runtime call uses the memory address, size and directionlity of each parameter at each function invocation to build a dependence task graph. A node in the task graph is added to represent the newly created task and it is linked to previous task on whose output it depends. Once a task is finished, the runtime looks in the graph for tasks that depend on this one and if they have no other pending dependencies they are interted into the ready queue. Concurrently with this main thread, a set of worker threads, started at initialization time, traverse this list looking for tasks ready for execution. In the case that the main thread encounters a synchronization (barrier, wait on specific data or end of the program) it cooperates with the worker threads to execute pending tasks.

In order to eliminate false dependencies (i.e. dependencies caused by data reuse), the OmpSs runtime is capable of dynamically renaming data objects, leaving only true dependencies. This is the same technique used in current superscalar processors and optimizing compilers to remove false dependencies due to the reuse of registers. In SMPSs the renaming may apply to whole regions of memory passed as arguments to a task. Such renaming is implemented by the runtime, allocating new data regions and passing the appropriate pointers to the tasks, which themselves do not care about the actual storage positions passed as arguments. The runtime is responsible for properly handling the actual object instance passed to successive tasks. Also if necessary, it copies back the data to its original position.

This renaming mechanism has the potential to use available memory to increase the actual amount of parallelism in the node. An excessive use of renaming may result in swapping and introduce a high performance penalty. A parameter in a configuration file limits the size of memory that can be used for renaming.

The priority clause gives a hint to the runtime system about the "urgency" when scheduling the task. The runtime has two ready queues and tasks from the high priority queue are selected before tasks in the low priority queue. This mechanism allows a programmer with global understanding of the critical computations to influence the actual scheduling.

One of the main goals of scheduling in OmpSs is to exploit data locality. In that regard the scheduler takes advantage of the graph information in order to schedule dependent tasks to the same core so that output data is reused immediately.

The programmer can add the *priority* clause to some task, indicating that the task has higher scheduling priority. These tasks are scheduled as soon as possible.

The OmpSs runtime is also aware about NUMA memory architecture and schedules a task according to NUMA locality of task arguments. The OmpSs scheduler contains a queue for NUMA domain and work stealing is supported. Applications do not have the same behavior, so the scheduling options are configurable from the configuration file where a user could tune scheduler for targeted application.

OmpSs programming model supports also programming heterogeneous architectures. By adding *target* clause to the pragma construct, OmpSs can declare that instances of some task are to be executed on hardware accelerators. Reading these annotations, the runtime schedules the execution of the specified task on the dedicated hardware and automatically moves all the needed data for that task. This feature significantly facilitates the easy programming of heterogeneous architectures, as it was proven for programming Cell B./E. [6] and Nvidia GPUs[9].

OmpSs is a most promising programming approach in HPC world. It makes porting of sequential applications natural and straight-forward approach. A programmer could focus on expressing an algorithm, while the OmpSs runtime cares about performance and parallel execution. This thesis is based on the OmpSs approach and merge MPI and OmpSs. The OpenMP 4.0 standard introduced OpenMP Task Dependency Support, thus it could be used as an implementation platform for the work of this thesis.

#### Example of irregular parallelism – Cholesky

Figure 2.4 shows OmpSs parallelization of a Cholesky code. In order to parallelize Cholesky code with OmpSs, only four code lines need to be added. All four functions called from *compute* are encapsulated into tasks using *#pragma omp task* directives. For each of these functions, pragma directives also specify the directionality of function parameters. This type of coordinating tasks on the shared variables is much easier for the programmer than determining what variables should be shared or private among the threads. After adding the annotations, the resulting code has the same logical structure as the original sequential code. Also, note that compiling this OmpSs code with non-OmpSs compiler simply ignores OmpSs pragmas and creates a binary for the corresponding sequential execution.

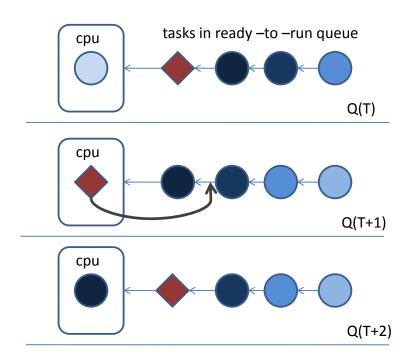

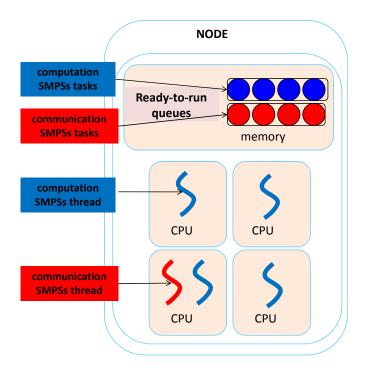

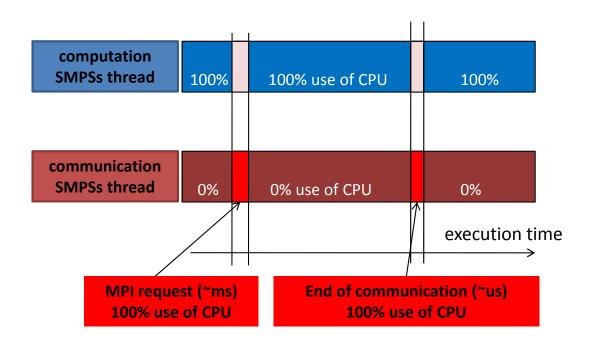

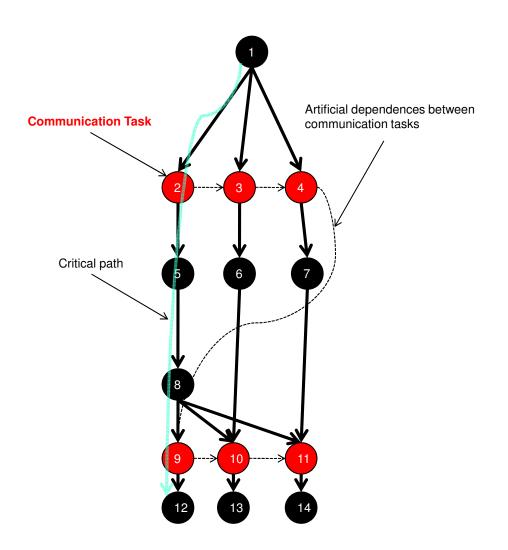

In parallel execution of this code, the annotated tasks can execute out-of-order, as long as data-dependencies are satisfied. The program initiates with only one active thread – the master thread. When the master thread reaches a taskified function, it instantiates that function into a task and wires in the new task instance into the tasks dependency graph, see 2.5. Considering the dependency graph, the runtime schedules out-of-order execution of tasks.