**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<u>www.tesisenxarxa.net</u>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<u>www.tesisenred.net</u>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<u>www.tesisenxarxa.net</u>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

# Runahead Threads

## Tanausú Ramírez García

UNIVERSITAT POLITECNICA DE CATALUNYA Departament d'Arquitectura de Computadors

©2010 TANAUSU RAMIREZ GARCIA ALL RIGHTS RESERVED

# **Runahead Threads**

## Tanausú Ramírez García

Advisors: Mateo Valero Universitat Politècnica de Catalunya Alex Pajuelo Universitat Politècnica de Catalunya Oliverio J. Santana Universidad de Las Palmas de Gran Canaria

A THESIS SUBMITTED IN FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY (COMPUTER SCIENCE) DOCTOR POR LA UPC A mis padres, por su amor, apoyo y aliento

## Acknowledgments

Esta tesis ha sido el resultado de una gran aventura fuera de mi tierra, Gran Canaria. Durante este largo camino, ha habido muchos momentos de alegría y satisfacción personal, así como de malos y duros momentos. Sin embargo, he tenido la suerte de contar con el apoyo de muchas personas, a las cuales les quiero dedicar estas líneas pues sin ellas no habría llegado hasta aquí.

En primer lugar, quiero agradecer a mi director de tesis, Mateo Valero, por su confianza en mí desde el principio. Sin aún conocerme, me invitó a una cena de un congreso nacional, y le bastó un trayecto en su coche desde Lleida a Barcelona para animarme a hacer el doctorado. Mateo me ha brindado su ayuda, sus conocimientos y su apoyo, así como la oportunidad de comenzar mi carrera investigadora en el Departamento de Arquitectura de Computadores (DAC) de la UPC.

Igualmente, quiero dar las gracias a mis otros directores de tesis. A Alex Pajuelo, por su confianza e infalible ayuda tanto en el aspecto profesional como en el personal para que este trabajo saliera adelante. A Oliver Santana, por su dedicación y ayuda prestada en todo momento tanto aquí como desde la distancia. Posiblemente esta tesis no estaría terminada sin vuestra ayuda, simplemente gracias.

Para realizar esta tesis tuve que moverme de Las Palmas a Barcelona, y con ello dejé atrás a mi familia y muchos amigos en Canarias. En este viaje, agradecer especialmente a Carmelo Acosta, amigo y compañero desde el colegio, Javier Verdú y Fran Cazorla compañeros también en la ULPGC. Todos ellos, ya doctores, tomaron previamente el mismo camino que yo, animándome a venir, haciendo mi llegada más fácil y ayudándome en todas las situaciones durante estos años. Gracias Carmelo y Hema por ofrecerme vuestra casa, pero especialmente vuestra compañía en los primeros momentos.

Una vez aquí, también he conocido a nuevas personas estupendas, que además de compañeros de doctorado se han convertido en muy buenos amigos. Entre ellos, quiero mencionar especialmente a Josep María Codina, Ayose Falcón, Ana Bosque, Jaume Abella y Rubén Gran. Me gustaría agradecerles su apoyo, ánimo, amistad y compañía en las diferentes etapas de esta tesis, pero sobre todo gracias por los momentos de diversión que me ayudaron a superar los obstáculos con alegría.

También agradecer a tantos otros compañeros del DAC que he ido conociendo durante estos años, y con los cuales he podido compartir reuniones de trabajo, sala de becarios, horas de comida, cafés y muchas otras actividades: Adrián Cristal, Marco Galluzi, Alejandro García, Beatriz Otero, Jordi Guitart, Germán Rodríguez, Llorenç Cruz, Ramon Canal, Fermín Sanchez, Javi Alonso, Miquel Moreto... y muchos más que espero que no se molesten por no nombrar aquí. Igualmente dar las gracias al resto de profesores y miembros del departamento que lo conforman y lo hacen uno de los más importantes del mundo en su área de conocimiento.

Del mismo modo, destacar que todo este trabajo ha sido financiado por la beca FPU AP2003-3682 del Ministerio de Educación y Ciencia, así como por las líneas de investigación de la Comisión Interministerial de Ciencia Y Tecnología (CICYT) TIN-2004-07739 y TIN2007-60625, y también por la red europea de excelencia High Performance Embedded Architectures and Compilers (HiPEAC).

Personalmente, esta tesis no sólo ha supuesto un reto profesional sino seguramente un gran cambio en mi vida. Gracias a la tesis, he podido conocer otra tierra, otra gente, viajar y realizar muchas otras actividades, como entrar en el mundo de la salsa. Y así, bailando salsa, he podido desconectar de las situaciones de estrés y abatimiento en los momentos más difíciles. Pero lo más importante es que he conocido a muchas personas salseras que valen la pena, Oscar, Susana, Joaquín, Cristina Robles, Eva, Cristina Salinas, Luba, Patrick... y a las cuales quiero agradecerles los muchos momentos de diversión y amistad que han compartido conmigo.

De manera muy especial, quiero dar las gracias de todo corazón a Judit, la persona más maravillosa que he podido conocer, pues su forma de ser transformó nuestro baile en amor. No tengo palabras para agradecerle su cariñosa compañía, por haberme apoyado y alentado repetidas veces, pues gracias a ella encontré las fuerzas necesarias para llegar hasta el final. Y, por supuesto, gracias por todo el amor con el que me rodeas, del cual espero disfrutar toda mi vida.

Finalmente, mis más profundo y sentido agradecimiento a mi familia, que con amorosa paciencia, y entregándome su incondicional ayuda, también me han apoyado en esta etapa de mi vida, soportando la distancia que nos separaba. Mi madre Yolanda, mi padre Antonio, mi hermana Yurena, y mi abuela Tata, a pesar de la distancia siempre pude sentir su cariño. Les quiero mucho.

## Abstract

The evolution of processors has been supported by both the rapid technology advance and smart architecture designs. Until recently, processors mainly focused on exploiting instruction-level parallelism (ILP) to improve the performance. Nevertheless, the combination of the practical limits to superscalar processor implementations, the theoretical limits of instruction-level parallelism, and the increment of power constraints has forced different changes in processor designs. In this sense, the computer architecture community turns to new research towards other forms of parallelism.

Fruit of this trend, thread-level parallelism (TLP) has become a common strategy for improving processor performance. Simultaneous Multithreading (SMT) is one of these new paradigms to exploit TLP in recent years. The main feature of SMT processors is to simultaneously execute multiple threads to increase the utilization of the pipeline by sharing many more resources than in other types of processors. However, the memory wall problem is still present in these processors. Memory-intensive threads tend to use processor and memory resources poorly creating resource contention problems. This kind of threads can clog up shared resources due to long-latency memory operations without making progress on a SMT processor, thereby hindering the overall system performance.

In this dissertation, we target these problems with a two-fold objective: to improve the performance of these multithreading processors and to propose techniques to be as efficient as possible inside the current power constraints. To cover these goals, this dissertation firstly proposes Runahead Threads (RaT) to alleviate the memory wall problem, and secondly, provides additional techniques to improve the efficiency of our initial proposal.

## Contents

| 1 Introduction |                  | oducti  | on                                                                                               | 1  |  |

|----------------|------------------|---------|--------------------------------------------------------------------------------------------------|----|--|

|                | 1.1              | Multit  | hreaded models                                                                                   | 2  |  |

|                |                  | 1.1.1   | Simultaneous Multithreaded Processors                                                            | 4  |  |

|                |                  | 1.1.2   | SMT trends                                                                                       | 5  |  |

|                | 1.2              | Thesis  | overview                                                                                         | 6  |  |

|                |                  | 1.2.1   | The motivation: SMT problems                                                                     | 6  |  |

|                |                  | 1.2.2   | The approach: Runahead Threads                                                                   | 9  |  |

|                | 1.3              | Thesis  | contributions                                                                                    | 11 |  |

|                | 1.4              | List of | publications                                                                                     | 13 |  |

|                | 1.5              | Thesis  | organization                                                                                     | 14 |  |

| <b>2</b>       | Eva              | luatior | n Framework                                                                                      | 15 |  |

|                | 2.1              | Simula  | ation tools                                                                                      | 15 |  |

|                |                  | 2.1.1   | SMTSIM                                                                                           | 15 |  |

|                |                  | 2.1.2   | Power tools                                                                                      | 20 |  |

|                |                  |         | Wattch $\ldots$ | 20 |  |

|                |                  |         | CACTI                                                                                            | 21 |  |

|                | 2.2              | Bench   | marks                                                                                            | 22 |  |

|                | 2.3              | Evalua  | ation methodology and metrics                                                                    | 25 |  |

|                |                  | 2.3.1   | Performance metrics                                                                              | 25 |  |

|                |                  | 2.3.2   | Power and efficiency metrics                                                                     | 26 |  |

| 3              | Runahead Threads |         |                                                                                                  |    |  |

|                | 3.1              | The id  | lea of Runahead Threads                                                                          | 30 |  |

|                | 3.2              | Funda   | mentals of Runahead Threads                                                                      | 32 |  |

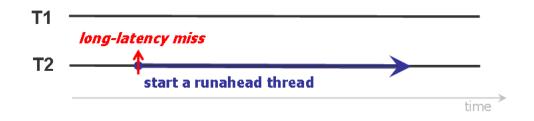

|                |                  | 3.2.1   | Starting a runahead thread                                                                       | 33 |  |

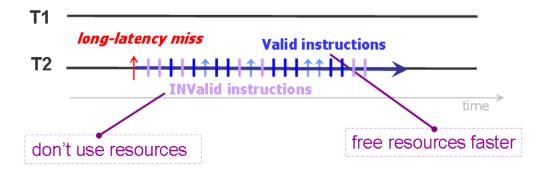

|                |                  | 3.2.2   | Executing a runahead thread                                                                      | 34 |  |

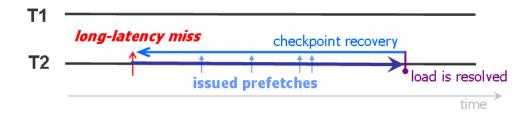

|     | 3.2.3                          | Exiting runahead thread                                                                                 | 36 |

|-----|--------------------------------|---------------------------------------------------------------------------------------------------------|----|

| 3.3 | Imple                          | mentation of Runahead Threads                                                                           | 36 |

|     | 3.3.1                          | Implementation issues for starting a runahead thread $\ . \ . \ .$ .                                    | 37 |

|     | 3.3.2                          | Implementation issues for runahead thread execution $\ldots$ .                                          | 38 |

|     |                                | Register validation control                                                                             | 38 |

|     |                                | Load and store management                                                                               | 39 |

|     |                                | Floating-point resources                                                                                | 40 |

|     |                                | Synchronization                                                                                         | 40 |

|     | 3.3.3                          | Implementation issues for exiting from a runahead thread                                                | 41 |

|     | 3.3.4                          | Overall hardware cost and complexity                                                                    | 41 |

| 3.4 | Evaluation of Runahead Threads |                                                                                                         |    |

|     | 3.4.1                          | Performance of Runahead Threads                                                                         | 43 |

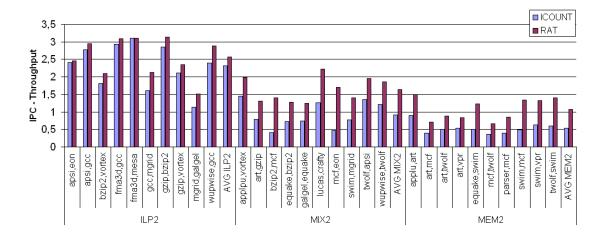

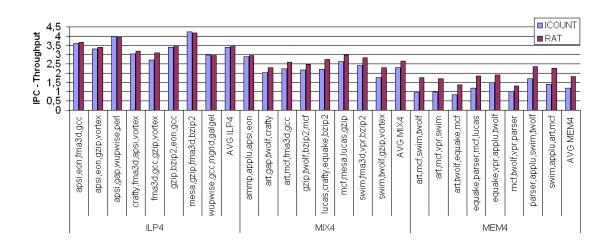

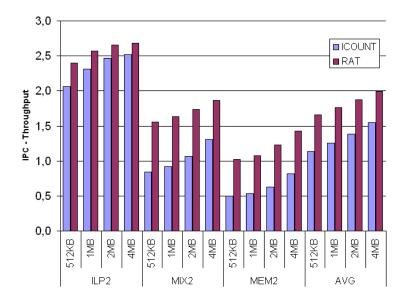

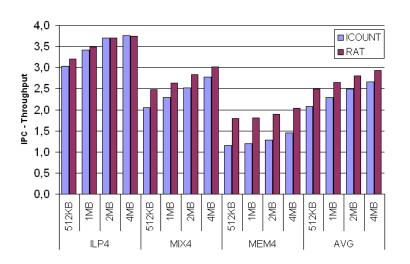

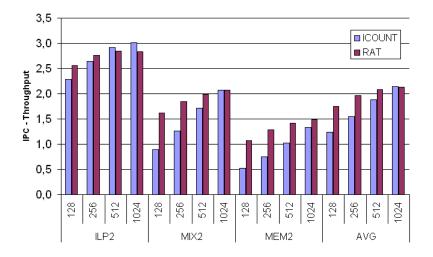

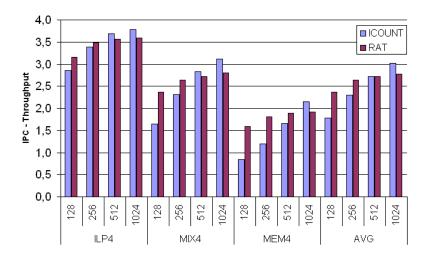

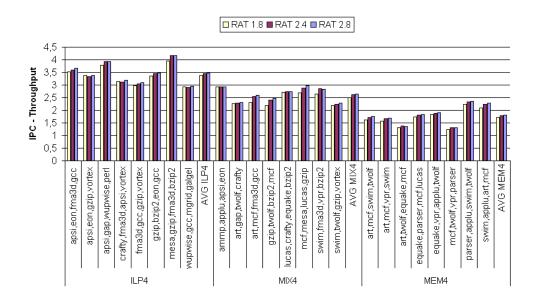

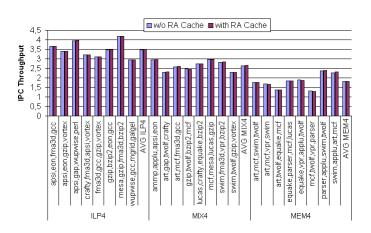

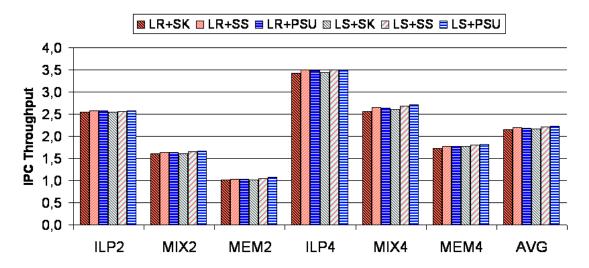

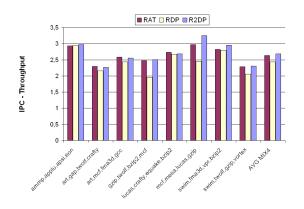

|     |                                | Throughput                                                                                              | 43 |

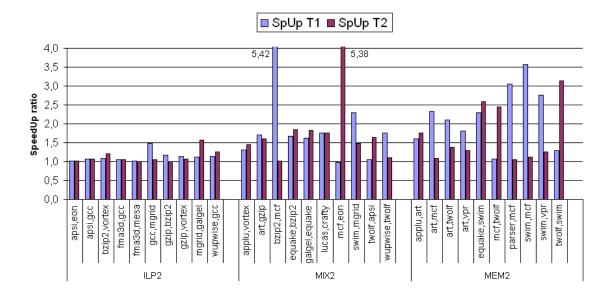

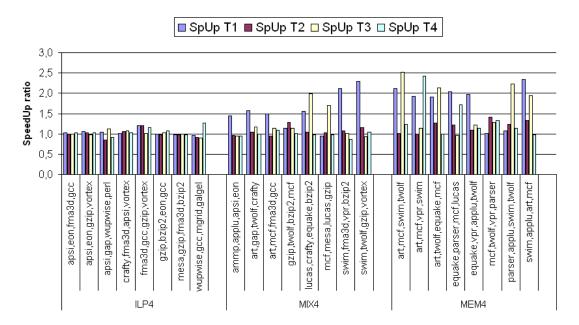

|     |                                | Per-thread SpeedUp                                                                                      | 45 |

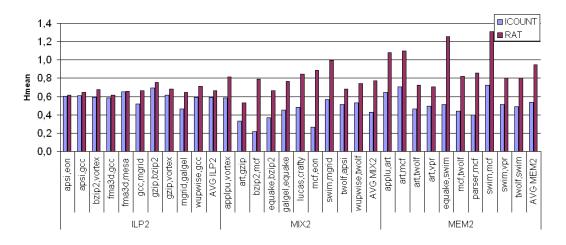

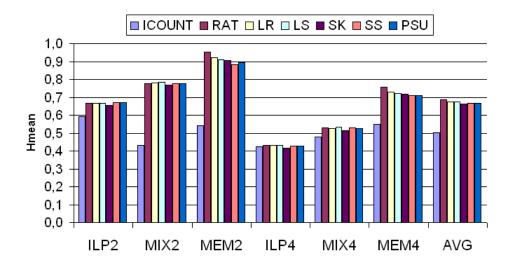

|     |                                | Hmean $\ldots$         | 47 |

|     | 3.4.2                          | Benefits and limitations of Runahead Threads $\ . \ . \ . \ .$ .                                        | 48 |

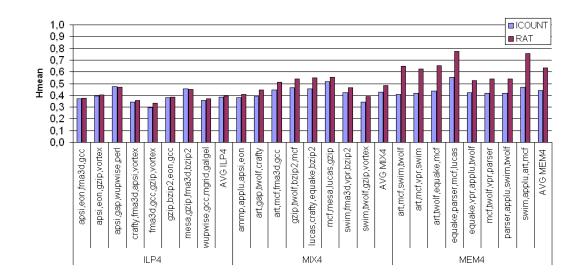

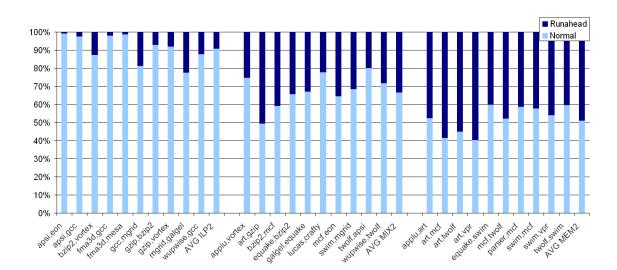

|     |                                | Prefetching                                                                                             | 48 |

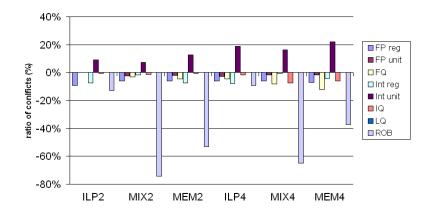

|     |                                | Resource contention                                                                                     | 50 |

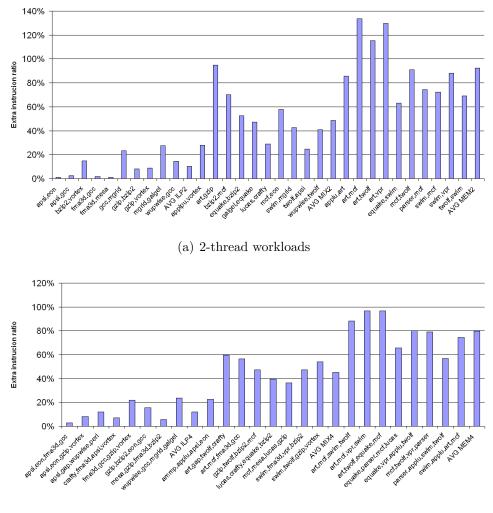

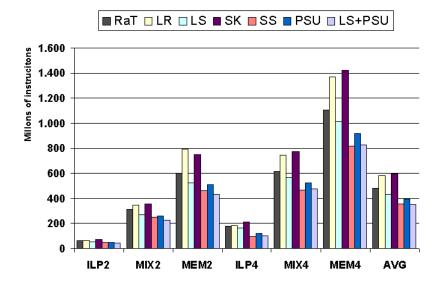

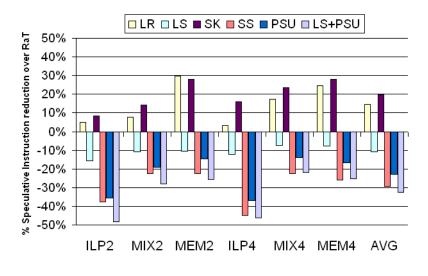

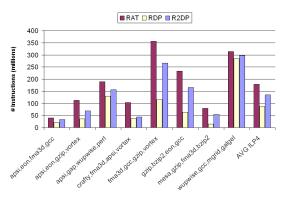

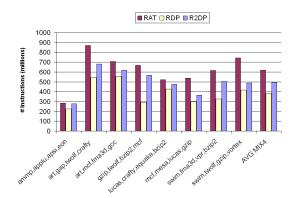

|     |                                | Instruction overhead                                                                                    | 51 |

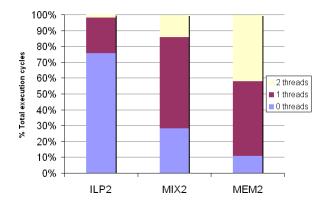

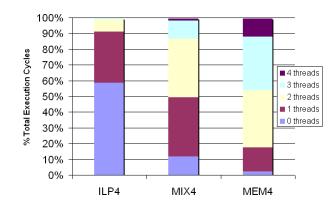

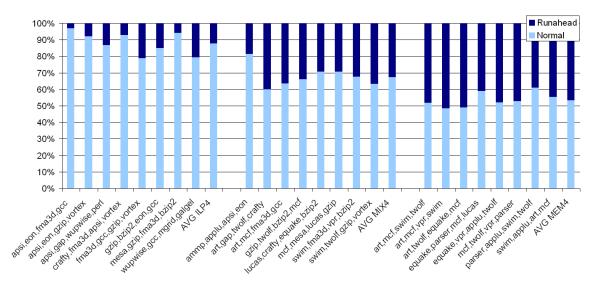

|     | 3.4.3                          | Life time of runahead threads $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$            | 53 |

| 3.5 | Sensit                         | ivity of Runahead Threads to processor parameters                                                       | 55 |

|     | 3.5.1                          | Hardware contexts                                                                                       | 56 |

|     | 3.5.2                          | Memory latency                                                                                          | 58 |

|     | 3.5.3                          | L2 cache size $\ldots$ | 60 |

|     | 3.5.4                          | Reorder buffer size                                                                                     | 61 |

|     | 3.5.5                          | Shared vs. non-shared ROB                                                                               | 64 |

|     | 3.5.6                          | Register file size                                                                                      | 65 |

| 3.6 | Design                         | a analysis for Runahead Threads implementation                                                          | 68 |

|     | 3.6.1                          | Fetch policy setup                                                                                      | 68 |

|     | 3.6.2                          | Different thread priority schemes for Runahead Threads $\ldots$ .                                       | 70 |

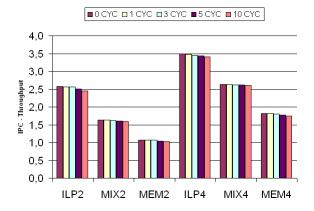

|     | 3.6.3                          | Checkpointing delay                                                                                     | 73 |

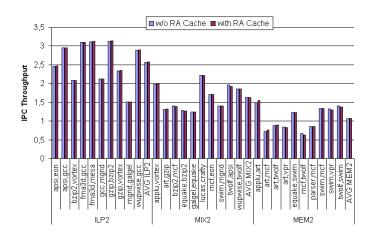

|     | 3.6.4                          | Use of the runahead cache $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$       | 74 |

| 3.7 | Summ                           | nary                                                                                                    | 76 |

| 4        | Coo | de Sem     | antic-Aware Runahead Threads                                                                            | <b>79</b> |

|----------|-----|------------|---------------------------------------------------------------------------------------------------------|-----------|

|          | 4.1 | Efficie    | ency and Runahead Threads                                                                               | 80        |

|          | 4.2 | Overs      | eeing program structures to improve RaT efficiency                                                      | 82        |

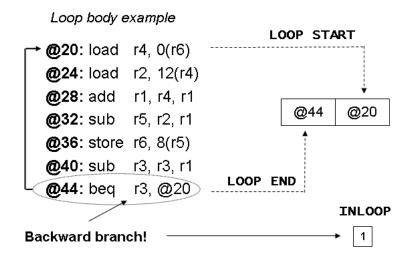

|          | 4.3 | Loop       | control techniques                                                                                      | 83        |

|          | 4.4 | Subro      | utine control techniques                                                                                | 89        |

|          | 4.5 | Loops      | and subroutines analysis $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 97        |

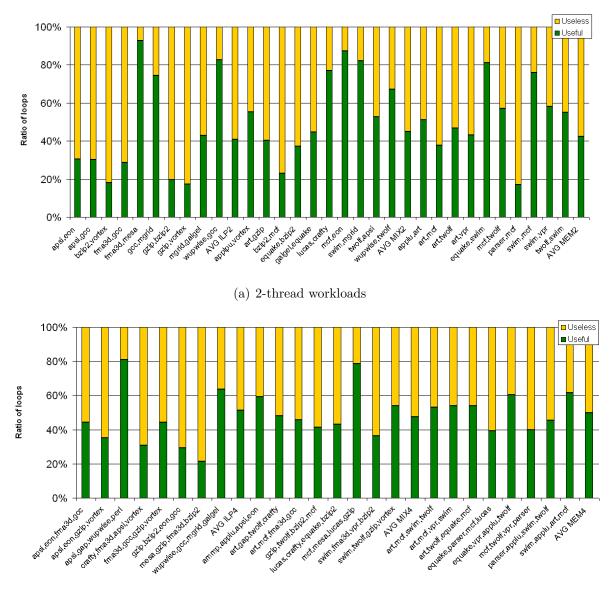

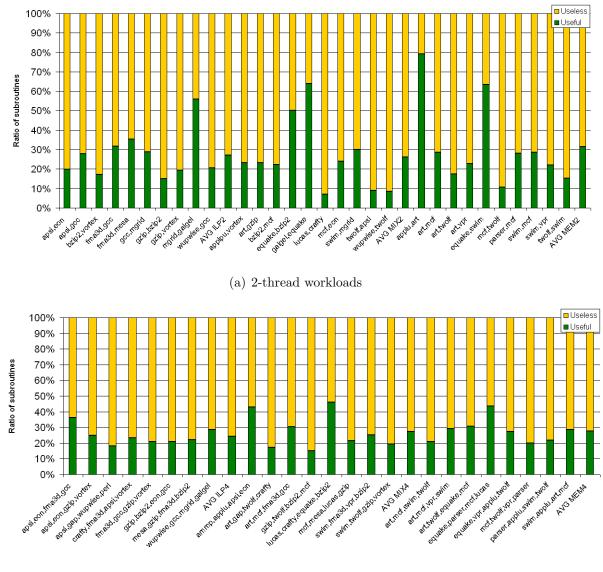

|          |     | 4.5.1      | Loops in runahead threads                                                                               | 97        |

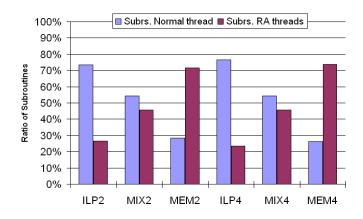

|          |     | 4.5.2      | Subroutines in runahead threads                                                                         | 100       |

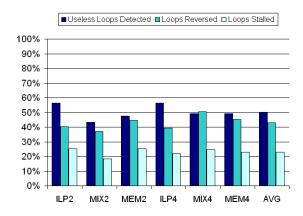

|          |     | 4.5.3      | Statistics about the controlled loops and subroutines $\ . \ . \ .$ .                                   | 101       |

|          | 4.6 | Evalu      | ation of code semantic techniques                                                                       | 103       |

|          |     | 4.6.1      | Impact of using the saturated counters $\ldots \ldots \ldots \ldots \ldots$                             | 104       |

|          |     | 4.6.2      | Performance evaluation                                                                                  | 105       |

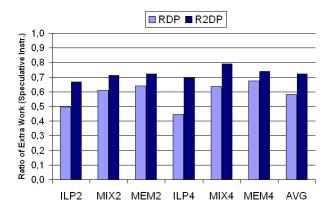

|          |     | 4.6.3      | Extra work                                                                                              | 107       |

|          |     |            | Speculative instructions                                                                                | 108       |

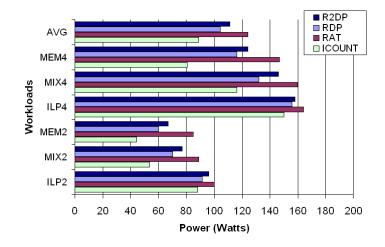

|          |     |            | Power consumption                                                                                       | 108       |

|          | 4.7 | Summ       | nary                                                                                                    | 110       |

| ۲        | Бæ  | - <b>!</b> | among Damahaad Thuas da                                                                                 | 110       |

| <b>5</b> |     | · ·        | -aware Runahead Threads                                                                                 | 113       |

|          | 5.1 |            | head distance prediction                                                                                |           |

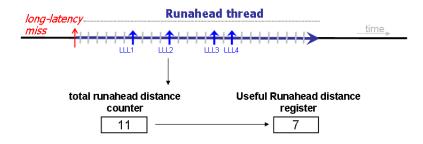

|          |     | 5.1.1      | Useful runahead distance                                                                                |           |

|          |     | 5.1.2      | The first approach                                                                                      |           |

|          |     | 5.1.3      | The second approach                                                                                     |           |

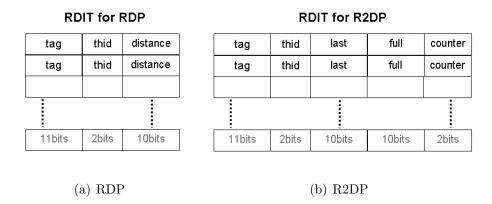

|          | -   | 5.1.4      | Implementation issues related to runahead distance techniques .                                         |           |

|          | 5.2 |            | ation of runahead distance mechanisms                                                                   |           |

|          |     | 5.2.1      | Analysis of refinements applied to R2DP technique                                                       |           |

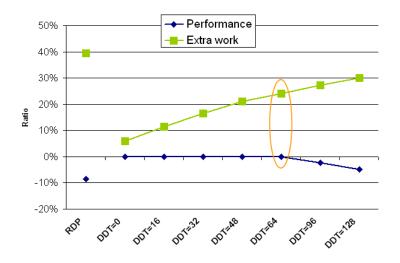

|          |     |            | Distance difference threshold                                                                           | 125       |

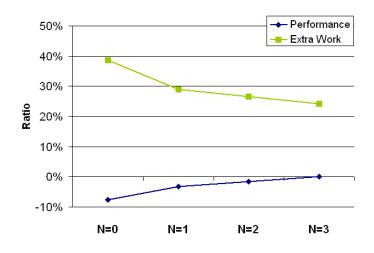

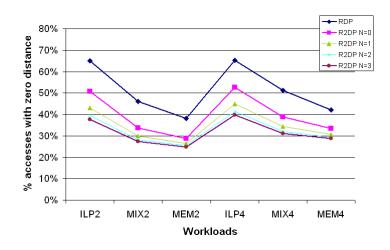

|          |     |            | Control heuristic to manage the distances with zero value                                               | 126       |

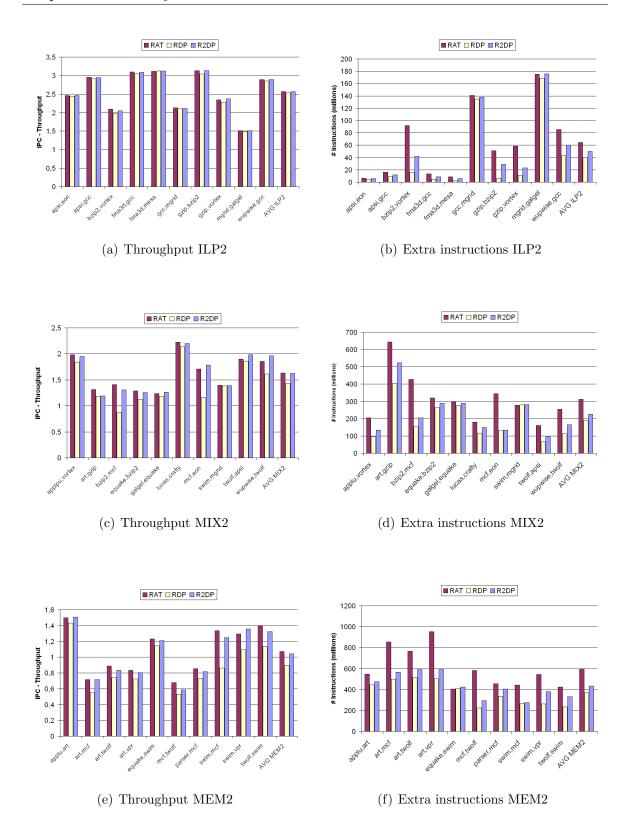

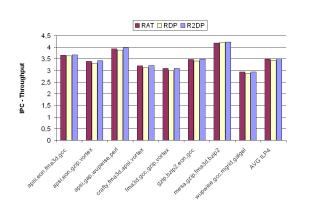

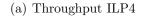

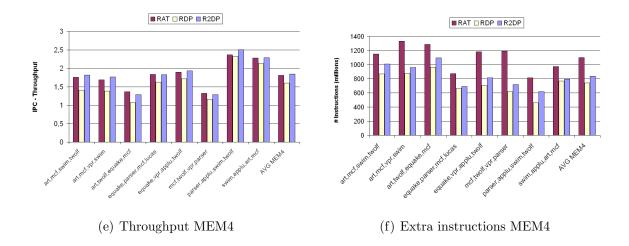

|          |     | 5.2.2      | Performance and extra work evaluation                                                                   | 128       |

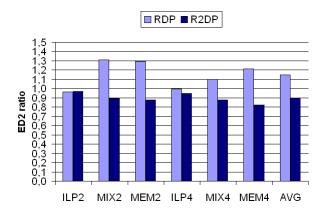

|          |     | 5.2.3      | Energy efficiency                                                                                       | 131       |

|          |     | 5.2.4      | Evaluation of dynamic adaptivity of runahead distance                                                   | 134       |

|          | 5.3 | Analy      | sis of the approaches                                                                                   | 136       |

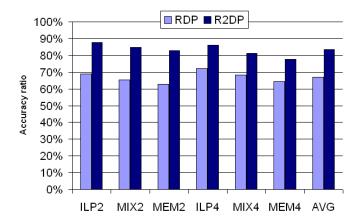

|          |     | 5.3.1      | Runahead distance prediction accuracy                                                                   | 136       |

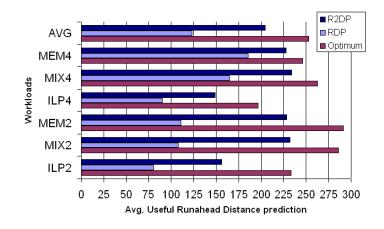

|          |     | 5.3.2      | Predicted useful runahead distance                                                                      | 137       |

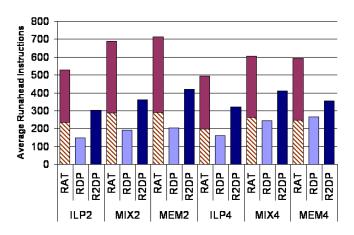

|          |     | 5.3.3      | Length of runahead threads                                                                              | 138       |

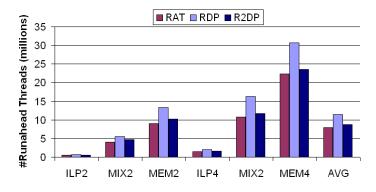

|               |                    | 5.3.4    | Number of runahead threads                  | 140 |

|---------------|--------------------|----------|---------------------------------------------|-----|

|               |                    | 5.3.5    | Distribution of controlled runahead threads | 140 |

|               | 5.4                | Summa    | ary                                         | 143 |

| 6             | Rel                | ated W   | <b>Tork</b>                                 | 145 |

|               | 6.1                | Simult   | aneous Multithreading                       | 145 |

|               |                    | 6.1.1    | Instruction fetch policies                  | 146 |

|               |                    | 6.1.2    | Dynamic resource allocation techniques      | 148 |

|               |                    | 6.1.3    | MLP-aware policies                          | 150 |

|               | 6.2                | Runah    | ead paradigm                                | 151 |

|               | 6.3                | Thread   | l-based speculative techniques              | 153 |

| 7             | Ove                | erall Me | echanism Comparison                         | 157 |

|               | 7.1                | State-o  | of-the-art SMT mechanisms                   | 157 |

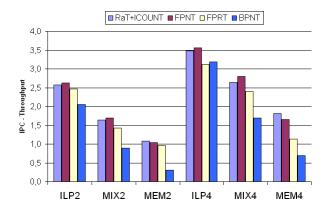

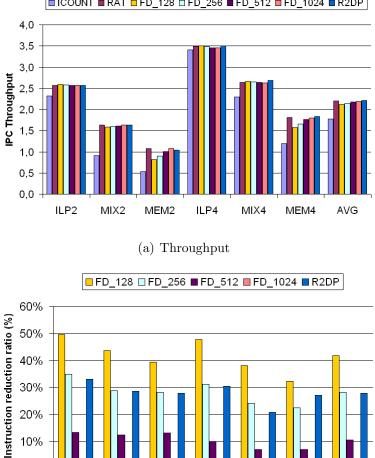

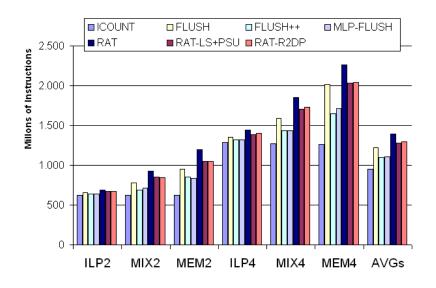

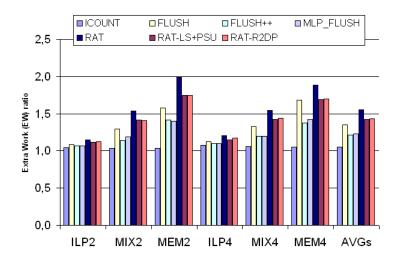

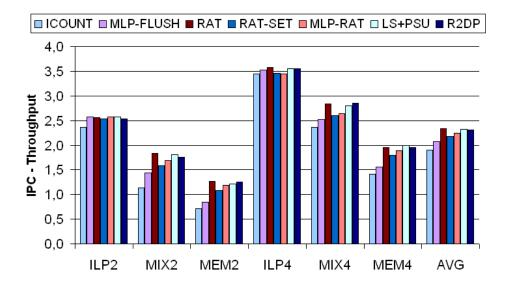

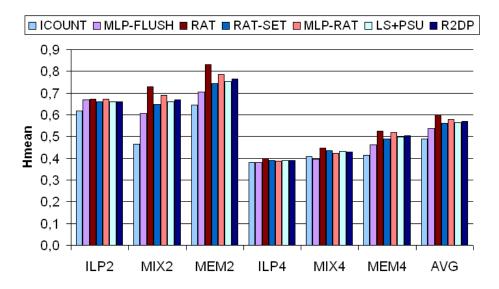

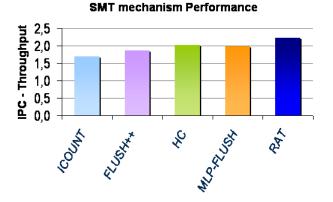

|               |                    | 7.1.1    | Performance evaluation                      | 158 |

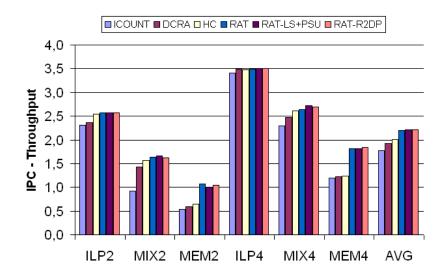

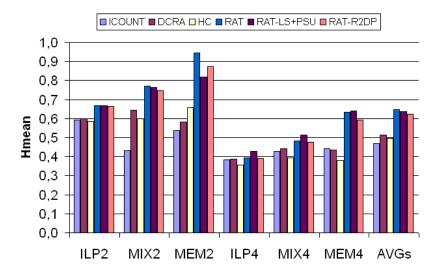

|               |                    |          | I-fetch policies                            | 158 |

|               |                    |          | Dynamic allocation techniques               | 160 |

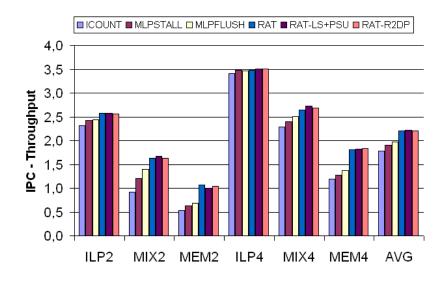

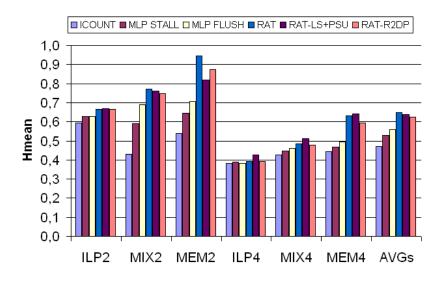

|               |                    |          | MLP-aware policies                          | 162 |

|               |                    | 7.1.2    | Extra instruction execution                 | 164 |

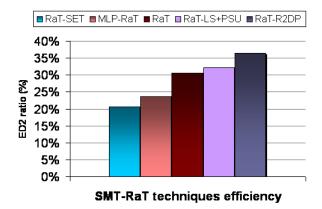

|               | 7.2                | Efficier | nt runahead thread techniques               | 167 |

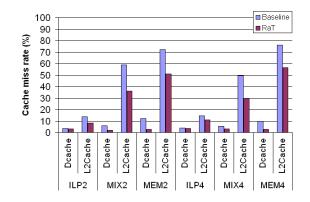

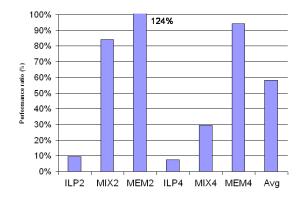

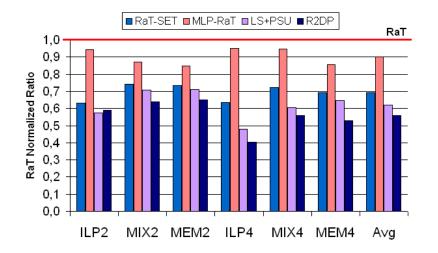

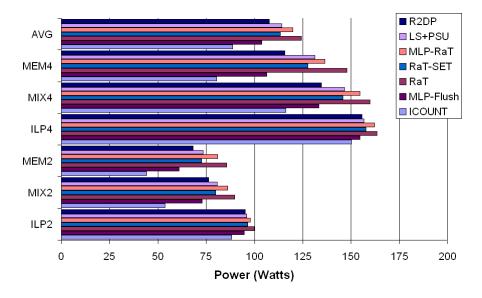

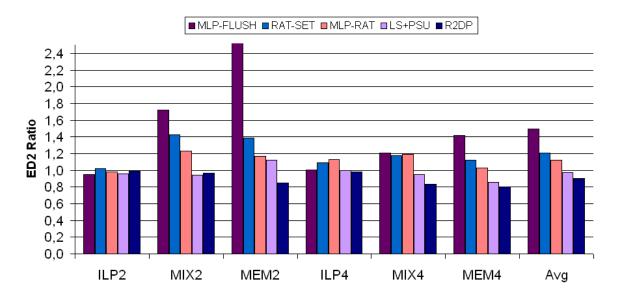

|               |                    | 7.2.1    | Performance                                 | 168 |

|               |                    | 7.2.2    | Energy efficiency                           | 170 |

|               | 7.3                | Summa    | ary                                         | 174 |

| 8             | Cor                | clusion  | IS                                          | 177 |

|               | 8.1                | Goals a  | and conclusions                             | 177 |

|               | 8.2                | Remar    | ks and future directions                    | 181 |

| $\mathbf{Li}$ | st of              | figures  | 3                                           | 187 |

| $\mathbf{Li}$ | List of tables 189 |          |                                             |     |

| R             | References 19      |          |                                             |     |

## Chapter

### Introduction

The incredible progress of computer development up to high-performance modern processors has come both from advances in technology and from innovation in computer design. Computer architecture and processor manufacturing have been able to provide faster processor designs by the available technology. For decades, the shrinking of transistors continuing to follow Moore's law [48] has allowed computer architects to improve processor performance by exploiting bit-level parallelism, instruction-level parallelism and memory hierarchies.

However, several factors have steered computer architects away from continuing to design increasingly more powerful single-thread processors in the last decade. The combination of the non-scalability of conventional out-of-order processors, limited instruction parallelism and power constraints has forced changes in processor designs. As a result, processor architects have focused their efforts on finding new alternatives to effectively utilize the millions of transistors available to improve performance in ways that minimize both design complexity and additional power usage.

In this scenario, *Multithreading* paradigm has become popular to deal with the above problems. Since it is difficult to extract more instruction-level parallelism (ILP) from a single program, architects have opted to execute multiple programs by exposing thread-level parallelism (TLP). Unlike ILP, which exploits implicit parallel instructions within a executed program, TLP is explicitly represented in a higher level of parallelism by the use of multiple threads of execution. The motivation to exploit TLP comes from the idea of using this parallelism among threads as another source to

find independent instructions when insufficient ILP exists. Therefore, processors with multithreading capabilities exploit the concurrency of multiple tasks to optimize the processor's performance by running a larger number of threads.

Since multithreaded processors have rapidly become a common strategy for improving processor performance, the research on this trend plays an important role in future processor designs. This thesis takes a step in the direction of improving the performance of Simultaneous multithreaded processors, one of the promising implementation models of multithreading.

#### 1.1 Multithreaded models

Multithreaded architectures are driven by the realization that single-threaded superscalar processors spend a surprising amount of time doing nothing. On the one hand, conventional processors have many execution units, and a single thread rarely uses all of them at once. On the other hand, when a thread stalls because it needs data that is not stored in the cache, the CPU ends up waiting for memory for hundreds of cycles. In both of these cases, having another thread immediately ready to run can fill up these empty spaces, and can prevent wasting resources.

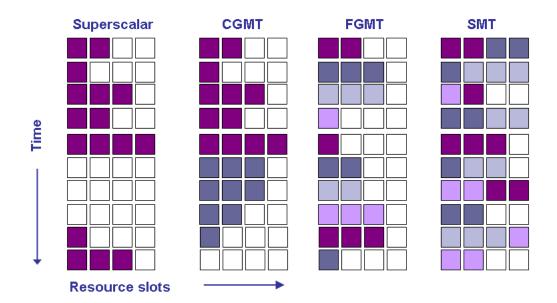

Hence, several multithreaded models are proposed to make better use of processor resources by executing several threads. Figure 1.1 depicts the different approaches of multithreaded models in function of the strategy to share the expensive execution resources on the processor core. In this figure, we represent that the processor either finds an instruction to execute (filled box) or the corresponding resource slot is unused in that clock cycle (empty box). Each color represents a different thread in execution. From the processor view, a *thread* represents a hardware context of execution with its own instructions and data.

• In a *superscalar architecture*, without multithreading support, only one thread is running at a given time. The lack of ILP limits the ability to issue more instructions per cycle. Superscalar processors often have more functional unit parallelism available than a single thread can effectively use. In addition, a longlatency event (such as a main memory access) can leave the entire processor idle.

- Figure 1.1: Different approaches of multithreaded processor. The horizontal dimension represents the execution resources used in each clock cycle. The vertical dimension represents a sequence of clock cycles.

- In a *coarse-grain multithreaded* (CGMT) processor, threads share all execution resources but instructions are issued from a single thread in each cycle. A CGMT processor switches to a different thread when a thread experiences a long-latency event, for example an off-chip cache misses. This allows the processors to hide part of the latency of long-latency operations by switching to another thread. Although this reduces the number of idle clock cycles, the ILP limitations still lead to idle resource slots within each cycle. Furthermore, CGMT processors suffer from the pipeline start-up period of threads each time there is a thread switching.

- In the *Fine-grain multithreading* (FGMT) case, the processor interleaves the execution of multiple threads switching them in alternate cycles. The main difference between coarse-grain and fine-grain multithreading is the granularity at which context switches occur. In a FGMT processor context switches are often done on every clock cycle (round-robin fashion), skipping any threads that are stalled at that time. The primary disadvantage is that it slows down the execution of the individual threads, since a thread that is ready to execute without stalls will be delayed by instructions from other threads. Besides, ILP limitations

still lead to idle slots within individual clock cycles because only one thread issues instructions in a given clock cycle.

• Simultaneous Multithreaded (SMT) processors eliminate context switching between multiple threads by allowing instructions from multiple simultaneously active threads to occupy processor's execution slots. SMT processors fetch instructions from different independent threads, and mix them in the processor pipeline reducing the number of idle slots. As a result, an SMT processor not only can switch to a different thread to use the idle issue cycles in a long-latency operation, but also fill unused issue slots in a given cycle with other threads (really exploiting the TLP). The drawbacks come from the imbalances in the resource needs and resource availability over multiple threads.

Although this figure greatly simplifies the real operation of these processors, it does illustrate the different potential performance advantages of multithreading.

#### 1.1.1 Simultaneous Multithreaded Processors

In particular, Simultaneous Multithreading [76][84] is one of the most promising implementations for the exploitation of TLP. An SMT processor allows dynamically varying the interleaving of instructions from multiple threads across shared execution resources. Therefore, SMT processors are able to exploit TLP as well as ILP by filling the pipeline with instructions fetched from multiple threads.

The key premise behind the simultaneous multithreading is that single thread multiple-issue processors already have many of the hardware mechanisms needed to support this multithread approach. SMT processors inherit from superscalar ones the ability to issue multiple instructions each cycle and the hardware support to execute out-of-order from multiple threads. More precisely, superscalar processors have a physical register file that can be used to hold the register sets of independent threads, though it has to deal with larger register files to hold multiple contexts. In addition, register renaming provides unique register identifiers, so instructions from multiple threads can be mixed in the data path without confusing sources and destinations across the threads (assuming separate renaming tables are kept for each thread). Furthermore, multiple instructions from independent threads can be issued without regard to the dependencies among them since the resolution of their dependencies can be handled by the dynamic scheduling capability. These observations enable straightforward implementations of SMTs on top of an out-of-order processor by basically adding a per-thread renaming table, keeping separate program counters (PCs), and providing the capability for instructions from multiple threads to commit (per-thread retirement).

SMT processors combine the multithreading technique with a wide-issue out-oforder processor to overcome the under utilization of a conventional superscalar processor. Multiple instructions from different threads are mixed within pipeline stages, allowing the extensive resources within these pipe stages in a superscalar processor to be more fully utilized. Thus, SMT achieves better performance throughput than singlethreaded superscalar processors for multithreaded (or multiprogramming) workloads, improving the overall efficiency.

#### 1.1.2 SMT trends

Simultaneous multithreading has already had impact in both the academic and commercial communities. Thus, different forms of SMT processors have been presented as research proposals [76][84] and many others have been adopted in real systems. Compaq proposed the Alpha EV8 21464 [25] that consists on a four-threaded eightissue SMT processor. In this thesis, we take this known design as the base for the SMT model. Multithreading is also mentioned as processor technique for the architecture projects of the Sun UltraSPARC family [39], starting from UltraSPARC IV [66]. *Hyper-Threading* [45], the Intel's brand name for Simultaneous Multithreading, is conceptually similar to the SMT proposals in which some portions of the Pentium 4 pipeline are multithreaded in a partitioned fine-grained fashion. For instance, the Intel Pentium 4 Xeon processor family [38] incorporates this hybrid form of multithreading that enables two logical processors to share some of the execution resources of the processors.

Likewise, as transistor dimensions continue to shrink thanks to process technology, another architectural approach for achieving TLP is represented by Chip Multiprocessors (CMPs) [52]. CMPs support the execution of more than one thread per processor chip by replicating an entire processor core for each thread. Both SMT and CMP architectures lead to orthogonal implementations also known as Chip Multithreading (CMT), having multiple cores able to execute several threads in one chip. In this sense, mixed designs and commercial processors with multithreaded and chip multiprocessors have appeared. For example, the Intel Core architectures [32] and Sun UltraSPARC T-series also know as Niagara processors. UltraSPARC T1 [67] in 2006 and next Ultra-SPARC T2 [68] in 2008 are both multicore and multithreaded processors, with up to eight CPU cores, each one able to concurrently handle four or eight threads respectively. There are others current commercial examples, such as the dual-core IBM POWER5 [36] and the succeeding POWER6 [26], processors with support for simultaneous multi-threading with two threads per core. Nowadays, new simultaneous multithreaded and chip multicore processors have been announced or are already in production by Intel, AMD, IBM and Sun.

#### 1.2 Thesis overview

#### 1.2.1 The motivation: SMT problems

SMT is going to become more important as this type of technology is making its way into CPU designs by all the major processor manufacturers. Therefore, many future processors will continue implementing some form of SMT since constitute an actual solution to improve the performance/cost ratio of processors. SMT designs exploit the thread-level parallelism by sharing hardware resources among multiple threads. However, the ability to get more performance (exploiting both instruction level parallelism and thread level parallelism) in these multithreaded processors also runs into two key related problems: the memory wall problem and the resource monopolization.

SMT processors can tolerate better the main memory latencies while running a multiprogrammed or multithreaded workload. Long latencies occurring in the execution of single threads are bridged by issuing operations of the remaining threads loaded on the processor. However, SMT processors still suffer from the memory wall problem [83] because long memory latencies continue having importance due to their impact on performance in the execution of a single-thread and in the overall SMT processor performance.

On the one hand, because of the growing memory access latencies (measured in processor cycles), any request from a thread that misses in the caches may eventually take hundred of cycles to satisfy. For example, commercial applications such as transaction processing workloads see 65% processor idle times, and high-performance scientific computations see 95% processor idle times: much of this is due to memory

latencies [47]. Thus, the execution of a thread continues being dominated by memory latencies.

On the other hand, this memory wall creates another critical side problem in the SMT framework: threads with intensive streams of memory accesses (memory-intensive threads) can create important resource contention in SMT processors [74]. As each thread has access to as many hardware resources as it needs, the features of memory intensive threads can unbalance the resource allocation holding more resources than others. A thread with a long-latency load pending will not make forward progress because following instructions can neither issue nor commit while waiting for the memory operation. This causes the thread to hoard a lot of critical resources due to all these pending instructions in the pipeline. As consequence of this situation, the shared resources are clogged, thereby starving other threads of required resources and preventing their forward progress as well. This effect would likely lead to a resource monopolization by a single thread and significantly degrading the performance of the other threads in the processor.

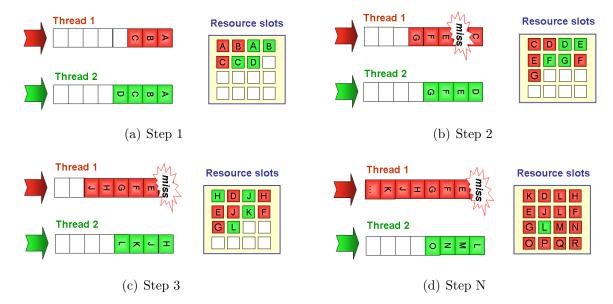

Figure 1.2 illustrates this important problem. This figure depicts two different threads executing their corresponding instructions in different steps. These instructions require certain resource slots which are taken from a resource pool. This resource pool represents whatever shared resource of the processor such as the issue queues, physical registers or reorder buffer. During this multithreaded execution, the thread 1 suffers from a long-latency miss (see 1.2(b)). From this point onwards, the subsequent instructions that already have resources allocated can not commit for this thread. Furthermore, the new introduced dependent instructions also allocate more resources slots. This effect causes the thread 1 to strangle the execution of the thread 2 monopolizing the resources slots (as the 1.2(d) shows) until the long-latency miss is solved.

To handle this long latency problem, different fetch and resource dynamic policies have been proposed to control the use of resources by memory-intensive threads (see Chapter 6). These techniques identify those threads that suffer from long-latency loads, and limit their use of machine resources by stalling or flushing these threads under determined conditions to prevent resource overuse. In these approaches, memoryintensive threads are usually restricted in order to get higher global throughput. Although these policies alleviate the memory-intensive thread monopolization, the performance of fast threads is not reduced at the cost of stalling the execution of memoryintensive threads.

Figure 1.2: Effects of long-latency misses on SMT processors

In addition, these existing techniques do not assume memory intensive threads exhibit other kind of parallelism as is the memory-level parallelism (MLP) [31]. Consequently, these policies are harmful for memory-intensive applications because threads are stopped before they can exploit the available MLP, failing to reach the potential performance achievable. Therefore, significant potential exists to improve the performance of the SMT processors by improving their tolerance to long main memory latencies with regard to memory intensive threads.

Several large instruction window approaches [1][18][19][41][46][65] have been proposed to maintain a high number of instructions in the pipeline to exploit the ILP and MLP as much as possible. The idea of building a large instruction window is worthy of research since these proposals have shown significant single-thread performance. However, they suppose challenges in their implementations due to the design complexity, verification process, and increase in the energy consumption of single-thread processors. For instance, the proposed solutions still require very large buffers, hierarchical structures and non-trivial control logic in the processor core. Hence, these alternatives maybe are even more complex and difficult to implement in multithreaded processors, in which some of large and complex structures to support large instruction windows should be shared and replicated as well. Therefore, large-instruction windows are promising in the single-thread processors, but in the multithreaded scenario, where current trends point towards simpler cores, they are less suitable. Finally, as power consumption has already become a limiting constraint in the design of high-performance processors, simple power and efficient proposed techniques are especially desirable.

#### **1.2.2** The approach: Runahead Threads

The main purpose of this dissertation is to resolve the problems related with the memory wall on SMT processors with a two-fold objective: to improve the performance and to propose efficient techniques inside the current power constraints. To cover all these goals, this dissertation first proposes introducing and evaluating the mechanism of Runahead Threads (RaT) to alleviate the memory wall problem and improve SMT performance, and second, providing additional techniques to improve the power-efficiency of our initial proposal.

Before beginning this work, previous techniques tend to distribute resources to threads that infrequently miss in the caches, i.e. which are compute-intensive. By contrast, we target our approach to improve the performance impact of memory-intensive threads in SMT machines without penalizing the other thread performance. At the same time, we want to provide the latency tolerance provided by a large instruction window without having to design and implement structures to support a large number of in-flight instructions. To accomplish this, we extend the Runahead paradigm for SMT processors by *Runahead Threads* (RaT). Runahead [23][51] is an execution scheme that generates accurate data prefetches by speculatively executing instructions past a long latency cache miss, when the processor would otherwise be stalled. Runahead consists of avoiding the blockage of the instruction window due to long-latency operations, *e.g.* a load that misses in the last level cache. Instead, the processor continues executing instructions speculatively, trying to follow the most likely program path until the load that triggered the runahead mode is resolved.

Through Runahead Threads (RaT), we alleviate the problems related to longlatency loads in SMT processors. First, runahead threads do not clog up resources (and thus they do not starve other threads) on long-latency load misses. A runahead thread allocates and deallocates shared processor resources quickly instead of holding on to them until the long-latency load completes. This allows other threads to make use of the available shared resources. Second, runahead threads exploit further MLP going beyond the processor's instruction window. The main novelty of this alternative proposal regarding previous SMT techniques is that the memory-intensive threads advance speculatively, instead of being stalled. On the one hand, RaT improves the memory latency tolerance of each individual thread by exploiting the memory-level parallelism available. Each runahead thread does useful processing to improve their performance through prefetching. This provides benefits on a single-threaded application, which is not provided by multithreading. On the other hand, our mechanism also avoids memory-intensive threads clogging up shared resources, transforming them into light speculative threads and allowing all threads to continue executing with the shared resources. Other important advantage is that it is required small changes in the hardware to support RaT in the SMT processor. Thus, RaT mechanism does not require significant hardware cost or complexity.

However, these benefits of RaT come at the cost of executing a large number of instructions speculatively. If runahead thread execution does not provide prefetching benefits, it can result in degrading efficiency by executing a large number of useless instructions. To avoid this problem, this thesis also presents several contributions aimed not only at improving the performance of SMT processors, but also to increase the efficiency of Runahead Threads. In this dissertation, we propose and evaluate different techniques to control runahead thread executions in order to make RaT a more efficient mechanism.

The next proposals are focused on studying how to enhance the effectiveness of RaT. We focus on reducing the speculative work done by runahead threads as much as possible, without degrading their performance benefits. On the one hand, we present a kind of proposals base on analyzing the prefetch opportunities (usefulness) of executed code structures, such loop and subroutines, during the runahead thread executions. These techniques dynamically use some semantic information to detect these particular program structures and to analyze when they are useful or not in order to control the runahead thread execution. By means of this dynamic information, the proposed techniques make a control decision either to avoid or to stall the particular loop or subroutine execution in runahead threads. These decisions make RaT reduce the useless work executed in common program structures and the most important thing, improving its efficiency.

On the other hand, we proposed another novel technique to improve the efficiency of the initial RaT mechanism reducing the number of instructions executed by controlled runahead threads. We introduce a new mechanism which is guided by the useful runahead distance, a new concept that indicates how far a thread should run ahead such that speculative runahead execution is useful. Based on the useful distance prediction, our technique makes two actions. First, it predicts whether or not a thread should start runahead execution, (i.e. whether or not runahead execution is useful) to avoid the execution of useless runahead periods. Second, it indicates how long the thread should execute in runahead mode to reduce unnecessary extra work done by useful runahead periods. Limiting the runahead distance of a thread not only avoids unnecessary speculative execution but also allows more shared resources to be efficiently used by non-speculative threads. As result of this proposal, we significantly reduce power consumption of RaT, providing better performance and energy balance than previous proposals in the field.

#### **1.3** Thesis contributions

The contributions of this thesis are summarized in the following main points:

- The mechanism of Runahead Threads. The contribution of Runahead Threads is a different mechanism to overcome the memory wall problem on SMT processors. Although we have been inspired by previous Runahead paradigm, we introduce and evaluate for the first time Runahead Threads for multithreaded scenarios.

- By Runahead Threads, we greatly improve the overall performance of SMT processors exploiting ILP, TLP and MLP. We show that with RaT it is possible to improve the performance of single-thread by the runahead prefetching effect and to avoid the resource monopolization of memory-intensive threads. This contribution represents a completely different approach to tackle the problem of handling long-latency loads on SMT processor.

- Runahead Threads are deeply evaluated. Aside from its different benefits to alleviate the commented SMT problems, we demonstrate that RaT can benefit from smaller register file with even performance improvements. This may allow SMT designs with less expensive hardware. We also show the major drawback of runahead threads. In case there is no prefetching to be performed, the runahead threads execute useless speculative instructions resulting in lower efficiency. To solve this shortcoming, several alternatives for improving the RaT efficiency are proposed with a different point of view.

- Code semantic-aware runahead threads. This contribution consists on a code semantic-aware set of techniques to improve RaT efficiency. These techniques perform coarse-grain analysis based on code semantics to oversee the prefetching usefulness of loops and subroutines during runahead executions. In function of this analysis, the processor makes different actions to control the runahead threads. While these alternatives are targeted to particular code patterns, these show good relation between instruction reduction and performance.

- The Runahead Distance Prediction approach. This proposal enhance the efficiency of RaT based on the new concept of useful runahead distance. The useful runahead distance represents the maximum MLP achievable by a particular runahead thread while at the same time reducing the extra useless speculative work. We propose two different generic mechanisms that perform a fine-grain analysis of each runahead thread to collect that useful runahead distance. The novelty is that we predict how long the thread should execute in runahead mode to be efficient. We show as our mechanism is able to eliminate more useless speculative instructions (even in useful runahead periods) that cannot be eliminated by previous techniques. Furthermore, we achieve reducing the power consumption while maintaining the overall SMT performance with RaT.

- Finally, we provide a quantitative survey of RaT mechanisms from this dissertation and the state-of-the-art related techniques. We show that RaT approaches provide significant performance outperforming state-of-the-art techniques. As additional contribution, we provide experiments to compare these related proposals including novel power and energy efficiency results not considered in prior work. We present the first evaluation (to the best of our knowledge) that give power and energy measurements in the Runahead paradigm.

#### 1.4 List of publications

Here, we compile and list all of the publications arise from the research and contributions of this dissertation:

- Tanausú Ramírez, Alex Pajuelo, Oliverio J. Santana and Mateo Valero. Kiloinstruction Processors, Runahead and Prefetching. In ACM conference on Computing Frontiers (CF'06), pages 269-278. May 2006, Ischia, Italy.

- Tanausú Ramírez, Alex Pajuelo, Oliverio J. Santana and Mateo Valero. A First Glance at Runahead Threads. In HiPEAC Advanced Computer Architecture and Compilation for Embedded Systems (ACACES'07), pages 107-110. July 18th, 2007, L'Aquila, Italy.

- Tanausú Ramírez, Oliverio J. Santana, Alex Pajuelo and Mateo Valero. Runahead Threads: Reducing Resource Contention in SMT Processors. In IEEE-ACM Conference, Parallel Architectures and Compilation Techniques (PACT'07), page 423. September 15-19, 2007, Brasov, Romania.

- Tanausú Ramírez, Alex Pajuelo, Oliverio J. Santana y Mateo Valero. Introducing Runahead Threads for SMT Processors. In XVIII Jornadas de Paralelismo (JP'07) held in conjunction with CEDI 2007, pages 35-42. 11-14 September, 2007. Zaragoza, Spain.

- Tanausú Ramírez, Alex Pajuelo, Oliverio J. Santana, and Mateo Valero. Runahead Threads to Improve SMT Performance. In IEEE High-Performance Computer Architecture Conference, (HPCA'08), pages 149-158. February 18-20, 2008, Salt Lake City, USA.

- Tanausú Ramírez, Alex Pajuelo, Oliverio J. Santana, and Mateo Valero. Code Semantic-Aware Runahead Threads. In IEEE 38th International Conference on Parallel Processing, (ICPP'09), pages 437-444. 22-25 September 2009 Vienna, Austria.

- Tanausú Ramírez, Alex Pajuelo, Oliverio J. Santana, Onur Mutlu and Mateo Valero. *Efficient Runahead Threads*. Submitted to 24th ACM/SIGARCH International Conference on Supercomputing (ICS'10). June 2010 Tsukuba, Japan.

#### 1.5 Thesis organization

The structure of this dissertation is as follows:

Chapter 2 is devoted to explain our experimental framework. This includes the simulation tools, the benchmarks, and metrics used in this thesis.

Chapter 3 introduces the mechanism of Runahead Threads, describing its functionality and details for the implementation on SMT processors. We evaluate and analyze in detail different design trade-offs for RaT in the multithreaded environment.

Chapter 4 describes the inefficiency problem of RaT and shows our first proposals to improve the RaT efficiency. We present code-semantic aware techniques that control the extra work on runahead thread executions. We show how by dynamically analyzing the code of programs, we can improve the RaT efficiency performing different actions during runahead threads.

Chapter 5 presents the second of our proposals focused on improving the RaT efficiency. This other approach is based on the concept of useful runahead distance for making RaT more efficient. Based on the runahead distance prediction in order to reduce the speculative instructions, different mechanisms decide when and how long a runahead thread is executed.

Chapter 6 describes prior work that help to understand the scenario of this thesis.

Chapter 7 provides a detailed mechanism comparison exploring all the state-of-theart SMT techniques as well as results achieved with a deep evaluation between them and our performance and efficient RaT proposals.

Chapter 8 provides conclusions, a summary of the key results, and insights presented in this dissertation. We also propose some directions for future work.

# Chapter **2**

## **Evaluation Framework**

This chapter describes the simulation tools, benchmarks and the methodology that make up the experimental framework of this thesis. Based on this evaluation framework, we evaluate the different proposals, obtain the experiment results and provide the conclusions presented in this dissertation.

#### 2.1 Simulation tools

Computer architects use different simulation tools in which they model their novel ideas and evaluate the simulation results to measure their benefits and potential. To perform the different evaluations of this thesis, we employ a generic SMT processor simulator in conjunction with other complementary tools. They are described in the following sections.

#### 2.1.1 SMTSIM

Our simulation environment is based on a simulator derived from SMTSIM [73]. SMT-SIM is an execution-driven simulator which models generic Simultaneous Multithreaded processors and provides high flexibility. This simulator is able to run unmodified Alpha object code (we will describe our benchmarks later in Section 2.2).

We modify SMTSIM to support simulation checkpoints. A simulation checkpoint allows us to store the simulator execution state maintaining the execution-driven feature while reducing the simulation time considerably. In addition, we improve the memory hierarchy modeling bus, port and bank contention, bandwidth, and main memory timings accurately.

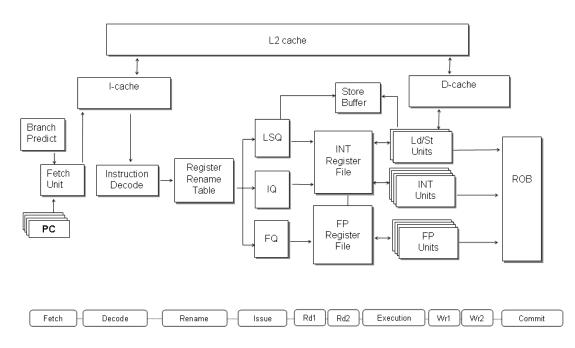

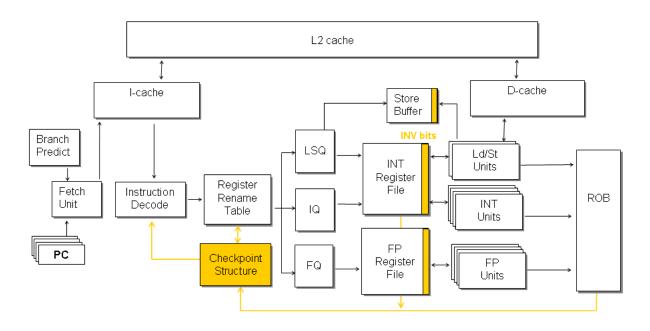

In order to evaluate all the contributions, the different designs of our mechanisms, as well as other fetch and resource scheduling techniques for comparison purposes, are built on top of this simulator. A scheme of the simulator processor model is depicted in Figure 2.1 in which the pipeline and main hardware components of this baseline architecture are shown.

Figure 2.1: Block diagram of SMT processor architecture

The larger multiported SMT register file requires a longer access time. An actual solution to avoid increasing the processor cycle time and to maintain the processor frequency is to extend register access across the pipe stages. So, we consider to extend the stages in which the register file is accessed (both read and write operations) with the corresponding additional bypasses. Now, read and write stages take two cycles each one. As result, this SMT architecture is composed of ten stages as it is shown in Figure 2.1. For instance, the pipeline of Intel Core micro-architecture is 14 stages long [82].

The processor fetches instructions from the instruction cache in program order. We use an underlying baseline fetch policy which determines from which of the available threads instructions are fetched. We choose ICOUNT (2,8) policy [75] which in each cycle, it selects two different threads (according to a fetch priority) and fetches up to eight instructions from each thread. By previous analysis [75], the ICOUNT (2,8) scheme performs 10% better than fetching from one thread at a time (1,8) and 5% better than fetching four instructions from each of two threads (2,4). We also perform an evaluation of the ICOUNT setup policy in Section 3.6 according to the new context of this dissertation. To support fetching from two different threads in each cycle, the instruction cache (Icache) is usually replicated to get several instruction blocks. In addition, both return address stack (RAS) and branch history register (BHR) need to be also replicated for each thread to avoid the interleaving of thread interferences in the branch predictions.

Next, instructions are decoded and renamed in order to track data dependencies. When an instruction is renamed, an entry is allocated in the corresponding issue queue (IQ) until all its operands are ready. Each instruction also allocates one entry in the reorder buffer (ROB) and a physical register for mapping a destination architectural register (if it is required). While the rename table can be partitioned across threads, all physical registers are viewed as a common pool in which SMT threads share the logic that manages them (port, free list, etc...). As soon as an instruction has all its operands ready, it is issued: it reads its operands, executes in the corresponding functional unit, and writes its results. Finally, that instruction is committed in program order.

The main configuration parameters of the simulated SMT processor architecture are summarized in Table 2.1. For this architectural model, we configure an eight-way superscalar organization in which up to four hardware contexts can be executed. A key factor for configuring the processor model is the resource organization. We define a resource configuration, taking into account which of resources are shared between threads and which are exclusive for each thread. In statically partitioned multithreaded designs, each context has a fixed pool or part of a resource assigned. This leads to a lack of flexibility away from the "simultaneous multithreaded" idea of sharing resources. Academic SMT models use dynamic resource sharing, which allows threads to allocate the different idle shared resources to improve the processor utilization. In our SMT model, we use a full resource sharing organization to benefit from the dynamic multithreaded advantages. Threads coexist in the different pipeline stages, sharing the following processor resources:

| Processor core          |                                            |  |

|-------------------------|--------------------------------------------|--|

| Processor depth         | 10 stages                                  |  |

| Fetch width             | 8 instructions (up to 2 threads per cycle) |  |

| Decode and commit width | 8 instructions                             |  |

| Reorder buffer          | shared ROB (64 entries per context)        |  |

| INT/FP registers        | 48 physical regs. per context              |  |

| INT/FP/LS issue queues  | 64 / 64 / 64 entries                       |  |

| Functional units        | 4 INT / 4 FP / 2 LdSt                      |  |

| Perceptron Branch       | Perceptron (256)                           |  |

| predictor               | $4096 \ge 14$ bit local and                |  |

|                         | 40 bit global history                      |  |

| RAS                     | 32 entries per context                     |  |

| Memory subsystem        |                                            |  |

| I-cache                 | 64 KB, 4-way, 1 cycle latency              |  |

| D-cache                 | 64 KB, 4-way, 3 cycles latency             |  |

| L2 Cache                | 1 MB, 8-way, 20 cycles latency             |  |

| Caches line size        | 64 bytes                                   |  |

| MSHRs                   | 16 per context                             |  |

| Main memory latency     | minimum of 300 cycles                      |  |

- Table 2.1: SMT processor baseline configuration. In all the experiments of this thesis,

these parameters remain unchanged except when explicitly stated otherwise.

- 1. Issue Queues (IQs): The processor considers every instruction (independently of the thread) equal from the execution point of view until they are committed. All threads insert their instructions in the corresponding IQ after the rename stage in function of the type of instruction. IQ are unified buffers that have generally high and somewhat unpredictable utilization.

- 2. Execution Units: All executions units are shared and fully pipelined. In the outof-order pipeline (back-end), instruction dependency chains determine execution resource utilization more than any arbitration schemes. This parameter is set by the number of available total functional units per cycle in our model.

- 3. Physical registers: the physical register file (RF) is shared by all contexts. There is a register file for integer operations and another for floating-point ones. The quantity of available physical registers for renaming is critical in a scenario with several hardware contexts with their own architectural registers. The latter depends on the particular instruction set architecture (ISA). For example, for an ISA with 32 architectural registers, 128 registers are needed to maintain the precise state for a 4-threaded SMT, per each integer and floating point RFs. Our architecture supports the Alpha ISA, so each hardware context can address 32 architectural integer registers and 32 architectural FP registers. The registerrenaming mechanism maps these architectural registers onto the different available physical registers for each context. The configuration of the register file size in our processor model is determined by the number of hardware contexts. We assume a contribution of 48 physical registers per context to the total RF pool available for register renaming. Hence, the architectural registers are renamed to a RF of 96 registers for a 2-context machine and 192 registers for a 4-context model.

- 4. Reorder Buffer: this structure keeps the program order of instructions. Using a separate ROB per thread would probably require less complexity in an actual hardware implementation, similar to replicate conventional superscalar ROBs. However, we choose a shared ROB design to analyze any possible critical resource contention with this important buffer. Sharing a ROB among multiple threads introduces additional complexity. This additional complexity mainly lies in selectively squashing the speculative instructions. Nevertheless, this procedure is already implemented in an SMT processor with a shared ROB to recover from branch mispredictions supporting selective flushing of nonconsecutive entries. For most of the experiments of this work, our simulated processor uses a shared ROB for all the hardware contexts. As for RF, each hardware context has a contribution to the total ROB size of 64 entries in this case. We will study the influence of the shared ROB in our architecture in Chapter 3 as well.

- 5. Caches (the instruction cache, the L1 data cache, and the unified L2 cache): The I-cache and D-cache are multiported and multibanked. Sharing cache access ports between threads to maximize their utilization is one of the objectives of an SMT design. Hence, all caches are shared between threads, and then, all their

memory space are common to all threads. Caches are tagged with the identifier of threads so that independent threads do not share data and/or instructions but they competes for cache space.

#### 2.1.2 Power tools

An important part of this work focuses on reducing the power consumption and improve the performance-energy efficiency of the proposed approaches. To perform these evaluations, we employ a power model based on Wattch [3]. In addition, caches (or similar structures) statistics such as delay or energy per access have been drawn from the CACTI tool [61].

#### Wattch

Wattch is an architecture-level power and performance simulator implemented on top of the Simplescalar[5]. Wattch uses activity counters during the simulation in order to estimate the energy consumption of the different processor components. We integrate the Wattch power model in our simulator implementation using an improved conditional clocking for scaling the power dissipation of multiport structures. We model the energy consumption for all the main hardware structures of the processor (functional units, register files, branch predictor, queues, ROB, memory system, etc), including also the clock power estimation. With this accurate power model, we will give data of power and energy as result of several studies and different mechanism evaluations. We extend the power model during this research to obtain the power dissipation of the modified and new structures added to the processor hardware.

Before running the simulation, Wattch calculates the basic energy of every processor component consumes when it is fully utilized. Different estimation formulas, which are taken from CACTI<sup>1</sup>, are used for each type of component. The main processor units that Wattch models fall into four categories:

1. Array Structures: Data and instruction caches, cache tag arrays, all register files, register alias table, branch predictors, the reorder buffer, and large portions of the issue queue and the load/store queue.

<sup>&</sup>lt;sup>1</sup>The original Wattch implementation uses an earlier version of Cacti whose code is built directly into the program. In our implementation, we run a separate and updated Cacti executable (version 4.2) and retrieve the data from it.

- 2. Fully Associative Content-Addressable Memories (CAM): Issue queue wakeup logic, load/store queue address checks, TLBs (if they are configured as fully-associative).

- 3. Combinational Logic and Wires: Functional units, issue queue selection logic, dependency check logic at decode stage, and result buses.

- 4. Clocking: Clock buffers, clock wires, and capacitive loads of the different structures.

During each cycle of the simulation, several counters keep track of the number of times each unit is accessed. Based on the number of accesses and the basic energy, the energy consumed during that cycle is calculated. For multi-port units, where only some of the ports are used, we implement an enhanced conditional clocking model. The power of these multiported units is scaled according to the number of ports used, with an unused port consuming 10% of the power a used port consumes (original Wattch uses the all-or-nothing approach).

Finally, the total energy consumed by the processor in function of each component is shown at the end of the simulation, along with the average power per cycle.

#### CACTI

CACTI is an independent tool which provides statistics such as timing, power and area model for cache memories. Although CACTI is theoretically modeled only for caches, we modify it to include also results for non-tagged similar structures (e.g. branch or data predictor tables). CACTI presents results in terms of area, energy consumption and delay broken down into the decoders, bitlines, wordlines, comparators, sense amplifiers, routing buses, output driver, etc.

Using CACTI, we estimate the access time for the cache configurations employed in our baseline. We also use this tool to estimate the energy of other structures and obtain additional information for our power consumption model, such as the number of bitline and wordline segments. This information is useful for Wattch to get the different hardware component features related to the energy.

#### 2.2 Benchmarks

To compose the experimental workloads, we use independent set of programs from the SPEC2000 benchmark suite [64]. SPEC benchmarks, developed from real user applications, are used to measure the performance of the processor, memory and compiler on the tested system. This set of applications includes a wide range of codes with different behaviors both for integer (Spec INT) and floating point programs (Spec FP). In this sense, the experiments in the thesis are performed with multiprogramming workloads created by combining single-thread programs using both the integer and the FP benchmarks from that SPEC suite. Using multithreaded workloads composed of independent applications is still a frequently used technique by computer architecture researchers. Although these workloads are composed of non-cooperative applications that perform non-related work and do not communicate each other, they emulate real system workloads to properly perform multithreaded evaluations. In spite of the increasing trend to use truly parallel applications, they are still less common in real machines. We consider that simulation methodologies for parallel applications are a really interesting topic for future research, but it is out of the scope of this work.

All benchmarks are compiled to obtain Alpha standard binaries on a DEC Alpha AXP-21264 running UNIX V4.0 OS and using Compaq C/C++ V6.2-034 and f77/f90 Compaq Fortran V5.3-915 compilers with the -O3 optimization level and non\_shared flag. For each benchmark, we select an interval of 300 million instructions representative of the entire program execution using the reference input set. To identify the most representative simulation point, we analyze the distribution of basic blocks using SimPoint[60] during benchmark executions. Table 2.2 presents the different SPEC benchmarks<sup>2</sup> with the reference input files used to run them, and the number of fast forwarded instructions for each benchmark. The last column shows the global memory miss rate for each program as well.

We characterize each program simulated in a single-threaded processor in order to classify the group of benchmarks and create the multiprogramming workloads. To make this classification, we use the IPC and the global cache miss rate. The IPC allows benchmarks to be classified into high-ILP and low-ILP according to their singlethreaded IPC. The global miss rate is calculated with respect to the number of misses

$<sup>^{2}</sup>$ We have not include two SPEC FP (sixtrack and facerec) due to syscall errors in order to generate their execution checkpoints.

|          | Benchmark   | input              | Fast-forward (Millions)                                                                                                                                                                                                                                                                | Global miss rate (%) |

|----------|-------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|          | 164.gzip    | graphic            | 68.100                                                                                                                                                                                                                                                                                 | 0,08                 |

|          | 175.vpr     | place              | 2.100                                                                                                                                                                                                                                                                                  | 1,12                 |

|          | 176.gcc     | 166.i              | 14.000                                                                                                                                                                                                                                                                                 | 0,07                 |

|          | 181.mcf     | inp.in             | 43.500                                                                                                                                                                                                                                                                                 | 14,97                |

| Е        | 186.crafty  | crafty.in          | 74.700                                                                                                                                                                                                                                                                                 | 0,02                 |

| Spec INT | 197.parser  | ref.in             | 83.100                                                                                                                                                                                                                                                                                 | 1,05                 |

| bec      | 252.eon     | cook               | 57.600                                                                                                                                                                                                                                                                                 | 0,01                 |

|          | 253.perlbmk | splitmail.535      | 68.100         2.100         14.000         43.500         74.700         83.100                                                                                                                                                                                                       | 0,03                 |

|          | 254.gap     | ref.in             | 79.800                                                                                                                                                                                                                                                                                 | 0,33                 |

|          | 255.vortex  | lendian1.raw       | 58.200                                                                                                                                                                                                                                                                                 | 0,11                 |

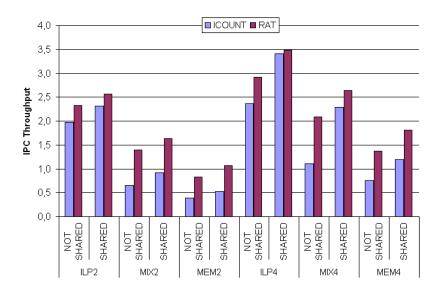

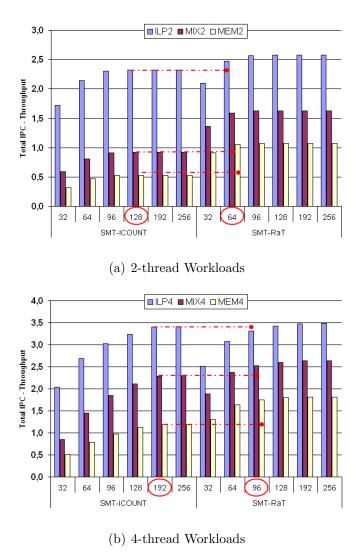

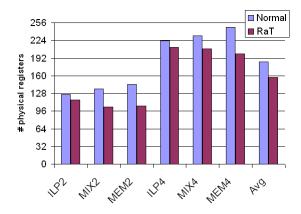

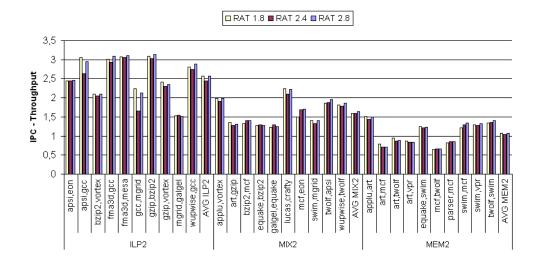

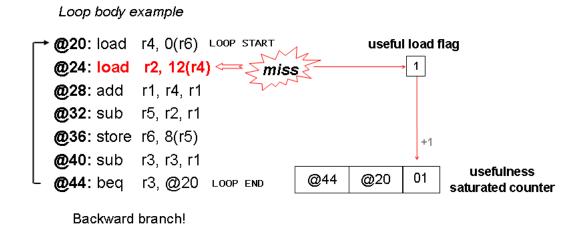

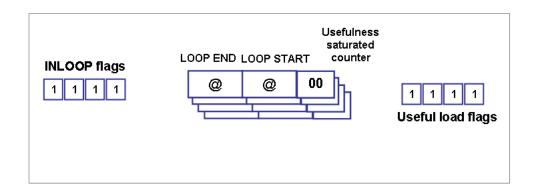

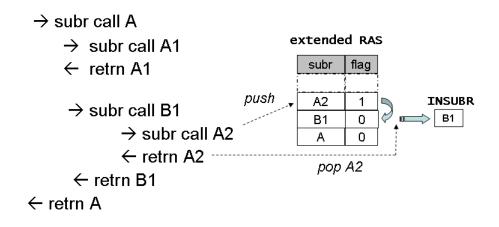

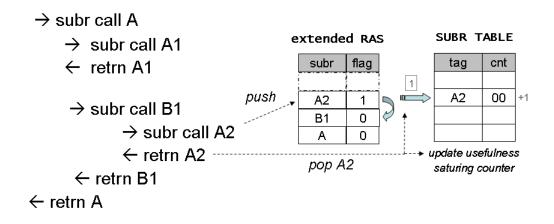

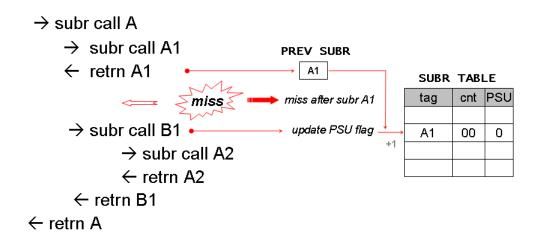

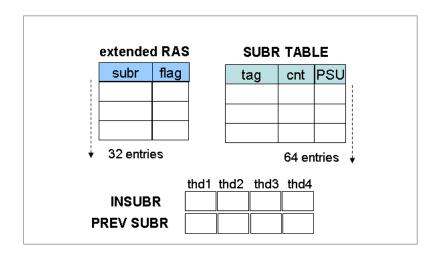

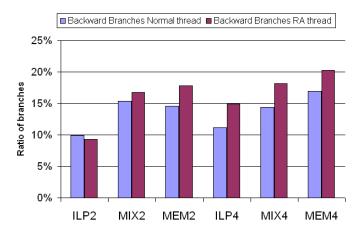

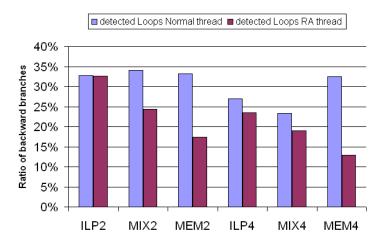

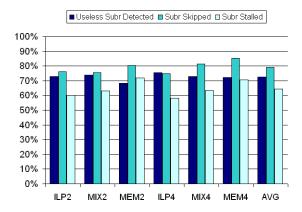

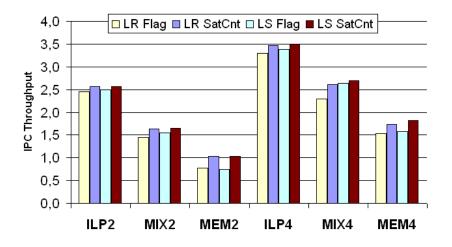

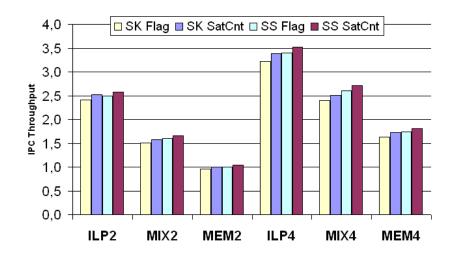

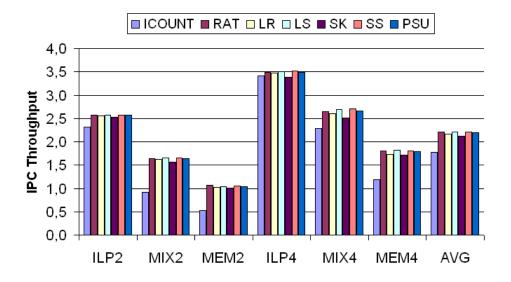

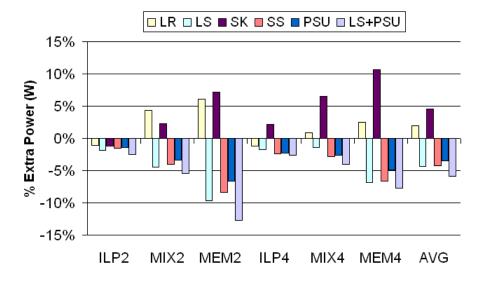

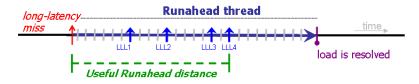

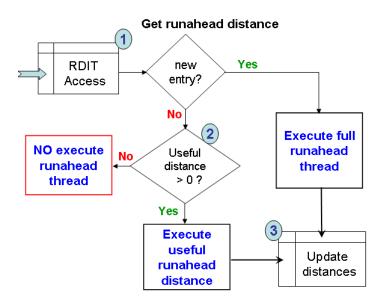

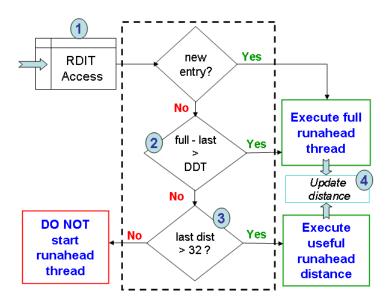

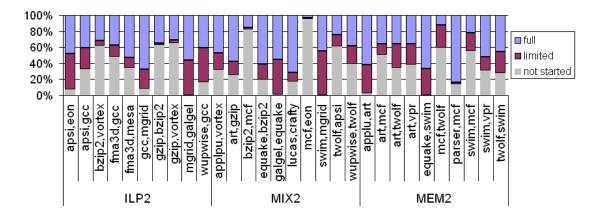

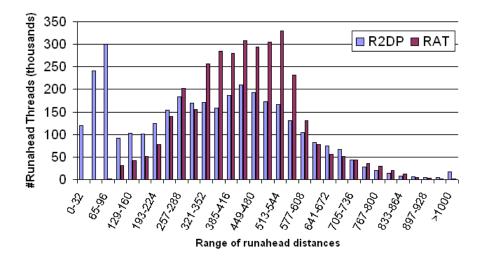

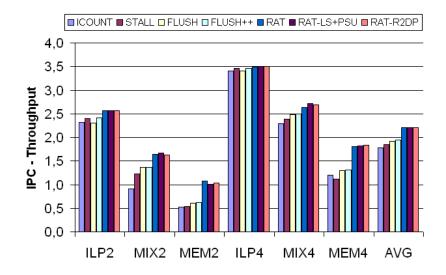

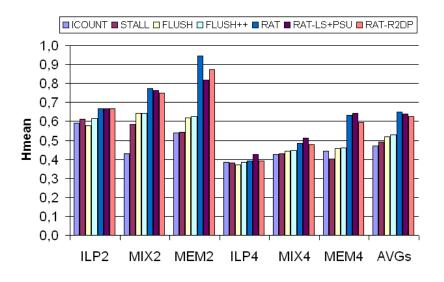

|          | 256.bzip2   | inp.program        | 13.500                                                                                                                                                                                                                                                                                 | 0,10                 |