# **Universitat** de les Illes Balears

# DOCTORAL THESIS 2022

# FORMAL ALGEBRAIC MODELLING FOR FOG COMPUTING NETWORK ARCHITECTURE

Pedro Juan Roig Roig

### Universitat de les Illes Balears

## DOCTORAL THESIS 2022

# Doctoral Programme in Information and Communications Technology

## FORMAL ALGEBRAIC MODELLING FOR FOG COMPUTING NETWORK ARCHITECTURE

### **Pedro Juan Roig Roig**

Thesis Supervisor: Dr. Carlos Juiz García

Thesis Supervisor: Dr. Salvador Alcaraz Carrasco

Thesis Tutor: Dr. Carlos Juiz García

**Doctor by the Universitat de les Illes Balears**

Dedicated to my parents

## Acknowledgments

I would like to thank my thesis supervisors Dr. Salvador Alcaraz, Dr. Katja Gilly and Dr. Carlos Juiz, as well as all those who supported me on my way to get here.

Thesis supervisor Author

#### Carlos Juiz and Salvador Alcaraz

Pedro Juan Roig Roig

#### Abstract

Fog computing is basically an extension of cloud computing where the computing resources are located on the edge of the network, allowing for better performance regarding latency and bandwidth. Hence, data centres (DC) being used in fog computing may be far smaller and so may the number of hosts and switches in use. In this context, the present thesis dissertation undertakes the modelling of some DC designs for fog computing, setting the focus on just simple network topologies, even though more complex ones might achieve better performance. Such topologies may be modelled in different ways, exposing the minimal path, or equal-cost multiple paths, through which a live Virtual Machine (VM) migration of computing assets may take place from a source to a destination host. This way, a user moving throughout a fog domain will have their computing assets following it as close as possible with a minimal time interval, which is the key point in Internet of Things (IoT) moving environments. It is to be stressed that the models are going to be exposed by following an analytical approach, with the combination of different mathematical branches to get the models ready, such as geometry and topology to obtain the appropriate designs, arithmetic to forward the moving assets to the proper destination, logic to implement those actions in flow charts and pseudocode, or algebra to exhibit a formal description of the whole model. The main contribution in this thesis dissertation goes about obtaining models of optimal paths for VM migrations in DC topologies related to fog computing deployments by means of an abstract process algebra called Algebra of Communicating Processes (ACP), which has been used in order to formally specify and verify such models, as it allows to reason about process terms on an analytical basis, getting back to basics regarding the information technology field. In summary, regarding each topology, different models may be proposed, such as by means of flow charts, pseudocode and a formal algebraic model, followed by the presentation of a formal algebraic model for a whole fog/cloud system.

viii Abstract

Directores de tesis Autor

Carlos Juiz and Salvador Alcaraz

Pedro Juan Roig Roig

#### Resumen

Fog computing es básicamente una extensión del cloud computing, donde los recursos de computación se encuentran en el borde de la red, lo cual permite un mejor rendimiento en cuanto a latencia y ancho de banda. Por lo tanto, los centros de datos (DC) que se utilizan en fog computing deben ser mucho más pequeños, así como el número de hosts y switches instalados. En este contexto, esta disertación de tesis aborda el modelado de algunos diseños de DC para fog computing, poniendo el foco solo en topologías de red simples, aunque otras más complejas puedan lograr mejor rendimiento. Dichas topologías pueden modelarse de diferentes maneras, exponiendo la ruta mínima, o rutas mínimas de igual costo, a través de las cuales se pueden llevar a cabo las migraciones de recursos entre un host origen y otro destino. De esta manera, un usuario moviéndose por un dominio fog tendrá sus recursos de computación asociados siguiéndole lo más cerca posible en un intervalo de tiempo mínimo, siendo éste el punto clave en los entornos de movilidad IoT. Se debe destacar que los modelos se van a exponer siguiendo un enfoque analítico, mediante la combinación de diferentes ramas matemáticas para preparar los modelos de la manera más directa, como la geometría y la topología para obtener los diseños adecuados, la aritmética para llevar a cabo el movimiento de los recursos de computación al destino adecuado, la lógica para implementar esas acciones en diagramas de flujo y pseudocódigo, o el álgebra para proporcionar una descripción formal de todo el modelo. La principal contribución en esta disertación de tesis consiste en obtener modelos de rutas óptimas para migraciones de VM en topologías de DC relacionadas con despliegues fog computing por medio de un álgebra de procesos abstracta denominada ACP, con la cual se han especificado y verificado formalmente dichos modelos, ya que permite razonar sobre términos de procesos de forma analítica, volviendo a los orígenes en el campo de las tecnologías de la información. En resumen, con respecto a cada topología, se proponen diferentes modelos, tales como diagramas de flujo, pseudocódigo y un modelo algebraico formal, para posteriormente presentar un modelo algebraico formal para un sistema completo de fog/cloud.

$\mathbf{x}$  Resum

Directors de tesi Autor

#### Carlos Juiz and Salvador Alcaraz

#### Pedro Juan Roig Roig

#### Resum

Fog computing és bàsicament una extensió del cloud computing, on els recursos de computació es troben al límit de la xarxa, la qual cosa permet un millor rendiment pel que fa a latència i ample de banda. Per tant, els centres de dades (DC) que s'utilitzen en fog computing han de ser molt més petits, així com el nombre de hosts i switches instal·lats. En aquest context, aquesta dissertació de tesi aborda el modelatge d'alguns dissenys de DC per fog computing, posant el focus només en topologies de xarxa simples, encara que altres més complexes puguin aconseguir millor rendiment. Aquestes topologies poden modelar-se de diferents maneres, exposant la ruta mínima, o rutes mínimes del mateix cost, a través de les quals poden tenir lloc les migracions de recursos entre un host origen i un altre destí. Així, un usuari movent-se per un domini fog tindrà els seus recursos de computació associats seguir-lo el més a prop possible amb un interval de temps mínim, que és el punt clau en els entorns de mobilitat IoT. S'ha de destacar que els models van a ésser exposats seguint un enfocament analític, mitjançant la combinació de diferents branques matemàtiques per preparar els models, com la geometria i la topologia per obtenir els dissenys adequats, l'aritmètica per dur a terme el moviment dels recursos de computació a la destinació adequada, la lògica per implementar aquestes accions en diagrames de flux i pseudocodi, o l'àlgebra per a proporcionar una descripció formal de tot el model. La principal contribució en aquesta dissertació de tesi es basa en obtenir models de rutes òptimes per a migracions de VM en topologies de DC relacionades amb desplegaments fog computing mitjantçant un àlgebra de processos abstracta anomenada ACP, amb la qual s'han especificat i verificat formalment aquests models, ja que permet raonar sobre termes de processos de forma analítica, tornant als orígens en el camp de les tecnologies de la informació. En resum, pel que respecta a cada topologia, es proposen diferents models, como ara diagrames de flux, pseudocodi i un model algebraic formal, per a posteriorment presentar un model algebraic formal per a un sistema complet de fog/cloud.

$ext{xii}$   $ext{Resum}$

## Contents

|   | Title | e Page                                                                  |

|---|-------|-------------------------------------------------------------------------|

|   | Ded   | ication                                                                 |

|   | Ack   | nowledgments                                                            |

|   | Abs   | ${ m tract}$                                                            |

|   | Resi  | umen                                                                    |

|   | Resu  | um                                                                      |

|   | List  | of Figures xix                                                          |

|   | List  | of Tables                                                               |

| 1 | Intr  | roduction 1                                                             |

|   | 1.1   | Context                                                                 |

|   | 1.2   | Objectives                                                              |

|   | 1.3   | Outline                                                                 |

| 2 | Mai   | in pillars and related work                                             |

|   | 2.1   | Computing, cloud and fog                                                |

|   |       | 2.1.1 Cloud and Fog computing                                           |

|   |       | 2.1.2 VM migration techniques                                           |

|   | 2.2   | Modelling with ACP                                                      |

|   |       | 2.2.1 Using FDT modelling in cloud/fog environments                     |

|   |       | 2.2.2 ACP modelling                                                     |

|   | 2.3   | Topologies for data centres                                             |

|   |       | 2.3.1 Network topologies                                                |

|   |       | 2.3.2 Redundant topologies proposed                                     |

|   | 2.4   | Summary                                                                 |

| 3 | Reg   | gular $N$ -polytopes, trees, graphs and tori applied to data centres 43 |

|   | 3.1   | N-dimensional geometry                                                  |

|   |       | 3.1.1 Platonic solids                                                   |

|   |       | 3.1.2 Schläfli notation                                                 |

|   |       | 3.1.3 Regular polygons                                                  |

|   |       | 3.1.4 Regular polyhedra                                                 |

xiv Contents

|   |     | 3.1.5  | Regular polychora                            |

|---|-----|--------|----------------------------------------------|

|   |     | 3.1.6  | Regular polytera                             |

|   |     | 3.1.7  | Regular $N$ -polytopes                       |

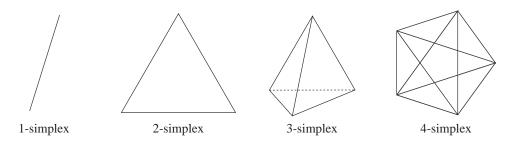

|   |     |        | 3.1.7.1 $N$ -simplex: $k$ -facets            |

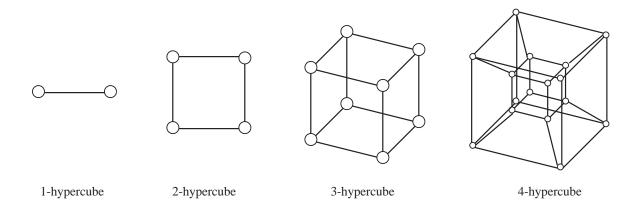

|   |     |        | 3.1.7.2 $N$ -hypercube: $k$ -facets 60       |

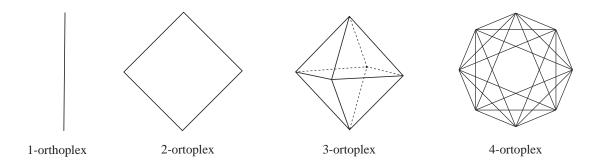

|   |     |        | 3.1.7.3 N-orthoplex: $k$ -facets 61          |

|   | 3.2 | Tree-l | ike data structures                          |

|   |     | 3.2.1  | Abstract data types                          |

|   |     | 3.2.2  | Vocabulary about trees                       |

|   |     | 3.2.3  | Structural induction                         |

|   |     | 3.2.4  | Binary trees                                 |

|   |     | 3.2.5  | <i>M</i> -ary trees                          |

|   | 3.3 | Graph  | n-like data structures                       |

|   |     | 3.3.1  | Seven bridges of Königsberg                  |

|   |     | 3.3.2  | Fundamentals on graphs                       |

|   |     | 3.3.3  | Eulerian and Hamiltonian graphs              |

|   |     | 3.3.4  | Geometrical graphs                           |

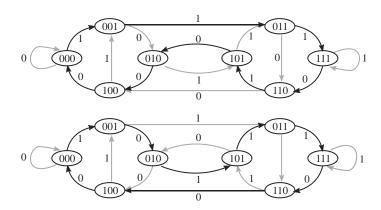

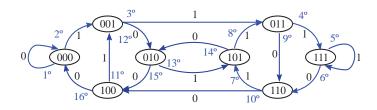

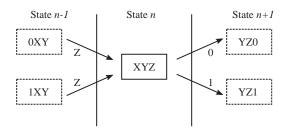

|   |     | 3.3.5  | De Bruijn graphs                             |

|   | 3.4 | Torus  | topologies                                   |

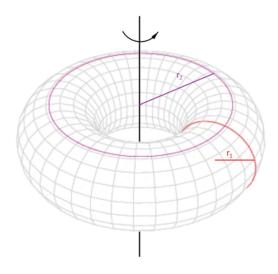

|   |     | 3.4.1  | Properties of a torus                        |

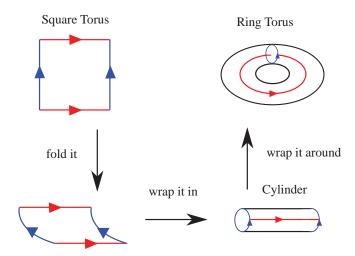

|   |     | 3.4.2  | Toroidal network designs                     |

|   |     | 3.4.3  | De Bruijn torus                              |

|   |     | 3.4.4  | De Bruijn hypertorus                         |

|   | 3.5 | Summ   | ary                                          |

| 4 | Con | nmon   | network topologies for Data Centres 97       |

|   | 4.1 |        | l mesh: tree-like designs                    |

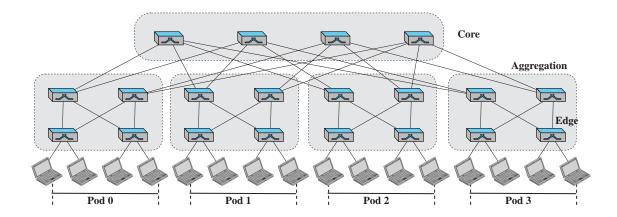

|   |     | 4.1.1  | Fat tree                                     |

|   |     | 4.1.2  | Leaf and spine                               |

|   | 4.2 | Partia | l mesh: graph-like designs                   |

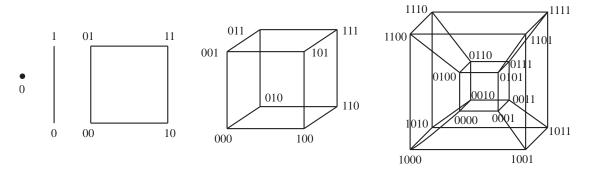

|   |     | 4.2.1  | <i>N</i> -hypercube                          |

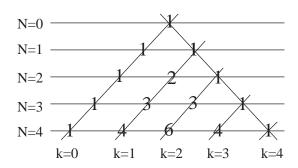

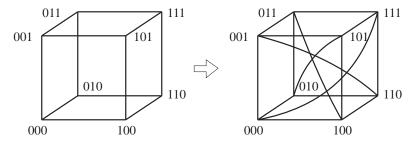

|   |     | 4.2.2  | Folded $N$ -hypercube                        |

|   | 4.3 | Comp   | aring tree-like -vs- graph-like designs      |

|   |     | 4.3.1  | Average distance in links among hosts        |

|   |     | 4.3.2  | Average distance in links among end switches |

|   |     | 4.3.3  | Results and analysis                         |

|   | 4.4 | Other  | mesh and star topologies                     |

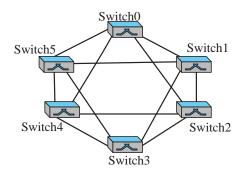

|   |     | 4.4.1  | Full mesh                                    |

|   |     | 4.4.2  | Quasi full mesh                              |

|   |     | 4.4.3  | Star                                         |

|   | 4.5 | Toroid | lal grid topologies                          |

|   |     | 4.5.1  | Redundant ring                               |

Contents

|   | 4.6   | 4.5.2 Toroidal ring                             | 125<br>126 |

|---|-------|-------------------------------------------------|------------|

|   | 4.0   |                                                 | 120        |

|   |       | <i>y</i> 0 1                                    | 120 $128$  |

|   | 4.7   |                                                 | 120 $129$  |

|   | 4.1   | Undirected-graph topologies                     | 129 $130$  |

|   |       | v 0                                             | 130        |

|   |       | 001                                             | 132        |

|   |       | 4.7.3 Cage graphs                               | 136        |

|   |       | 4.7.3.2 Heawood graph                           | 130        |

|   | 4.8   | Summary                                         | 137        |

| 5 | Mod   | delling network Data Centre topologies with ACP | 139        |

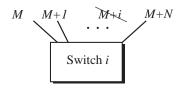

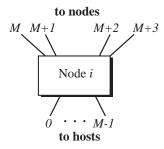

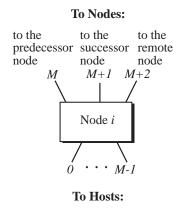

| 0 | 5.1   | Hosts, switches and ports                       | 140        |

|   | 5.2   | Modelling hosts                                 | 141        |

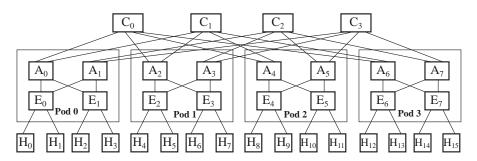

|   | 5.3   | Fat tree                                        | 145        |

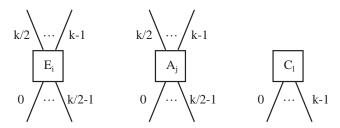

|   |       | 5.3.1 Edge switches                             | 146        |

|   |       | 5.3.2 Aggregation switches                      | 147        |

|   |       | 5.3.3 Core switches                             | 150        |

|   |       | 5.3.4 Consolidating fat tree                    | 151        |

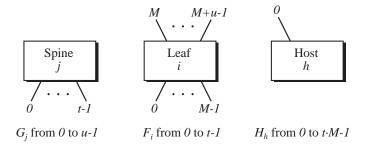

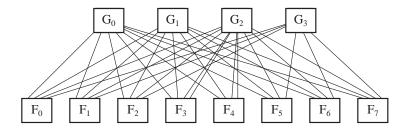

|   | 5.4   | Leaf and spine                                  | 158        |

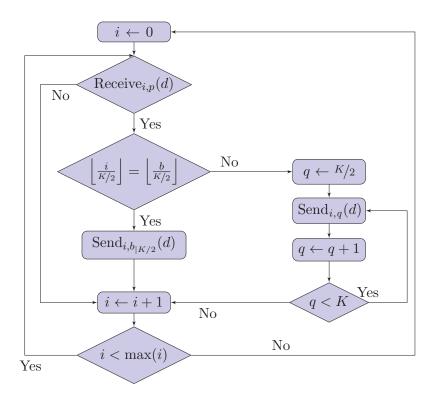

|   |       | 5.4.1 Leaf switches                             | 160        |

|   |       | 5.4.2 Spine switches                            | 161        |

|   |       | 5.4.3 Consolidating leaf and spine              | 163        |

|   | 5.5   | N-hypercube                                     | 165        |

|   | 5.6   | Folded $N$ -hypercube                           | 173        |

|   | 5.7   | Full mesh                                       | 179        |

|   | 5.8   | Quasi full mesh                                 | 183        |

|   | 5.9   | Redundant star                                  | 186        |

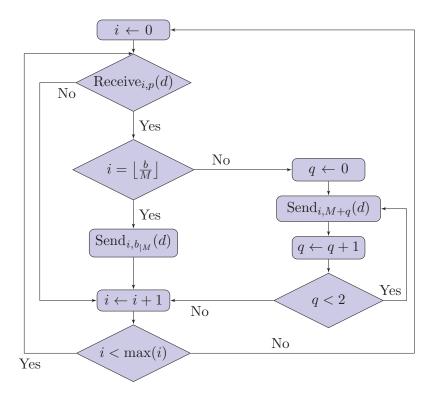

|   |       | 5.9.1 Spoke switches                            | 187        |

|   |       | 5.9.2 Hub switches                              | 188        |

|   |       | 5.9.3 Consolidating hub and spoke               | 189        |

|   | 5.10  | Redundant ring                                  | 191        |

|   | 5.11  | Toroidal ring                                   | 194        |

|   | 5.12  | De Bruijn graph                                 | 197        |

|   | 5.13  | De Bruijn reverse graph                         | 203        |

|   | 5.14  | Binary grid                                     | 206        |

|   | 5.15  | Hamming graph                                   | 209        |

|   | 5.16  | Petersen graph                                  | 213        |

|   | 5.17  | Heawood graph                                   | 217        |

|   | 5 1 2 | Summary                                         | 222        |

xvi

| 6  | Generalization of Data Centre models with ACP                          | 227   |

|----|------------------------------------------------------------------------|-------|

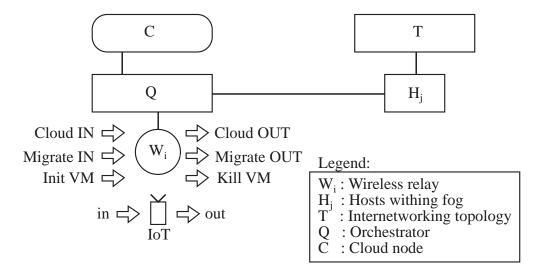

|    | 6.1 Topology framework for a generic fog model                         | . 227 |

|    | 6.2 Modelling VM actions within a fog environment with ACP             | . 230 |

|    | 6.2.1 Action cloud in $\dots$                                          | . 231 |

|    | 6.2.2 Action migrate in $\dots$                                        |       |

|    | 6.2.3 Action init $VM$                                                 | . 235 |

|    | 6.2.4 Action $cloud\ out\ \dots\dots\dots\dots\dots\dots\dots$         | . 236 |

|    | 6.2.5 Action migration out $\dots \dots \dots \dots \dots \dots \dots$ | . 238 |

|    | 6.2.6 Action $kill\ VM$                                                |       |

|    | 6.3 Verification of the models                                         | . 240 |

|    | 6.4 Summary                                                            | . 242 |

| 7  | Use case of Data Centre models                                         | 245   |

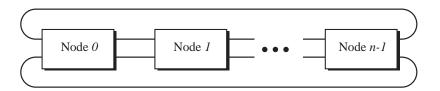

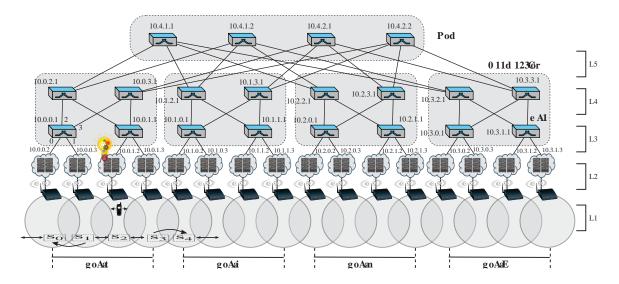

|    | 7.1 Sequential relay - schematic diagram                               | . 245 |

|    | 7.2 Topology framework for linear deployments                          | . 247 |

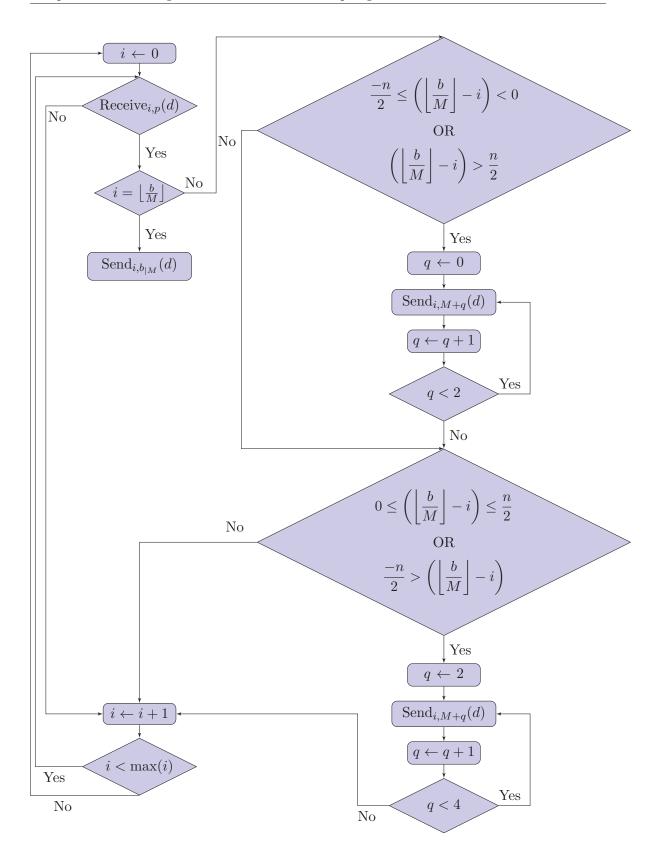

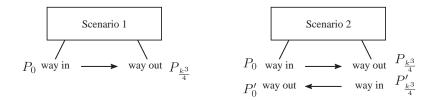

|    | 7.3 Scenario 1: one-way and no resource restrictions                   | . 250 |

|    | 7.4 Scenario 2: two-way and resource restrictions                      |       |

|    | 7.5 Model verification                                                 | . 263 |

|    | 7.6 Summary                                                            | . 267 |

| 8  | Conclusions and Future Work                                            | 269   |

|    | 8.1 Conclusions                                                        | . 269 |

|    | 8.2 Future work                                                        | . 275 |

| 9  | Publications                                                           | 279   |

| 10 | ) Appendix                                                             | 285   |

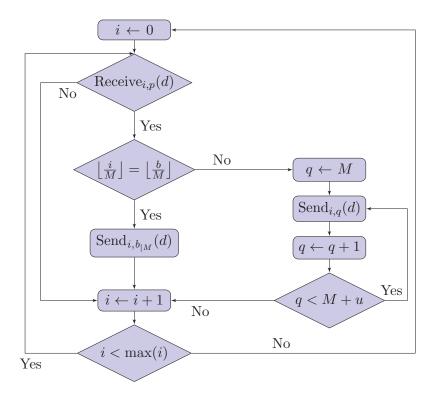

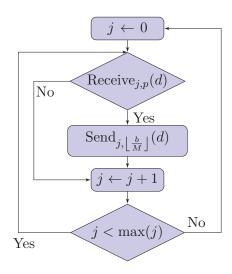

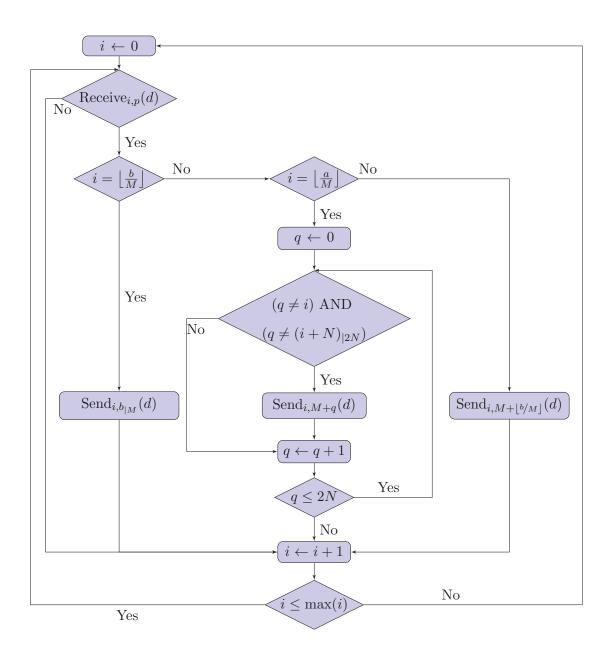

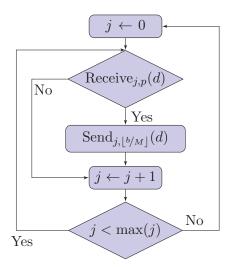

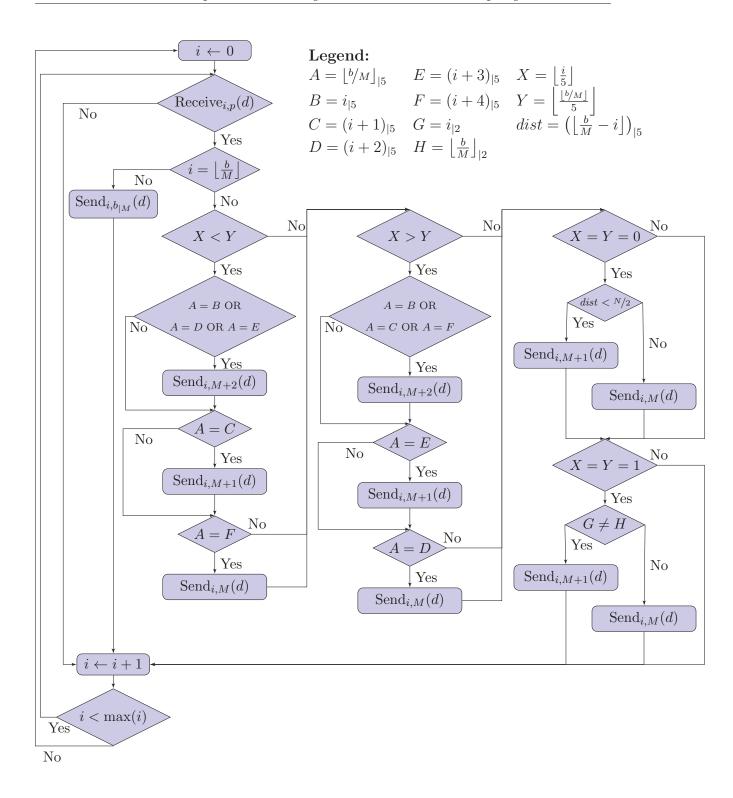

|    | 10.1 Algorithm for a host                                              | . 285 |

|    | 10.2 Algorithm for an edge switch in fat tree                          | . 286 |

|    | 10.3 Algorithm for an aggregation switch in fat tree                   | . 287 |

|    | 10.4 Algorithm for a core switch in fat tree                           | . 287 |

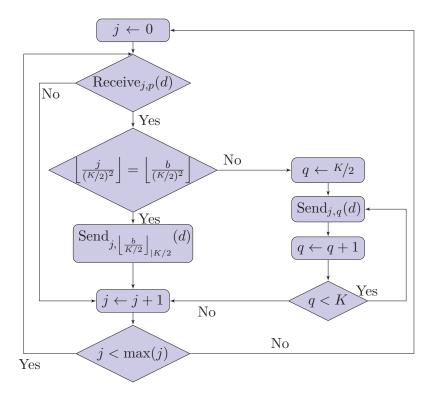

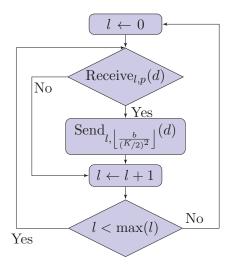

|    | 10.5 Algorithm for a leaf switch in leaf and spine                     | . 288 |

|    | 10.6 Algorithm for a spine switch in leaf and spine                    | . 288 |

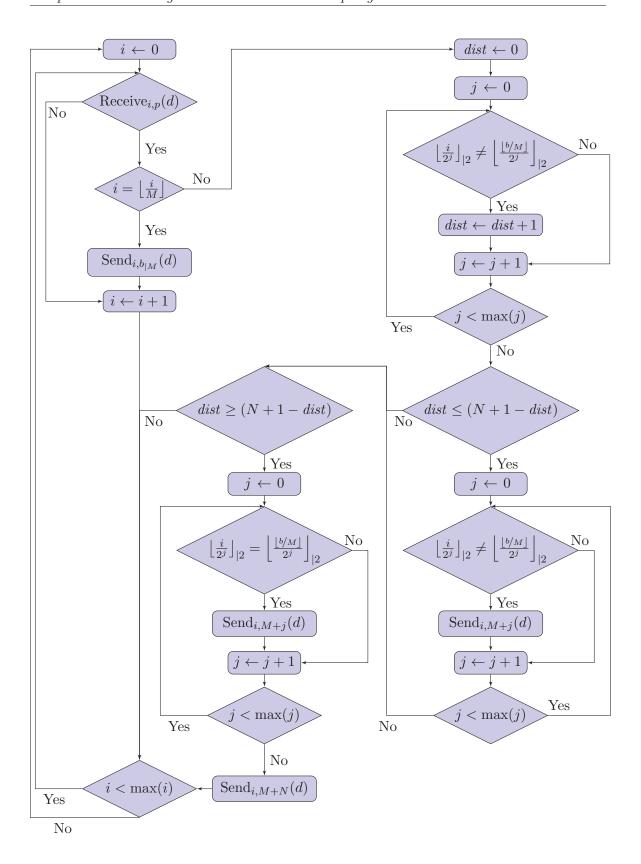

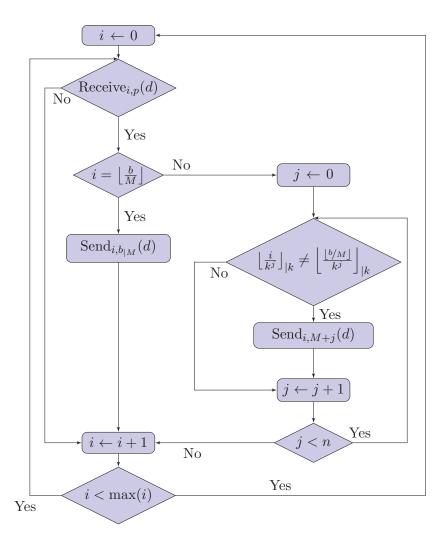

|    | 10.7 Algorithm for an $N$ -hypercube switch                            | . 289 |

|    | 10.8 Algorithm for a folded $N$ -hypercube switch                      | . 290 |

|    | 10.9 Algorithm for a full mesh switch $\{N\text{-simplex}\}$           | . 291 |

|    | 10.10Algorithm for a quasi full mesh switch $\{N\text{-orthoplex}\}$   | . 292 |

|    | 10.11Algorithm for a spoke switch in a redundant star                  | . 293 |

|    | 10.12Algorithm for a hub switch in a redundant star                    | . 293 |

|    | 10.13Algorithm for a redundant ring switch                             | . 294 |

|    | 10.14Algorithm for a toroidal ring switch                              | . 295 |

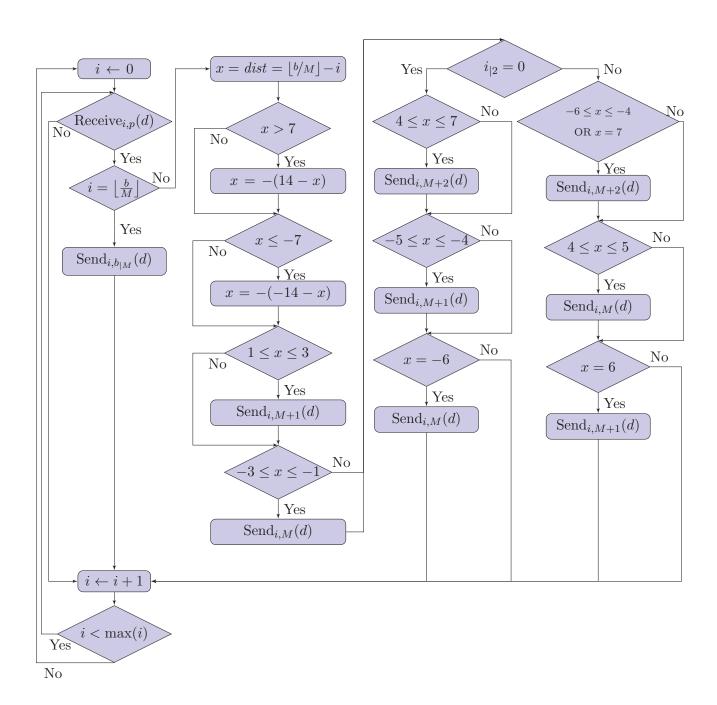

|    | 10.15Algorithm for a de Bruijn graph switch                            | . 296 |

| 10.16 Algorithm for a de Druijn reverse gran | sh c | <br>:+, | ah. |   |   |   |   |   |   |   |   |   |   |   | 207 |

|----------------------------------------------|------|---------|-----|---|---|---|---|---|---|---|---|---|---|---|-----|

| 10.16Algorithm for a de Bruijn reverse grap  |      |         |     |   |   |   |   |   |   |   |   |   |   |   |     |

| 10.17Algorithm for a binary grid switch      |      |         |     |   |   |   |   |   |   |   |   |   |   |   |     |

| 10.18Algorithm for a Hamming graph switch    |      |         |     |   |   |   |   |   |   |   |   |   |   |   |     |

| 10.19Algorithm for a Petersen graph switch   |      |         |     |   |   |   |   |   |   |   |   |   |   |   |     |

| 10.20Algorithm for a Heawood graph switch    | h.   | •       | ٠   | • | • | • | • | • | • | • | • | • | • | • | 301 |

| Bibliography                                 |      |         |     |   |   |   |   |   |   |   |   |   |   | , | 307 |

xviii Contents

## List of Figures

| 2.1  | Cloud service models                                                        |

|------|-----------------------------------------------------------------------------|

| 2.2  | VM migration timeline                                                       |

| 2.3  | Example of bisimilarity                                                     |

| 2.4  | Most common network topologies                                              |

| 2.5  | Instances of topologies with a tree-like design and a graph-like design. 38 |

| 3.1  | Platonic solids                                                             |

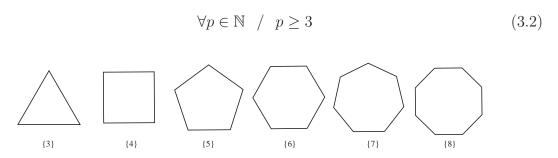

| 3.2  | Convex regular polygons                                                     |

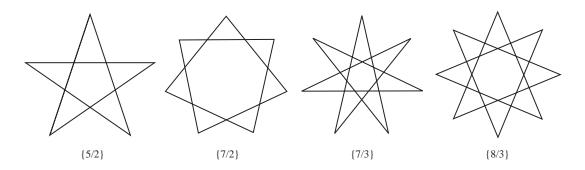

| 3.3  | Star regular polygons                                                       |

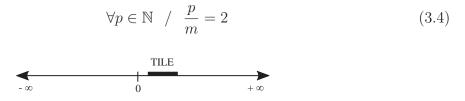

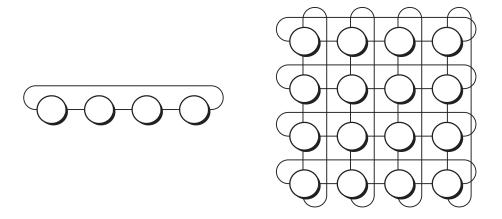

| 3.4  | Regular tessellation of the $1D$ Euclidean line                             |

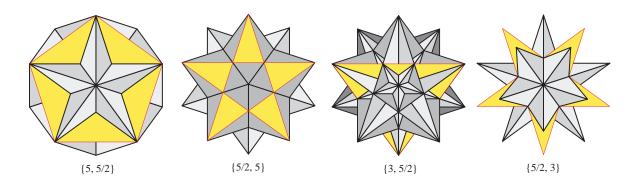

| 3.5  | Star regular polyhedra                                                      |

| 3.6  | Regular tessellation of the $2D$ Euclidean plane                            |

| 3.7  | Regular tessellation of the $3D$ Euclidean space                            |

| 3.8  | N-simplex shapes for lower dimensions                                       |

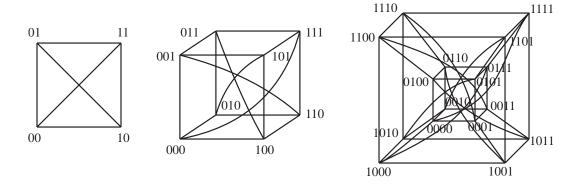

| 3.9  | N-hypercube shapes for lower dimensions 6                                   |

| 3.10 | N-orthoplex shapes for lower dimensions 62                                  |

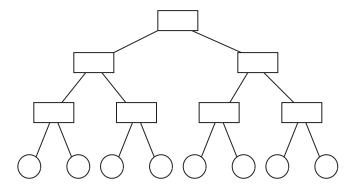

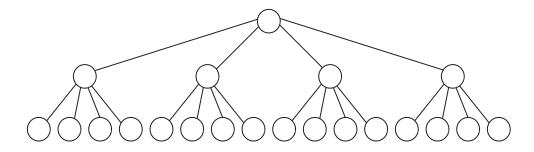

| 3.11 | Perfect binary tree with height 3                                           |

| 3.12 | Perfect ternary tree with height 3                                          |

|      | Perfect quaternary tree with height 3                                       |

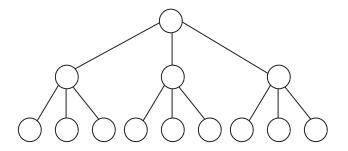

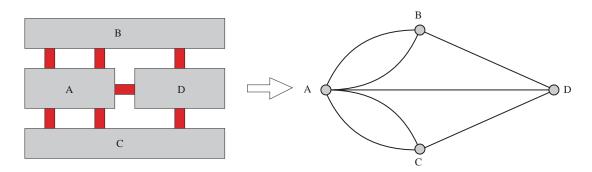

| 3.14 | Topology of the 7 bridges of Königsberg, along with its graph 7             |

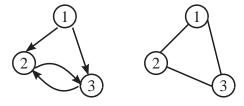

| 3.15 | Directed -vs- undirected graphs                                             |

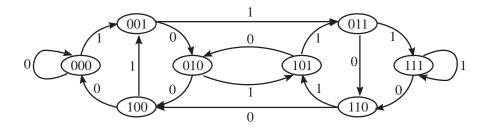

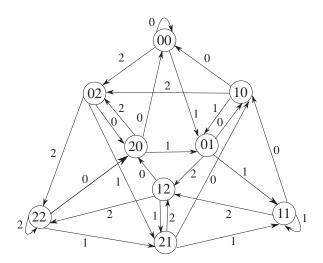

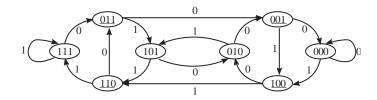

| 3.16 | De Bruijn graph: Eulerian $B(2,4)$ and Hamiltonian $B(2,3)$                 |

| 3.17 | Ring torus geometry                                                         |

| 3.18 | Forming a torus from a square                                               |

| 3.19 | Toroidal structures: line (along $1D$ ) and ring (along $2D$ ) 85           |

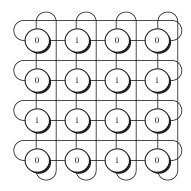

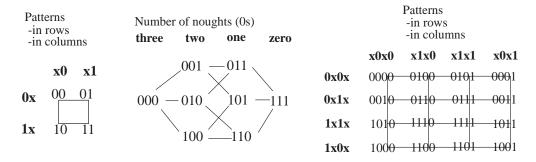

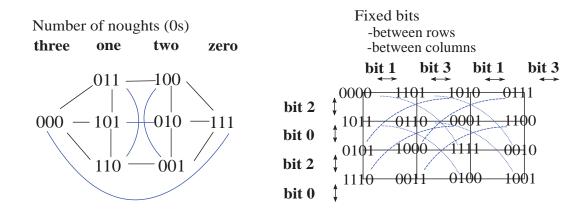

| 3.20 | De Bruijn binary square torus with a squared pattern: $(4,4;2,2)_2$ 8'      |

| 3.21 | De Bruijn torus $(4,4;2,2)_2$ : squared patterns                            |

| 3.22 | Various bidimensional toroidal arrays                                       |

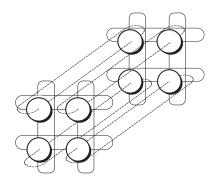

| 3.23 | Three-dimensional toroidal array $(2 \times 2 \times 2 \text{ nodes})$      |

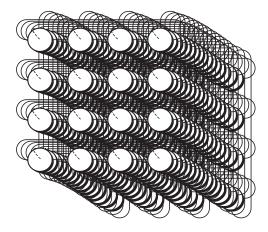

| 3.24 | Three-dimensional toroidal array ( $16 \times 4 \times 4$ nodes) 93         |

<u>xx</u> <u>List</u> of Figures

| 4.1  | Fat tree architecture for $K = 4$ and oversubscription ratio 1:1                          | 101 |

|------|-------------------------------------------------------------------------------------------|-----|

| 4.2  | Leaf and spine architecture with 8 leaves and 4 spines                                    | 103 |

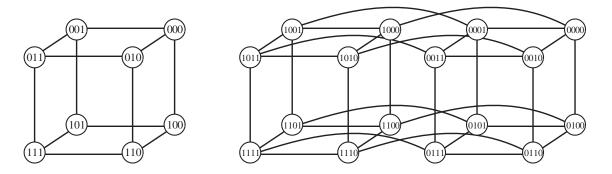

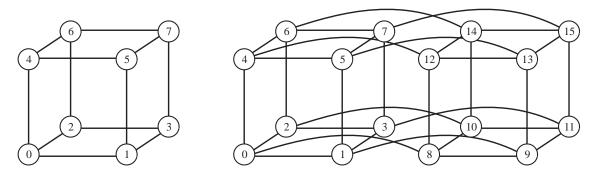

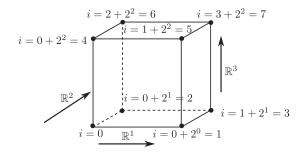

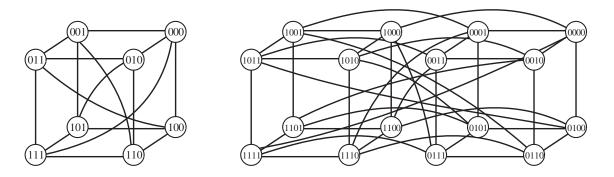

| 4.3  | N-hypercube architectures for $N \in \{0 \cdots 4\}$                                      | 105 |

| 4.4  | Pascal's triangle for the first rows                                                      | 107 |

| 4.5  | Converting a plain $N$ -hypercube into a folded $N$ -hypercube                            | 108 |

| 4.6  | Folded N-hypercube architectures for $N \in \{2 \cdots 4\}$                               | 108 |

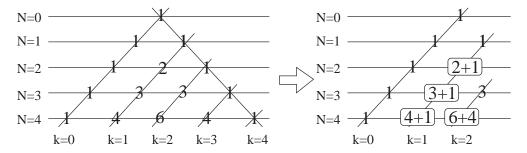

| 4.7  | Converting a Pascal's triangle into a folded Pascal's triangle                            | 110 |

| 4.8  | Folded Pascal's triangle for the first rows                                               | 110 |

| 4.9  | Full mesh topology                                                                        | 121 |

| 4.10 |                                                                                           | 122 |

| 4.11 | Hub and Spoke topology                                                                    | 123 |

|      | Redundant Hub and Spoke with a direct communication link                                  | 124 |

|      | Hamiltonian paths for $B(2,3)$                                                            | 126 |

|      | Eulerian path for $B(2,4)$                                                                | 127 |

|      | Paths in and out of a node in a binary de Bruijn graph                                    | 127 |

| 4.16 | De Bruijn graph $B(3,2)$                                                                  | 128 |

|      | De Bruijn reverse graph: Hamiltonian $\overline{B}(2,3)$ and Eulerian $\overline{B}(2,4)$ | 129 |

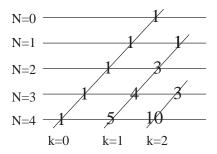

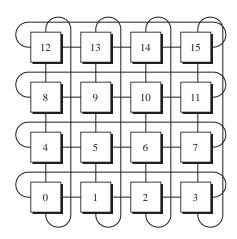

|      | Binary grid for $n = 2$ , $n = 3$ , $n = 4$                                               | 130 |

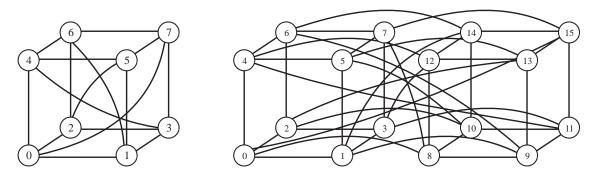

|      | Hamming graph $H_2(n, n-1)$ for $n=3$ and $n=4$                                           | 133 |

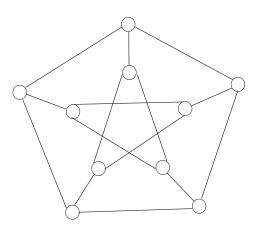

|      | Petersen graph                                                                            | 136 |

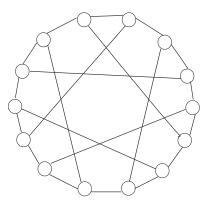

| 4.21 | Heawood graph                                                                             | 137 |

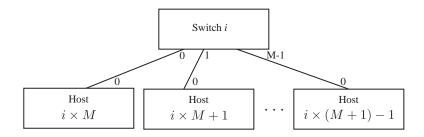

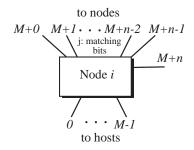

| 5.1  | Model for a generic switch $i$ , with its connected hosts                                 | 141 |

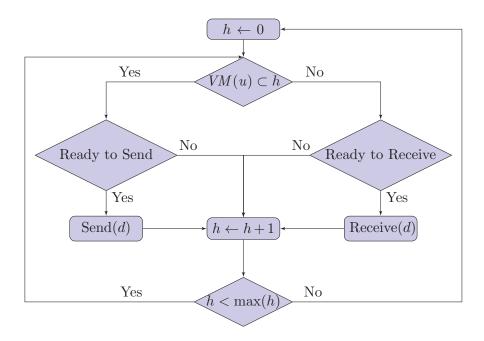

| 5.2  | Model for a generic host $h$                                                              | 143 |

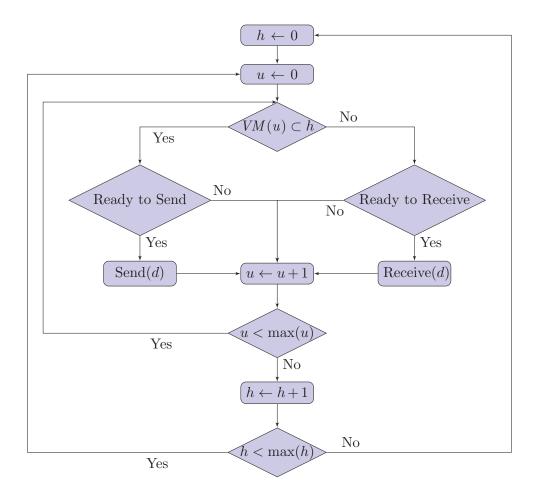

| 5.3  | Flow chart for hosts, with a unique user                                                  | 144 |

| 5.4  | Flow chart for hosts, with several users                                                  | 145 |

| 5.5  | Model for switches and their ports in fat tree                                            | 146 |

| 5.6  | Fat tree device nomenclature for $K = 4$                                                  | 146 |

| 5.7  | Flow chart for the behaviour of an edge switch (fat tree)                                 | 148 |

| 5.8  | Flow chart for the behaviour of an aggregation switch (fat tree)                          | 149 |

| 5.9  | Flow chart for the behaviour of a core switch (fat tree)                                  | 151 |

| 5.10 | Model for switches and their ports in leaf and spine                                      | 159 |

|      | Leaf and spine device nomenclature                                                        | 160 |

|      | Flow chart for the behaviour of an leaf switch (leaf and spine)                           | 161 |

| 5.13 | Flow chart for the behaviour of a spine switch (leaf and spine)                           | 162 |

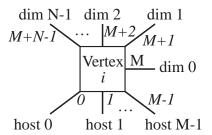

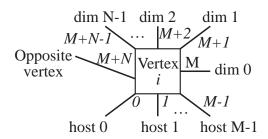

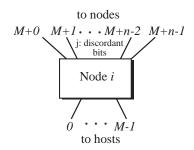

|      | Model for switches and their ports in $N$ -hypercube                                      | 167 |

|      | Node nomenclature using $N$ binary values: 3 (left) and 4 (right)                         | 167 |

|      | Node nomenclature translated into decimal values: 3 (left) and 4 (right)                  |     |

|      | Model the interconnected switches i for 3-hypercube                                       | 168 |

|      |                                                                                           |     |

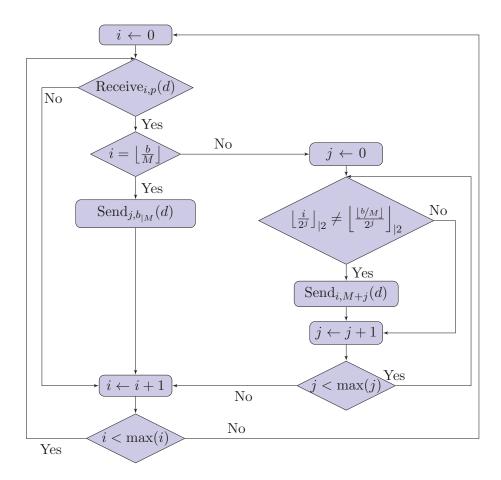

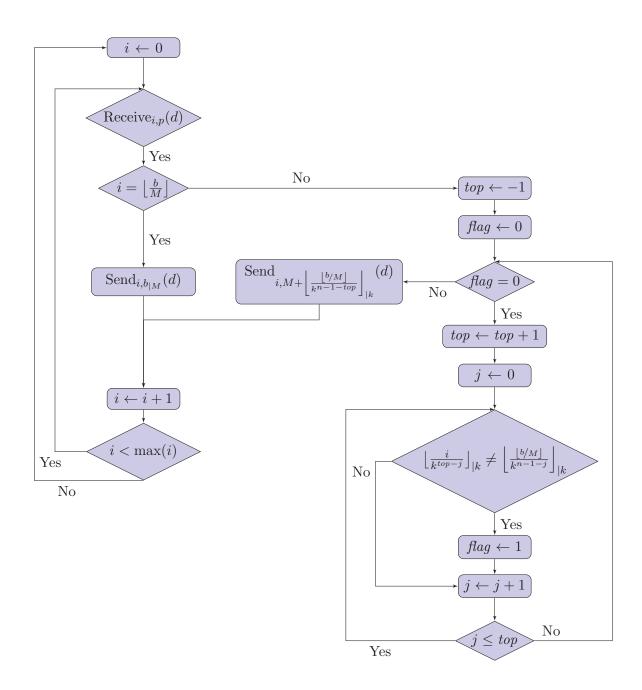

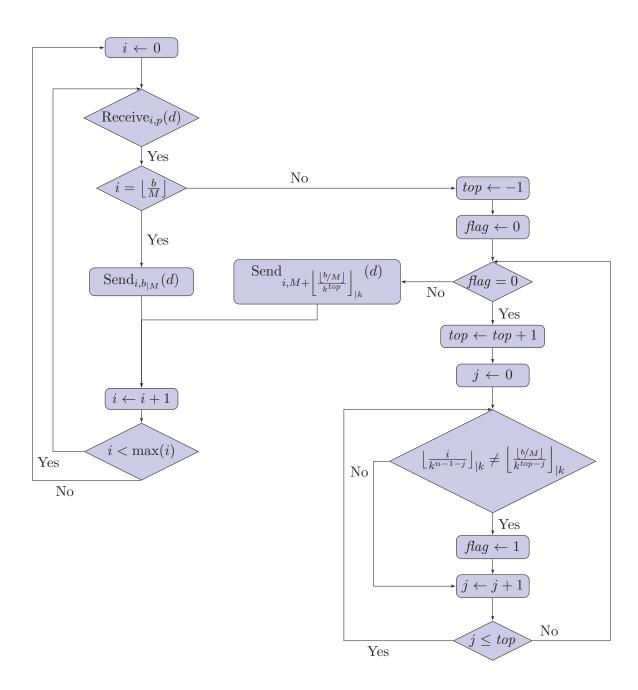

| 5.18 | Flow chart for the behaviour of a given switch ( $N$ -hypercube)                          | 169 |

|      | V 2                                                                                       |     |

| 5.19 | Flow chart for the behaviour of a given switch ( $N$ -hypercube)                          | 169 |

List of Figures xxi

| 5.21 | Node nomenclature converted into decimal values: 3 (left) and 4 (right). | 176 |

|------|--------------------------------------------------------------------------|-----|

| 5.22 | Flow chart for the behaviour of a given switch (folded $N$ -hypercube).  | 177 |

| 5.23 | Model for the uplink ports in a full mesh switch $(N-simplex)$           | 181 |

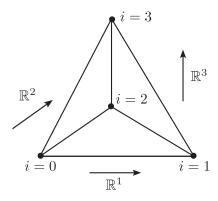

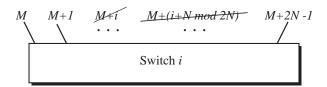

| 5.24 | Model for the interconnected switches in a 3-simplex                     | 181 |

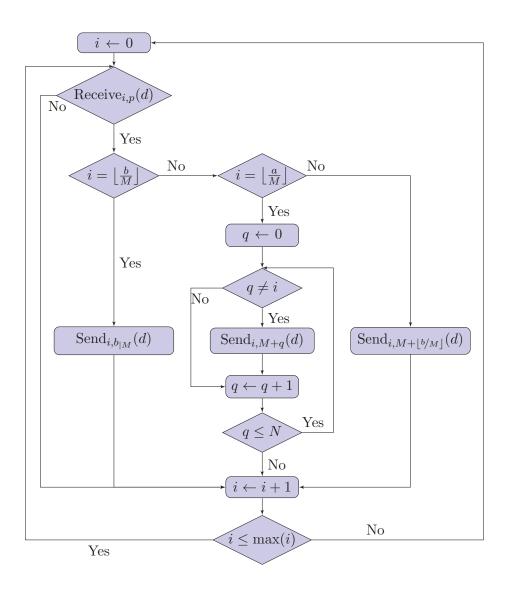

| 5.25 | Flow chart for the behaviour of a given switch $(N-simplex)$             | 182 |

| 5.26 | Model for the uplink ports in a quasi full mesh switch $(N$ -orthoplex). | 184 |

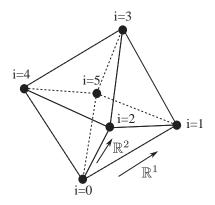

| 5.27 | Model for the interconnected switches in a 3-orthoplex                   | 184 |

| 5.28 | Flow chart for the behaviour of a given switch $(N$ -orthoplex)          | 185 |

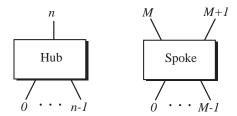

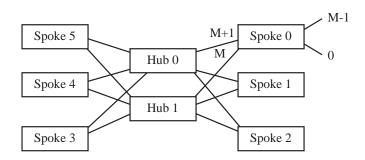

| 5.29 | Model for switches, along with its ports (redundant hub and spoke)       | 187 |

| 5.30 | Nomenclature of switches in redundant hub and spoke                      | 188 |

| 5.31 | Flow chart for the behaviour of a spoke (redundant hub and spoke)        | 189 |

| 5.32 | Flow chart for the behaviour of a hub (redundant hub and spoke)          | 190 |

| 5.33 | Model for switches, along with its ports (redundant ring)                | 192 |

| 5.34 | Node setup for a redundant ring topology                                 | 192 |

| 5.35 | Flow chart for the behaviour of a given switch (redundant ring)          | 193 |

| 5.36 | Node setup for a toroidal ring topology for $n = 4$                      | 196 |

| 5.37 | Model for switches, along with its ports (toroidal ring)                 | 196 |

| 5.38 | Flow chart for the behaviour of a given switch (toroidal ring)           | 198 |

| 5.39 | Model for a given node $i$ in a de Bruijn graph, along with its ports    | 200 |

| 5.40 | Flow chart for the behaviour of a switch (de Bruijn graph)               | 201 |

| 5.41 | Flow chart for the behaviour of a switch (de Bruijn reverse graph)       | 205 |

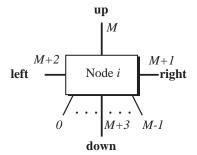

| 5.42 | Model for a given node $i$ in a Binary grid, along with its ports        | 207 |

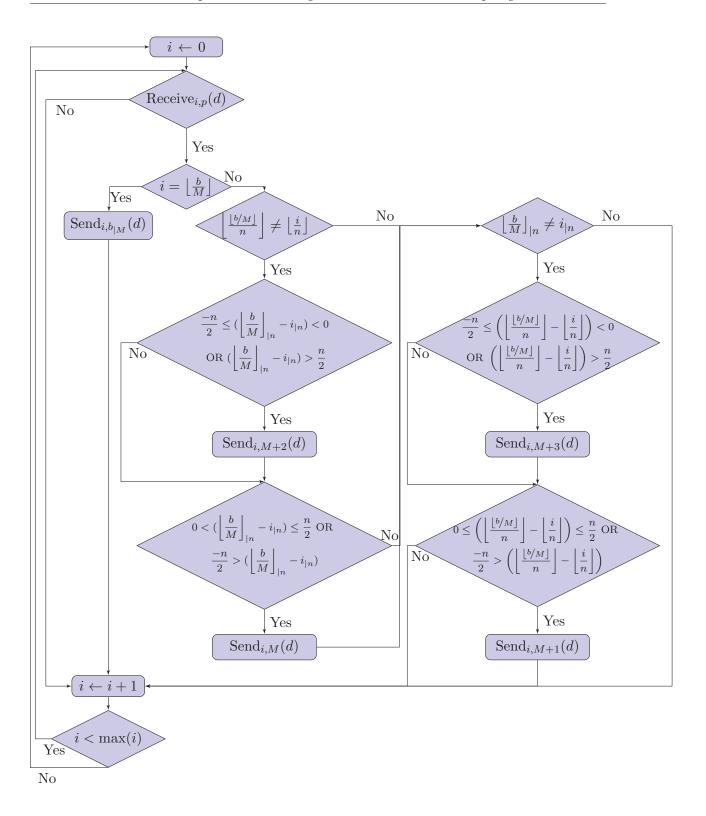

| 5.43 | Flow chart for the behaviour of a given switch (binary grid)             | 208 |

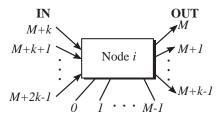

| 5.44 | Model for a node i in a Hamming graph $H_k(n, n-1)$ and its ports        | 211 |

|      | Flow chart for the behaviour of a switch (Hamming graph $H_k(n, n-1)$ ). | 212 |

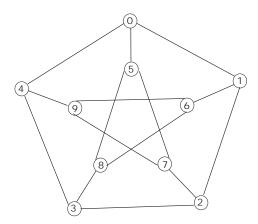

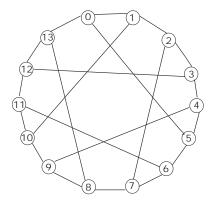

| 5.46 | Node distribution in a Petersen graph                                    | 214 |

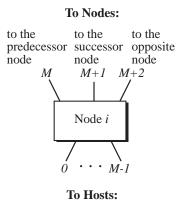

|      | Model for a given node $i$ in a Petersen graph, along with its ports     | 216 |

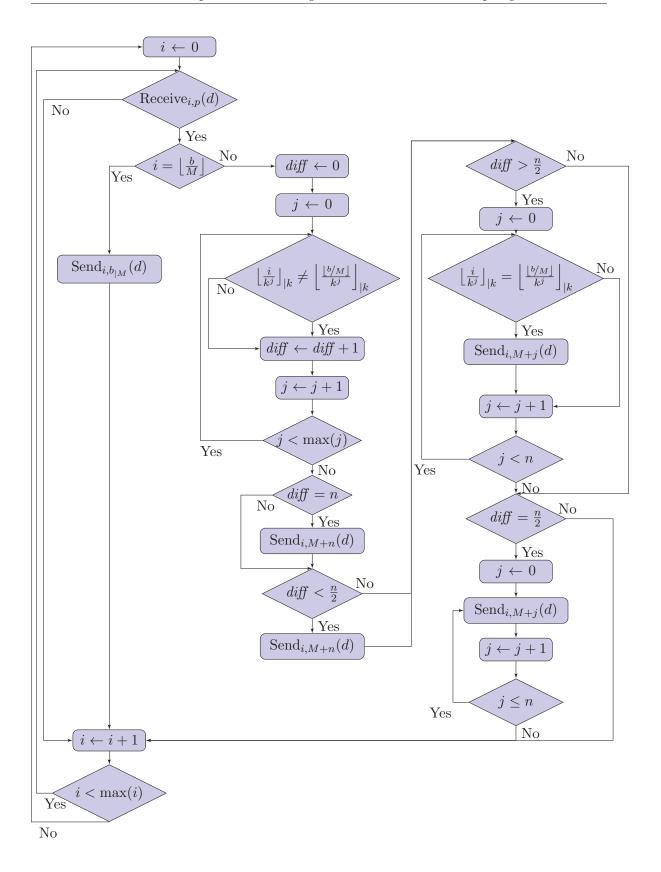

| 5.48 | Flow chart for the behaviour of a given switch (Petersen graph)          | 218 |

|      | Node distribution in a Heawood graph                                     | 219 |

| 5.50 | Model for a given node $i$ in a Heawood graph, along with its ports      | 222 |

| 5.51 | Flow chart for the behaviour of a given switch (Heawood graph)           | 224 |

| 6.1  | Generic topology scheme for an IoT/fog model                             | 228 |

| 7.1  | Schematic diagram of a fat tree sequential wireless relays               | 246 |

| 7.2  | External behaviour of scenario 1 and scenario 2                          | 265 |

xxii List of Figures

## List of Tables

| 3.1  | Platonic solids                                                                         | 46  |

|------|-----------------------------------------------------------------------------------------|-----|

| 3.2  | Convex regular polyhedra in Schläfli notation                                           | 51  |

| 3.3  | Star regular polyhedra in Schläfli notation                                             | 52  |

| 3.4  | Star regular polyhedra and their main features                                          | 52  |

| 3.5  | Convex regular polychora in Schläfli notation (I)                                       | 54  |

| 3.6  | Convex regular polychora in Schläfli notation (II)                                      | 54  |

| 3.7  | Star regular polychora in Schläfli notation                                             | 55  |

| 3.8  | Convex regular polytera in Schläfli notation                                            | 56  |

| 3.9  | Convex regular N-polytopes in Schläfli notation $(N \geq 5)$                            | 57  |

| 3.10 |                                                                                         | 59  |

| 3.11 | Amount of $k$ -facets present in each $N$ -simplex                                      | 60  |

| 3.12 | Amount of $k$ -facets present in each $N$ -hypercube                                    | 61  |

| 3.13 | Amount of $k$ -facets present in each $N$ -orthoplex                                    | 62  |

| 3.14 | Number of nodes in a perfect binary tree of height $h$                                  | 68  |

| 3.15 | Number of nodes in a perfect $M$ -ary tree of height $h$                                | 70  |

| 3.16 | Wong algorithm to achieve de Bruijn sequence $B(2,3)$                                   | 80  |

| 3.17 | Wong algorithm to achieve de Bruijn sequence $B(2,4)$                                   | 81  |

| 3.18 | De Bruijn sequences expressed as de Bruijn tori with length up to 64.                   | 90  |

| 3.19 | An instance of a $16 \times 4 \times 4$ de Bruijn hypertorus                            | 93  |

| 3.20 | An instance of all unique 256 b-cubes in a $16 \times 4 \times 4$ de Bruijn hypertorus. | 94  |

| 4.1  | Fat tree most relevant values                                                           | 101 |

| 4.2  | Number of redundant paths in fat tree among hosts                                       | 102 |

| 4.3  | Relevant number of items for the scenarios proposed (fat tree)                          | 113 |

| 4.4  | Relevant number of items for the scenarios proposed (leaf and spine).                   | 114 |

| 4.5  | Relevant number of items for the scenarios proposed $(N$ -hypercube).                   | 114 |

| 4.6  | Relevant number of items for the scenarios proposed (folded $N$ -Hyp).                  | 115 |

| 4.7  | Average distance in links ( $\lambda$ ) among hosts                                     | 118 |

| 4.8  | Average distance in links ( $\lambda$ ) among end switches                              | 119 |

| 4.9  | Known $(3, g)$ -cages                                                                   | 136 |

| 4.10 | Topologies proposed along with some relevant features                                   | 138 |

xxiv List of Tables

| 5.1  | Relevant variables and operations to be applied in the models             | 142         |

|------|---------------------------------------------------------------------------|-------------|

| 5.2  | List of devices and ports between 1-hop away hosts in fat tree            | 154         |

| 5.3  | List of devices and ports between 2-hops away hosts in fat tree           | 154         |

| 5.4  | List of devices and ports between 3-hops away hosts in fat tree           | 155         |

| 5.5  | List of devices and ports between 1-hop away hosts in leaf and spine.     | 163         |

| 5.6  | List of devices and ports between 2-hops away hosts in leaf and spine.    | 164         |

| 5.7  | Searching mismatching bits by arithmetic and logical means                | 169         |

| 5.8  | List of devices and ports between 1-hop away hosts in $N$ -hypercube.     | 170         |

| 5.9  | Permutations from source switch to destination switch in $N$ -hypercube.  | 172         |

| 5.10 | Searching the shortest path and its next hops by using of logical means.  | 176         |

| 5.11 | List of devices and ports between 1-hop away hosts in folded $N$ -hyp     | 179         |

| 5.12 | Permutations from source switch to destination switch in folded $N$ -hyp. | 180         |

| 5.13 | List of devices and ports between 1-hop away hosts in full mesh           | 181         |

| 5.14 | List of devices and ports between 2-hops away hosts in full mesh          | 183         |

| 5.15 | List of devices and ports between 1-hop away hosts in quasi full mesh.    | 186         |

| 5.16 | List of devices and ports between 2-hops away hosts in quasi full mesh.   | 186         |

| 5.17 | List of devices and ports between 1-hop away hosts in R. hub & spoke.     | 189         |

| 5.18 | List of devices and ports between 2-hops away hosts in R. hub & spoke.    | 190         |

| 5.19 | Searching the hops from source to destination node (de Bruijn graph).     | 202         |

| 5.20 | Searching the hops from source to destination node (de Bruijn rev.)       | 206         |

| C 1  |                                                                           | വൈ          |

| 6.1  | Communication channels in the model                                       | <b>∠</b> 3U |

## List of Algorithms

| 1  | $\operatorname{Host}()$                                                              | 285 |

|----|--------------------------------------------------------------------------------------|-----|

| 2  | Fat tree - edge()                                                                    | 286 |

| 3  | Fat tree - aggregation()                                                             | 287 |

| 4  | Fat tree - core()                                                                    | 287 |

| 5  | Leaf and spine - leaf() $\dots$                                                      | 288 |

| 6  | Leaf and spine - spine() $\dots \dots \dots \dots \dots \dots \dots$                 | 288 |

| 7  | N-hypercube()                                                                        | 289 |

| 8  | Folded $N$ -hypercube()                                                              | 290 |

| 9  | Full mesh() $\{N\text{-simplex}\}$                                                   | 291 |

| 10 | Quasi full mesh() $\{N\text{-orthoplex}\}$                                           | 292 |

| 11 | Redundant hub and spoke - spoke<br>() $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 293 |

| 12 | Redundant hub and spoke - hub() $\dots \dots \dots \dots \dots$                      | 293 |

| 13 | ${\rm Redundant\ ring}()\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\$                    | 294 |

| 14 | Toroidal ring()                                                                      | 295 |

| 15 | De Bruijn graph()                                                                    | 296 |

| 16 | De Bruijn reverse graph()                                                            | 297 |

| 17 | Binary grid()                                                                        | 298 |

| 18 | Hamming graph() $\{H_k(n, n-1)\}$                                                    | 299 |

| 19 | Petersen graph() $\dots$                                                             | 300 |

| 20 | Heawood graph()                                                                      | 301 |

### Chapter 1

### Introduction

#### 1.1 Context

Cloud computing paradigm has been consolidated in recent years, as traditional computing deployments are quite often being extended with the addition of extra assets, usually off-site, those being external resources basically regarding processing power and storage facilities, which are reached by service users through any sort of network connection.

Cloud scenarios provide many advantages compared to on-premise scenarios, such as ubiquitous computing, cost savings and on-demand resource flexibility. However, cloud's core nature may impose implicit disadvantages, such as not being appropriate in real-time scenarios, due to the latency involved in reaching the cloud and getting back, or otherwise, not being fit for its use in low-resource devices.

In order to cope with those limitations, fog computing paradigm represents an extension of the cloud by bringing the computing resources to the edge of the network. This way, latency and jitter rates get reduced and resource utilization gets decreased, whilst keeping the advantages of remote computation.

On the other hand, IoT (Internet of Things) devices are ordinary items equipped with computing and networking capabilities so as to get them connected in order to achieve a more efficient performance, thus making possible the enhanced deployment of smart cities and smart grids or the use of cyber physical systems in Industry 4.0.

Those devices usually have limited resources regarding processing power, memory allocation, storage capacity, bandwidth restrictions and low-power batteries.

IoT devices make the perfect candidates for the fog computing paradigm, and that is why the combination of both is often referred to as IoT/fog environments. In this context, it is to be said that such environments are usually divided into three hierarchical layers, where in the lower one there are IoT devices like sensors, actuators, smartphones, tablets or cars, whereas in the middle one there are fog nodes, also known as hosts, with higher computing power than the former, thus dealing with most of the data generated by those, whilst in the upper one there are back-end cloud nodes so as to manage data requiring an extensive use of computing power or storage.

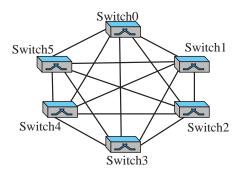

The most typical scenario is that of a group of IoT items, ranging from a few to a myriad, being all connected to some central servers forming the fog layer, according to a hub and spoke topology, where those hosts undertake most of the workload, although they may divert some of it to a cloud backup node.

Special attention has to be paid to those IoT devices in fog environments where they may be moving around the fog facilities, those being distributed along a limited geographic area. In such a case, it is important that the computing resources allocated to each user on the fog infrastructure, normally deployed as virtual instances in the form of a VM (Virtual Machine) or a virtual container, get as close as possible to the physical locations of their respective users, hence, latency and jitter get reduced, whereas bandwidth needs get minimized. It is to be noted that, in the context of this thesis, when these virtualized entities associated to users are mentioned, they will be generically referred to as VMs, although the approach using virtual containers would be very similar.

Additionally, when the IoT devices have mobility, the communication delay between a moving device and its associated computing assets may increase with the distance among them, thus getting to degrade the performance as such a distance grows. In this context, the concept of distance refers to number of links making the path between two given source and destination entities, which depends on the network topology of the DC (Data Centre) in use. Hence, in order to keep such a distance within a reasonable range at all times whilst allowing the device to keep moving, it

may be necessary to also move its related assets in some way to get them close enough to each other.

VM migration is the mechanism for a VM to try and follow its associated user while it moves through the fog environment. This migration takes place between the source host where the VM is currently held to the destination host where the VM is ready to move so as to minimise the distance towards its related user.

The migration path will try to follow the shortest available path between source and destination hosts. There may well be redundant paths, and in such a case, load balancing policies may be applied. Anyway, those paths definitely depend on the topology of the fog environment, thus, they will be related to the interconnections put in place among switches.

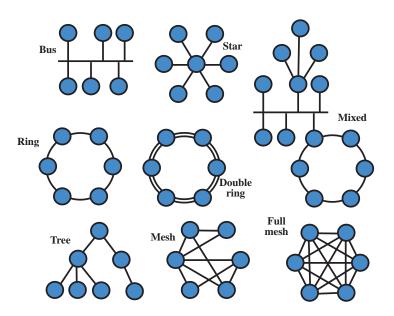

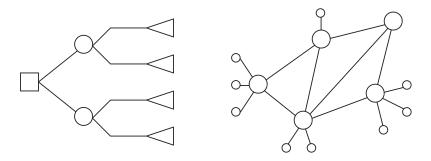

There are many different topologies being used in fog computing to interconnect hosts, each of them with their own benefits and drawbacks. The ideal situation would be a full-mesh infrastructure, where all hosts would be just one hop apart from each other. However, as the number of hosts increases, this approach is not feasible, so partial-mesh solutions come into play.

Among partial-mesh solutions, a distinction between hierarchical and flat views may be noted, the former presenting more advantages as the number of hosts grow, making tree-like designs, whereas the latter allowing for good solutions for smaller numbers, presenting graph-like designs.

As per the tree-like category, fat tree and leaf and spine get the most referenced instances in the literature related to fog computing, whilst regarding the graph-like category, plain N-hypercube is a typical instance, along with a well-known extension called folded N-hypercube.

Furthermore, *hub and spoke* designs are widely considered in real deployments, where there is a central entity, called hub, which establishes a point-to-point connection to each of the other entities, named spokes. Therefore, all communications between any pair of spokes need to go through the hub.

There may be many variations in all those categories, some of them presenting advantages on the performance side, in spite of introducing some degree of complication on the design and on the packet forwarding side. Therefore, in order to achieve a good trade-off between both parameters, the most basic instances are still widely used in many fog deployments.

Regarding the IoT devices being found in a fog environment, it is to be remarked that those IoT items are usually ordinary devices equipped with limited resource capabilities, which bring some sensors or actuators attached, thus playing the part of end devices for fog communications. Furthermore, the fog infrastructure is made up of a series of hosts being located anywhere between the end devices and the cloud, whose role is to undertake most of the computation and storage necessities of the aforesaid IoT devices, using the cloud as a backup system.

Those hosts may be interconnected by a network of switches, which are linked together according to a certain topology in order to allow the VM migration of a given instance of VM from any source host to any destination host, where different topology deployments may be put in place in relation to the needs of each fog ecosystem.

Hence, each switch joins together a bunch of hosts, resulting in only two links between any pair of those, whereas all switches communicate to each other through a certain topology, which determines the number of links between any pair of switches, resulting in a variable number of links between hosts connected to different switches. In this context, some key performance indicators, such as latency, jitter and bandwidth, will depend on the precise number of such links between any couple of hosts.

Furthermore, it is to be considered that switching topologies offer scalability, resilience and load balancing among the diverse hosts within the fog domain, thus making possible that the aforementioned VM migrations between any given pair of hosts may be carried out by means of alternative paths, which may depend on the switching topology being chosen within the fog environment.

Additionally, it is to be noted that fog environments may not contain a great amount of hosts due to the limited geographic scope of fog domains. Therefore, the number of necessary switches to interconnect all those hosts will not be too high, hence, fog deployments may not need complicated topologies.

On the other hand, some complex topologies might obtain better performance indicators that the ones presented, even though such a complexity in those designs may make packet forwarding more difficult to be achieved. Thus, such designs may not be taken into account herein, so in order to keep things simple, just the aforesaid topologies are going to be considered herein.

With that in mind, all of the moving devices within a fog environment may need its associated computing resources to be the closest possible. This fact implies moving those computing resources among hosts, and if those are considered as VMs, then it may be said that live VM migrations may take place among hosts.

With respect to the minimal paths in each topology to achieve the fastest VM migration by means of taking the shortest path between a particular pair of hosts, it is to be said that it may be expressed by applying the appropriate mathematical expressions, which may result in the construction of different models according to diverse mathematical areas, such as arithmetic, logic or algebra.

In this sense, flow charts and pseudocode algorithms are presented for all topologies selected, although special attention needs to be paid to algebraic models, specifically designed by means of a process algebra called ACP (Algebra of Communicating Processes), as they may be further used in order to find out whether the algebraic models presented get verified, which basically means that the behaviour of the model proposed matches that of the real system, in a way that all possible inputs in both generate the desired outputs in both.

It is to be remarked that ACP does not take time into consideration, thus the measurement of performance may not based on time, as it is the usual case where performance is evaluated by means of timed process algebras, queueing networks or timed Petri nets. Hence, the focus on performance has been swapped from time to space, related to switching infrastructure and redundant paths, leading to distances, and this way, performance may be evaluated by means of timeless Petri nets or timeless process algebras, where ACP belongs to.

Regarding networking, bandwidth and latency are the key players when dealing with performance analysis. This is usually measured in time units, even though an alternative view may be to measure distance as a measure of time, as long as all links within the DC have the same bandwidth and the same features, whereas their link lengths are also the same. If that is the case, distance is directly proportional to time, such that if distance increases, so does time. In view of that, distance is going to be

used herein to measure performance as the number of links between any given pair of devices because it is more intuitive and straightforward, where the shorter the better.

In this context, routing is crucial to enhance performance, as it minimizes the number of links to forward packets between a particular source and a particular destination within the DC. Other important parameters may also be cited, such as the protocol being used and the link utilization due to inefficiencies of implementation or environmental conditions, although only routing is going to be considered herein.

Therefore, the main working hypothesis of this thesis dissertation may be whether it is possible to model the VM migration path within a given DC topology being deployed in a fog environment by means of ACP. Furthermore, some other main working hypotheses may be proposed, such as the construction of a generic model for a fog ecosystem in ACP, where the DC topology is abstracted away, followed by the built-up of a particular instance of it, being focused on linear deployments, which is also designed with ACP. Additionally, some secondary working hypotheses may be brought forward, such as getting such models by means of flow charts and pseudocode algorithms, along with getting the list of devices and their appropriate ports for all redundant minimal paths (measured in number of links) for the models in ACP, as well as getting the appropriate verification for them.

This way, the target of this work may be seen mainly as threefold: first, to obtain formal algebraic models of VM migration for the aforementioned topologies, then, to achieve a formal algebraic model for any user moving around a generic fog environment, and from there on, to build up a specific scenario with a sequential layout, which may be adapted to bring fog services throughout a trajectory.

#### 1.2 Objectives

Therefore, the goals in this thesis are:

• To review the state of the art regarding the main pillars of this research, such as fog computing environments, Formal Description Techniques (FDT) and network topologies for DC.

- To go over some mathematical objects to be used in the models proposed, such as regular N-polytopes, trees, graphs and tori.

- To revise the main characteristics of the DC topologies presented.

- To obtain different mathematical models for VM migration in fog ecosystems for such topologies, where the amount of nodes within a given topology depends on the number of hosts needed in the fog deployment.

- To establish a generic algebraic model for a fog computing domain.

- To propose an application of such a model for a sequential deployment.

This way, the main hypotheses proposed above are going to be developed in order to prove them right:

- a ) Is it possible to model the VM migration path within a given DC topology being deployed in a fog environment by means of ACP?

- b ) Is it possible to construct a generic model for a fog ecosystem in ACP, where the DC topology is abstracted away?

- c ) Is it possible to build up a particular instance of such a general model in ACP which is being focused on linear deployments?

Additionally, the secondary hypotheses cited above will also be developed on the way to prove the main one quoted in the first place.

#### 1.3 Outline

The development of this thesis involves three parts as follows:

• Part one: background. This includes a brief overview on the main pillars sustaining this thesis. In particular, chapter 1 introduces some of the main features of fog computing, whilst chapter 2 discusses the role of live VM migration

in fog domains, modelling with ACP and DC topologies. Furthermore, chapter 3 goes through some mathematical foundations to be applied on the network topology models proposed later on, whereas chapter 4 reviews some of the most common DC topologies for fog deployments.

- Part two: contribution. It is focused on the new proposals given in this thesis. In this sense, chapter 5 exhibits different mathematical modellings for each of the aforementioned topologies, including algebraic representations to be used in the verification of such designs, whilst chapter 6 presents an algebraic model of a generic fog environment, abstracting away from the topology being used, and chapter 7 carries out a real-life application of such a model for sequential deployments, which may be implemented in railways, highways or pipelines.

- Part three: conclusions. That contains the final references associated with this thesis. Basically, chapter 8 draws the conclusions reached out of this thesis dissertation, as long as the future work proposals. Afterwards, chapter 9 shows the contributions achieved with this thesis, resulting in a collection of research papers published in international conferences and journals related to the foundational pillars cited above. Then, there is an appendix showing the algorithms proposed for each topology studied above. Next, there is a section explaining the meaning of the acronyms being used. After that, the last section displays the bibliography being used when building up this thesis.

### Chapter 2

### Main pillars and related work

This work is about getting a formal algebraic modelling of a fog computing architecture, which is based on some different pillars to be presented herein.

### 2.1 Computing, cloud and fog

First of all, it is to be noted that the world of computing undertakes significant technological developments on a regular basis, thus enhancing the way they operate, as well as gaining compactness and efficiency, whilst reducing cost and power consumption [143]. Therefore, each major improvement induced a new change of paradigm when it comes to how computers work, hence, that fact brought up a new generation of computers.

Initially, it is widely accepted that the first electronic digital computers are considered to be part of the first generation of computers appeared in the 1940s in the context of World War II and the corresponding postwar, which were based on *vacuum tubes* to process information and *binary code* was used to interact with hardware.

Later on, a new generation emerged in the late 1950s with the creation of the first Operating System (OS), along with the use of transistors for information processing, which led to the appearance of faster and more reliable computers. Besides, the use of symbolic languages like assembly prevailed instead of binary code, and even the first high-level programming languages were launched, such as Cobol and Fortran.

Afterwards, in the middle 1960s, another generation kicked off with the use of integrated circuits, also known as *microchips*, along with the appearance of the first instances of OSs being multitask, multiuser, multiprocessor or real-time, as well as the first computer networks, which required manual intervention to accomplish file sharing. It is to be noted that *Unix*, which is the basis of most current OSs, was designed at that time.

Later on, in the early 1970s, a new generation arose due to the invention of mi-croprocessors, those being able to integrate much more circuits into a single chip,

which led to the development of both microcomputers and supercomputers, where

the former popularized the use of personal computers, whilst the latter were devoted

to problems needing intensive calculations. Furthermore, it is to be said that core

developments in nowadays computing systems were made in this period, such as the

creation of C programming language and the Transmission Control Protocol / Internet Protocol (TCP/IP) practical model and Open Systems Interconnection (OSI)

reference model for network transmissions.

Eventually, the current generation is supposed to have been started in the middle 1980s, where diverse artificial intelligent technologies are being implemented in both hardware and software to try to improve different problem-solving skills, with the target of ever achieving more complex and accurate solutions. It is to be said that the vast majority of current OSs, programming languages, services, applications, network solutions, security designs and software developments are included therein.

Focusing on the way computers work, it is to be noted that all previous stages did it in a centralized way, meaning that each individual computer ran its own tasks. This fact is also known as *monolithic computing*, regardless whether they only support a single user at a time or multiple users through time sharing techniques.

However, in the last stage, the continuous rising in the power of microprocessors and the speed of Local Area Network (LAN) made possible the *distributed computing*, where hardware or software components may be located in different computers being interconnected and communication among them is undertaken by means of message passing techniques. This way, distributed systems permit to cope with ever higher load requirements and performances, thus outperforming centralized systems [54].

Some of the main features of such systems are concurrency, as tasks are executed in a simultaneous manner as opposed to a sequential one, the need of a common time for coordination and synchronization purposes, the failure tolerance in computers related to either its hardware, software or network components, the variability of the system structure, which may change during the execution time, and even the incomplete view of the whole system from each individual computer.

Different architectures are allowed in distributed systems, where maybe the most typical one is the client-server, also known as master-slave, where a client requests a resource or service being located on the server, which in turn provides it back to the client through a response. Some well known protocols of this architecture may be Hypertext Transfer Protocol (HTTP) protocol for web browsing, Simple Mail Transfer Protocol (SMTP) and Post Office Protocol revision 3 (POP3) protocols for email exchanging or File Transfer Protocol (FTP) protocol for file transferring.

Furthermore, peer-to-peer is also a typical architecture, where both entities establishing a communication channel may act as either a client or a server, depending on which is the requester and which is the provider of a specific resource. Some well-known examples of this architecture may be file sharing, Voice over IP (VoIP) services, videoconferencing applications or virtual currencies like bitcoin.

Additionally, distributed systems may be found in most types of wired and wireless telecommunication networks, as well as a wide range of network applications, real time process control for industrial automation and flight control. Furthermore, parallel computing may also be cited, where a task is divided into similar subprocesses to be run simultaneously, whose results are combined upon completion.

In that sense, multicore and multiprocessor keep the processing within the same computer, where the former implies a processor having more than one independent processing unit working at a time in a single Central Processing Unit (CPU) and the latter does more than one CPU working simultaneously.

On the contrary, cluster and grid share the processing among different computers, where the former implies that each node is homogeneous and performs the same task as a unique unit, whilst the latter states that all nodes may be homogeneous or heterogeneous and performs the same of a different task.

#### 2.1.1 Cloud and Fog computing

A special instance of parallel computation called *cloud computing* needs to be cited, also referred to as cloud [223]. It may be seen as on-demand computing resources, typically related to storage or computing power, being offered over a network connection. This way, many services might be available such as file saving and restoring, online application executing, remote data processing, repository managing or collaborative environment working, all being delivered on an ad hoc basis.

Clouds may be classified into three main categories, such as public cloud, private cloud and hybrid cloud. As per the first one, it is dedicated to anyone and it is delivered through the Internet, which may or may not require an access fee, then, regarding the second one, it is restricted only to a company, being offered with different levels of access to employees, providers and clients, and finally, with respect to the third one, it combines both clouds in order for the companies to keep with both the availability requirements and the data protection legislation.

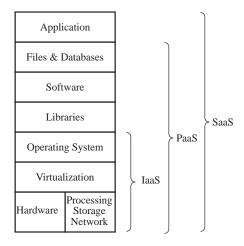

It may be said that the number of as-a-service types offered are growing by the day, even though the most well-known models of cloud are the following:

- Infrastructure as a Service (IaaS): it permits to rent tailor-made virtualized hardware, by choosing the number of processors, Random Access Memory (RAM) memory and storage space, as well as the OSs.

- Platform as a Service (PaaS): it permits to rent development platforms, by choosing software development tools and data base managers, leaving out hardware and software resources.

- Software as a Service (SaaS): it permits to rent a specific enterprise software and some determined space for the data associated to it, permitting the access through any device, regardless its type.

- IT as a Service (ITaaS): it permits to rent virtualized IT services according to the needs and business model of each organization, chosen on demand.

Besides, those different types of cloud services models may involve diverse conceptual blocks within a computing server [27], as shown in Figure 2.1.

Figure 2.1: Cloud service models.

Therefore, it may be said that cloud computing offers a new model which may be customized for each kind of user and situation, as it allows ubiquity, different levels of virtualization and on-demand scalability. This way, the main benefits when adopting cloud services are cost reduction, including hardware and software acquisition and maintenance, enhanced security as cloud premises implement high-end hardening measures and reliability in the event of potential shortages due to backup policies.

According to the aforementioned characteristics, it may appear that cloud computing might be an interesting candidate for providing services to low-resource computing devices, as most of their tasks could be derived to the cloud. In this context, IoT may be described as the aggregation and interconnection of physical objects through the Internet by means of integrated sensors and specific software in order to forward data on to some servers or systems. In other words, IoT may be seen as the connection of regular objects to the Internet so as to analyze the data they provide [141].

It may be noted that basically any physical device, such as domestic, industrial or any other kind, might be connected to the Internet, hence leading to a hyperconnected scenario where the physical and the virtual worlds may cooperate, allowing for the deployment of digitalization solutions or cyber physical systems. This is possible thanks to some recent advances in diverse technologies, such as low-cost and low-power sensors, machine learning, data analytics, big data and artificial intelligence.

With respect to the architectures appropriate for IoT networks, it is to be considered that IoT devices have constraint features regarding processing, storage, memory, bandwidth and power consumption. Therefore, it may seem clear that the use of a central server in order to collect and redistribute all messages among IoT devices might be the ideal solution, as they may minimize the amount of resources needed.

In this context, the central server, also known as broker, may register all IoT devices, as well as it may receive all the messages sent from the source IoT devices, and in turn, it may forward all those message on to the destination IoT devices, according to some predefined criteria. Hence, it could be said that the broker might act as the hub in a star topology, whereas the IoT devices might act as the spokes.

Furthermore, the main approach followed by IoT communications is called Publisher/Subscriber (Pub/Sub), where a software or hardware agent in an IoT device called the publisher, which usually comes equipped with some kind of sensor to measure the environment, gets a measure from it and sends a message with a certain topic to the broker, which in turn, forwards it on to the agents in all other IoT devices being subscribed to that topic, called the subscribers, which usually come equipped with some sort of actuator to act on the environment upon the messages received.

Moreover, there are two ways to implement the message pattern of Pub/Sub. The first one is called message queue, where the broker creates a specific queue of messages of each subscriber, which will be displayed when it gets connected, as it happens in an online forum. Otherwise, the second one is called message service, where the broker forwards messages on as they get in, hence if a subscriber is not connected, it will not receive such a message, as it happens in an online chat. Anyway, the most popular Pub/Sub protocol is Message Queue Telemetry Transport (MQTT), which works according to the message service way, but having some message queue features.

Focusing on the features of IoT devices and how their communication protocols work, it may be clear that cloud computing might not be the optimal solution, as their resource constraints regarding bandwidth and computing power may not make them feasible due to excessive latency and jitter issues because of the overdue time elapsed when sending messages to the cloud and receiving them back according to IoT needs. Besides, the same reasoning applies to communications in real time.

However, those drawbacks associated to cloud environments might be overcome if the remote computing facilities may get closer to the end users, as the time elapsed may get considerably reduced. For that reason, an extension of cloud computing was designed where the computing facilities were located just at the edge of the network, which was called fog computing [31]. That way, each IoT device may get an associated computing resource located on a host within the fog facility, hence accounting for very short values of latency and jitter [197].

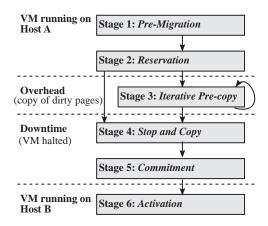

On the other hand, it is to be noted that many IoT devices may be moving around, which are known as moving IoT devices. In this sense, it might be necessary to migrate their computing resources located in a certain physical host within the fog DC to another physical host being closer to the current location of the IoT device [39]. If those remote computing resources are considered to be a VM for simplicity purposes, regardless the fact that those may be a VM, a docker container or another type, then that migration process may be called VM migration and takes place from a source host to a destination host, where the associated VM goes through one of the shortest internetworking paths available between both hosts.

In other words, users getting into a fog environment have some computing assets allocated [109], which are situated within any of the hosts being part of the fog architecture [153]. Those computing resources may usually be VMs, but may also have other forms [14], such as containers or dockers. Additionally, it is to be mentioned that the computer power of the asset can also be allocated in alternative fog environments, such as Arduinos, Raspberry Pis, smartphones, tablets or computing facilities in cars.

Nevertheless, within the context of this thesis, a VM will be referred to as any computing asset allocated within a host being part of a DC, and as such, those VMs might be migrated from one host to another in order to keep them as close as possible to their corresponding associated users when they move around [98].

Regarding fog computing, it may be considered as an extension of cloud computing which brings the computer assets closer to the edge of the network [126]. It is to be noted that cloud deployments have been around for a while and, at this stage, it

may well be said that this technology is totally integrated into our ordinary life, as cloud deployments account for many types of remote computing systems and storage capacities being used by a great deal of users on a daily basis.

Likewise, it may be said that cloud computing has contributed to achieve ubiquity related to computing assets [32], in a sense that those do not need to be next to the end user any more, but they may be located anywhere, as long as there is a necessary connection to get there. Some examples of popular cloud solutions regarding computing services [55] are Amazon Web Services, Microsoft Azure or Google Cloud Platform, whereas some instances of popular cloud storage solutions [50] are iCloud, Dropbox or Box.

However, those advantages turn into disadvantages when dealing with some specific conditions, such as real time scenarios or resource-limited devices [236]. The former case involves a reduced response time [117], which may not be enough for devices sending their requests up to the cloud and waiting to get a response back out of it [217], depending on the distance and the available bandwidth [109].

The latter case deals with scenarios with devices having limited resources, such as computing capacity, RAM memory scarcity, storage shortage, bandwidth insuffiency or power undersupply [218]. The typical scenarios for this conditions may be IoT devices, although others may also be affected.

Therefore, cloud paradigm has been extended in order to cope with the aforesaid situations and has evolved to fog paradigm, also known as fog computing [53]. This means that computing resources are located at the the edge of the network, thus, being far closer to the end user [63]. Hence, fog environments permit remote computing in the aforesaid scenarios, namely, real time implementations and IoT deployments, as it takes far less latency, jitter and bandwidth to reach the remote computing resources than it would if cloud facilities are used [237].

It is also to be considered that fog deployments are composed of a bunch of servers, those being interconnected by some switches, which are organized according to a certain topology within the fog domain [11]. Those servers are usually called hosts, as they basically *host* the remote computing resources assigned to the users within the fog environment, where those computing assets are generically called VMs, even

though other types may arise, as stated before [232]. Obviously, each host may keep several VMs, depending on their sizes.

Another point to be taken into account is that fog premises are usually connected to some cloud deployment [52], thus allowing it to be a backup system for the fog, hence permitting a VM to be diverted into the cloud in case there are no enough resources to allocate a certain VM in a host being part of the fog [28]. It may seem clear that the capacity of the resources within a cloud may well be far bigger than that of a fog, just because of its geographical scope.

Additionally, on the one hand, it is to be noted that the fog environment is usually tied to the Open Fog Reference Architecture [142] (adopted by the Institute of Electrical and Electronics Engineers (IEEE) as the official standard for fog computing), containing many applications, such as surveillance, autonomous vehicles or smart cities [3]. On the other hand, Multi-Access Edge Computing (MEC) is defined by the Industry Specification Group within the European Telecommunications Standards Institute (ETSI) [58], including many applications, such as caching scenarios, location services or extended reality scenarios, such as Virtual Reality (VR), Augmented Reality (AR) or Mixed Reality (MR) [239].

As a side note, it is also important to note that both MEC, which is also known as edge computing [125], and fog may both be seen as instances of distributed resources being located on the edge of the network [75] and being able to connect to external cloud nodes. However, the former puts the focus on the execution of computing processes close to end users, whilst the latter does it on the overall architecture [24].

Nonetheless, in both cases, communications between hosts and computing assets at the edge of the network do usually take place by means of mobile and wireless communications [8], which is called as Radio Access Network (RAN), whose performance may well be enhanced by the rise of the next generation networks, such as 5th Generation of Cellular Networks (5G) and the 6th Generation of Wireless Fidelity (WiFi-6) [146], and those being under development now, such as 6th Generation of Cellular Networks (6G) [235] and the 7th Generation of Wireless Fidelity (WiFi-7) [110]. However, when dealing with fog, communications with cloud facilities may also involve the use of wired communications, such as twisted pairs and mostly fiber optics.

Moreover, it may be considered that fog does usually imply a small DC, whist MEC might not be the case. Regarding the DCs, their size ought to be according to the amount of users and their workloads expected within the fog domain [229]. Therefore, the capacity of each host might not generally be as high as those implemented in cloud deployments, and likewise, the number of them could not need to be as big [79]. Hence, the topologies required for such DCs may well be quite simple in most deployments, thus allowing for easier designs, although in some cases, it might be a bit more complex, depending on expected amount of users and traffic [231].

Focusing on IoT deployments, they perfectly fit the features of fog computing [122], where communications take place between each of those devices and a central server called broker [221]. This entity may have enough resources to act as a hub for all communications with all the IoT devices [199], while maintaining a register of those being connected at any time [130].

Traditional networking protocols working with paradigms such as client-server or peer-to-peer do not match the aforesaid behaviour, thus, the central-server paradigm may be put in place [1]. There are different protocols working that way, most of them employing a Pub/Sub approach [193], whilst others use a Remote Procedure Call (RPC) methodology [64]. The main difference between them is that in the former, the central server plays a crucial part, as it manages all of the traffic between publishers and subscribers, whereas in the latter, its role is just to forward the flows of traffic among end users, not to manage them.