Doctorat en Enginyeria Electrònica

Departament D'Enginyeria Electrònica

# Array of microfluidic beam resonators for mass sensing applications - Design, Fabrication and Testing

Doctoral Thesis - July 2016

Salomón Elieser Marquez Villalobos Author

Prof. Laura M. Lechuga Gómez Director Dr. Mar Álvarez Sánchez Co-director

Dr. David Jiménez Jiménez Tutor

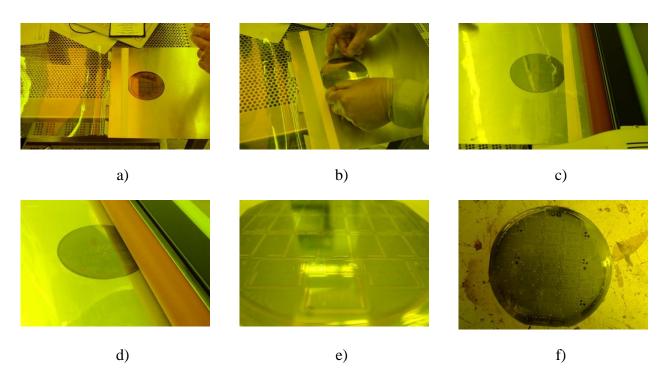

# Chapter 3 Fabrication of HMB devices

Before the batch processing of MEMS devices, a couple of previous tasks must be fulfilled according to the specific requirements and standards inside a cleanroom facility. These tasks encompassed the design and printing of the photolithographic masks and a detailed description of the fabrication steps involved in the definition of the MEMS technology. The photolithographic masks are essential to outline the specific dimensions and features of the microdevices as is the width, length and shape of the resonators along with the microfluidic inlets according to the design proposed in the previous chapter. The manufacturing process included additive and subtractive tasks for removing materials deposited on the silicon substrate in a layer-by-layer fabrication process. Each of the fabrication strategies listed in this Thesis was carefully planned, discussed and verified by the clean room personnel along with the photolithographic masks design to investigate the feasibility to manufacture the HMB resonators technology with high yield and reproducibility. The HMB technology was manufactured at the Large Scale Facility (ICTS) of the IMB-CNM-CSIC.

In this Thesis work, we have developed three approaches to fabricate HMB devices. The first fabrication strategy consisted of both surface and bulk micromachining techniques to fabricate doubly clamped hollowed structures with excellent resonating capabilities, wherein silicon nitride and silicon oxide were used as structural and sacrificial layer, respectively. Instead, in the second fabrication scheme, polycrystalline silicon and doped silicon oxide were employed as structural and sacrificial materials correspondingly. In this approach, the fabrication of HMB devices was simplified by only executing surface micromachining with two photolithographic steps to obtain well-defined and hollowed structures with good filling capabilities. Finally, the purpose of the last fabrication strategy was to diminish the undercutting effect of the released resonators while etching the sacrificial layer observed in the previous fabrication schemes. Additionally, the on-chip integration of polymer-based microfluidics was included to facilitate the micro and macrofluidic interconnections, and packaging of the devices.

# 3.1 Fabrication process of HMB devices of the first generation

# 3.1.1 Mask design

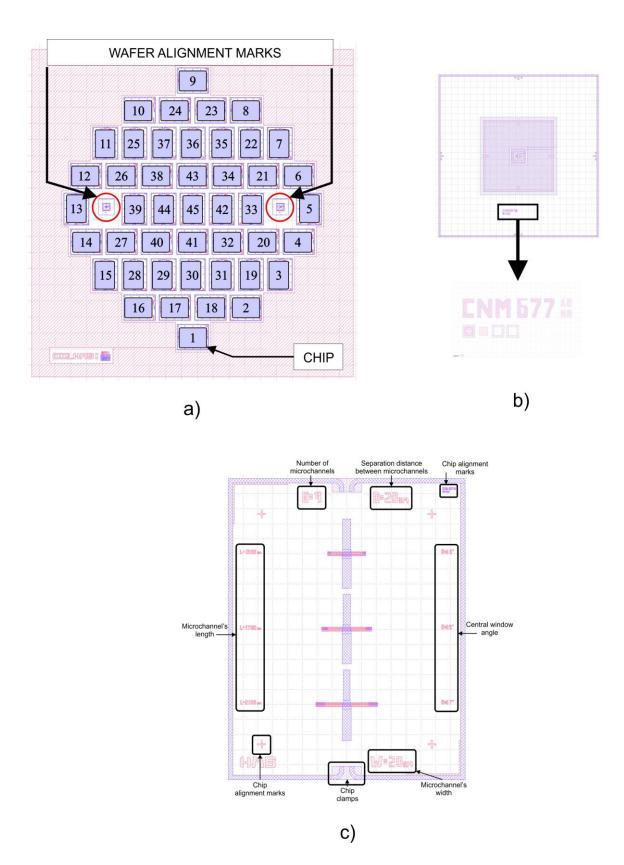

The first batch of photolithographic masks was developed for two fabrication process, named RUN6570 and RUN6829. A set of three soda-lime photomasks, namely CNM677, was drawn in Klayout Software and printed by Compugraphics Company (Spain). The minimum feature size (MFS) for this type of masks was  $1.5~\mu m$ , which complied well with the minimum dimensions required to fabricate our microstructures. Fig. 3-1 shows forty-five devices distributed all over the mask including the doubled size alignment marks located in the center whereby the dimensions of every device are 1~x~0.8~cm. For the step by step fabrication of devices, each mask has the following features:

- Mask CNM677-BRID1. This is the first alignment mask of the fabrication process that defines the following features of the microchannels: length (L), width (W), the number of microchannels in the array (B) and the separation distance between them (D). It also includes unique identification marks for every chip such as number, alignment motives and labels. Fig. 3-1 shows the marks included on each device.

- Mask CNM677-HOLE2. This mask is aligned with respect to CNM677-BRID1 mask to

define the effective length of the resonators. It also uncovers the sacrificial layer by

outlining access holes at both ends of the microchannels and includes an outer frame to

release the devices from the substrate.

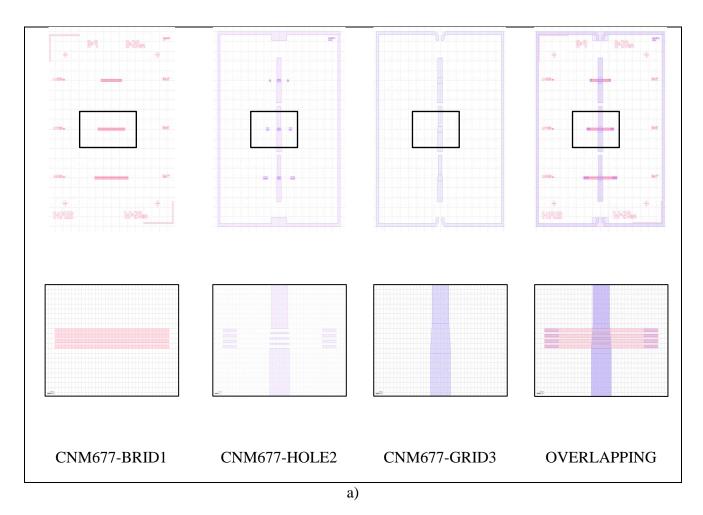

- Mask CNM677-GRID3. This mask is aligned with respect to CNM677-BRID1 mask using the double-sided alignment marks to release the structures from the silicon wafer during the bulk micromachining. Fig. 3–2 shows the alignment process of the three masks along with their corresponding alignment marks.

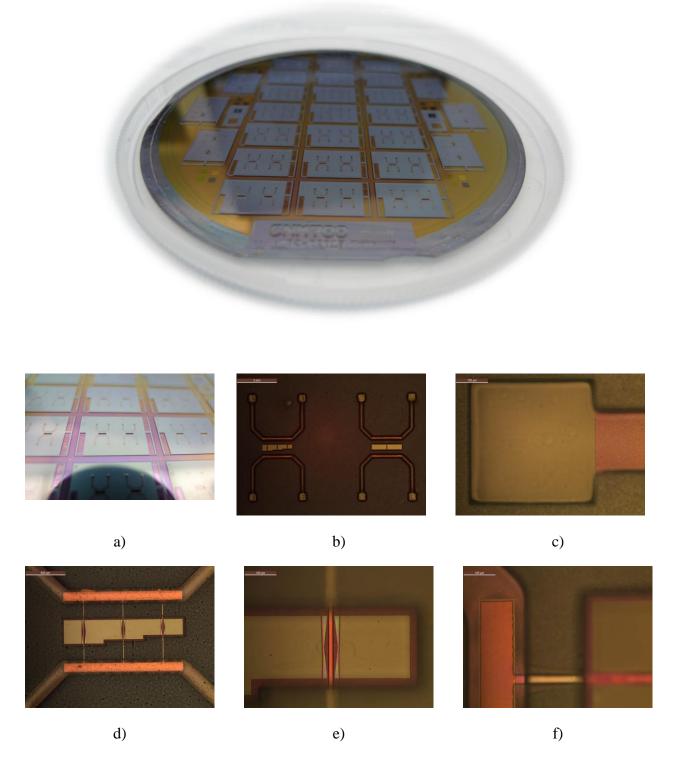

Fig. 3-1. a) Distribution of devices all over the mask design which has 5 inches in size, b) double-sided wafer alignment marks located in the center at a separation distance of 55 mm and c) main description labels that identify the fabrication features for each device.

Fig. 3–2. a) From left to right, consecutive alignment marks that define the HMB devices: microchannel dimensions, microfluidic inlets, effective length of the resonators and outer frame for chip release. A zoom-in of the marks indicates a detailed description of the microchannels masks and b) the principal alignment marks of each fabrication step.

#### 3.1.2 Fabrication process at cleanroom facilities

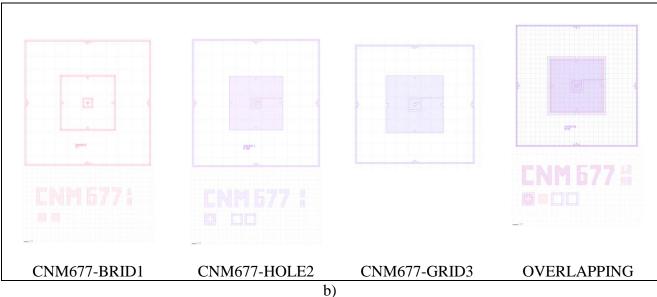

Fig. 3-3 shows an overview of the fabrication steps and a general view of the device prototype. The process began by using silicon wafers type P of 300  $\mu$ m thick and resistivity of 4-40 ohm-cm as based substrates. A general cleaning of the wafers with piranha solution removed any organic components. Next, a 500 Å layer of SiO<sub>2</sub> was thermally grown at 1000°C on both sides of the wafers (step 4). The silicon dioxide dielectric layer improved the adhesion of the following deposited layers and isolated the devices from the silicon substrate as required for the release of the final structures. From here, three groups of wafers were established to build microstructures with different dimensions based on the thickness of the structural and sacrificial layer. For the first batch of wafers (1-3), a 0.5  $\mu$ m layer of Si<sub>3</sub>N<sub>4</sub> was deposited by Low-Pressure Chemical Vapour Deposition (LPCVD).

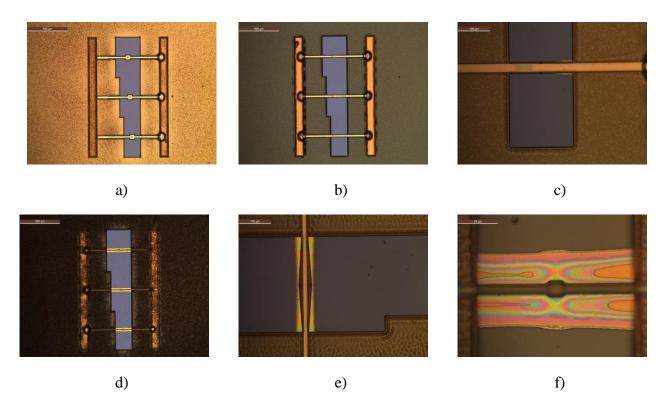

Fig. 3-3. On top, overview of a fabricated chip of the first generation of HMB devices. On bottom, a summary is presented for the most important fabrication steps in the procedure that include: a) initial wafer, b) patterning of the sacrificial layer, c) - d) enclosing and aperture of the microchannels, e) etching of the sacrificial layer and f) releasing the resonators from the silicon substrate.

Similarly, for the next group of wafers (4-6), a 0.7  $\mu$ m layer of Si<sub>3</sub>N<sub>4</sub> was deposited by LPCVD (steps 5&6). And for the latter group, a 1  $\mu$ m layer of Si<sub>3</sub>N<sub>4</sub> was deposited by Plasma-Enhanced Chemical Vapour Deposition (PECVD) to comply with the depth of the layer (step 7). The average thickness value was verified for each Si<sub>3</sub>N<sub>4</sub> deposited layer by interferometric measurements in the visible range, with the Nanospec equipment (step 8), resulting the following mean values: 4915.40  $\pm$  73.71 Å (wafers 1-3), 6981.33  $\pm$  100.39 Å (wafers 4-6) and 9518.60  $\pm$  153 Å (wafers 7-9).

| Step | Code                                                                         | Description                                                                     | Wafer |  |  |  |

|------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------|--|--|--|

| 1    | INICIO                                                                       | Preparation to begin RUN                                                        | 1-9   |  |  |  |

| 2    | MARC-PXA                                                                     | Marking of silicon wafers                                                       | 1-9   |  |  |  |

| 3    | NET-GEN                                                                      | General Cleaning                                                                | 1-9   |  |  |  |

|      |                                                                              |                                                                                 |       |  |  |  |

| 4    | OSC-0500                                                                     | Thermal grown of 500 Å of SiO <sub>2</sub> at 1000°C                            | 1-9   |  |  |  |

|      |                                                                              |                                                                                 |       |  |  |  |

| 5    | DNIT-ING                                                                     | LPCVD deposition of 0.5 μm of Si <sub>3</sub> N <sub>4</sub>                    | 1-3   |  |  |  |

| 6    | DNIT-ING                                                                     | LPCVD deposition of 0.75 μm of Si <sub>3</sub> N <sub>4</sub>                   | 4-6   |  |  |  |

| 7    | DAMINTXX                                                                     | PECVD deposition of 1 μm of Si <sub>3</sub> N <sub>4</sub>                      | 7-9   |  |  |  |

|      |                                                                              |                                                                                 |       |  |  |  |

| 8    | MES-NANO                                                                     | Thickness measurement of Si <sub>3</sub> N <sub>4</sub> with Nanospec equipment | 1-9   |  |  |  |

| 9    | NETG-SIM                                                                     | General simple cleaning                                                         | 1-9   |  |  |  |

|      | Si SiO <sub>2</sub> Si <sub>3</sub> N <sub>4</sub> Doped SiO <sub>2</sub> Al |                                                                                 |       |  |  |  |

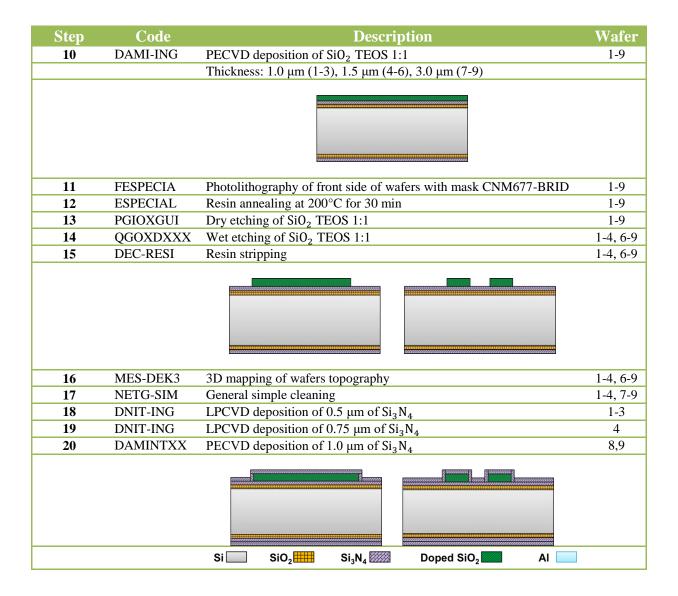

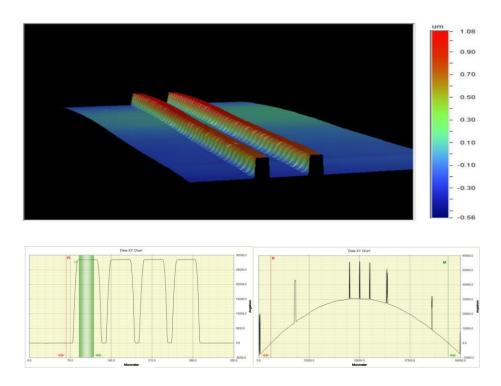

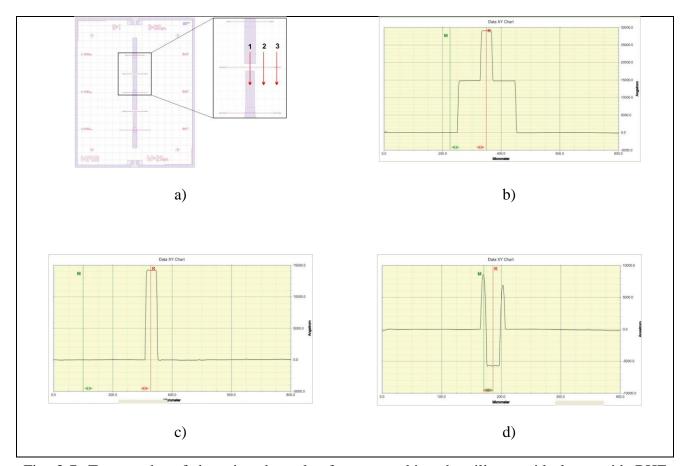

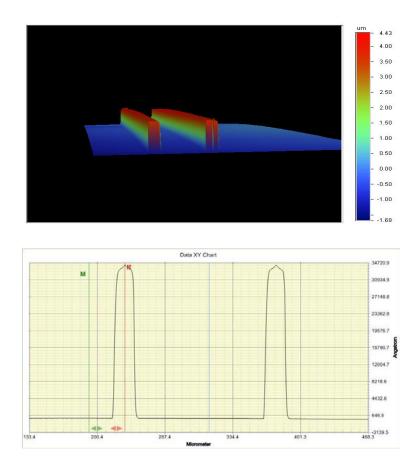

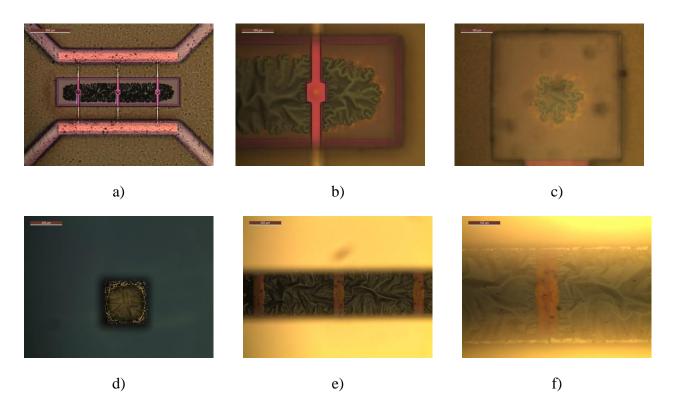

After a simple cleaning of wafers, the  $SiO_2$  TEOS 1:1 (Tetraethyl Orthosilicate) sacrificial layer was deposited by PECVD (step 10). For each group of wafers, the thickness of the sacrificial layer was  $9828 \pm 362$  Å,  $14620 \pm 378$  Å and  $28958 \pm 400$  Å, respectively. To achieve a 3 µm thickness, it was necessary to do three layer depositions of 1 µm thick each. During this process, particle traces appeared on the surface of the wafers along with other physical defects, which faded away after a cleaning with piranha solution over each deposition step. Next, vertically sidewalls of the sacrificial layer were patterned by soft-contact photolithography (step 11) and Reactive Ion Etching (RIE) in step 13. Any rest of the sacrificial layer was removed from  $Si_3N_4$  using Buffered Hydrogen Fluoride solution (BHF: NH4F + HF + HzO) for approximately 60 s (step 14). Next, the topography of the microchannels was characterized with a Dektak 150 profilometer (step 16) to determine the real microchannel dimensions, see Fig. 3-4. In here, the corner sides of the microchannels were slightly smoothed during the wet etching step and also the center of the wafers showed a relatively compressive stress.

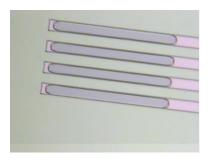

After a simple cleaning of the wafers, a second  $Si_3N_4$  layer was deposited to enclose the structures (steps 18, 19 and 20). The thickness of each deposited layer was assigned according to each group of wafers, as described in early steps, and taking into account the symmetry of the microchannels. The  $Si_3N_4$  thickness of each group of wafers was  $4993 \pm 71$  Å,  $6902 \pm 104$  Å and  $10038 \pm 88$  Å, respectively. Afterwards, the effective length of the doubly clamped beams and the fluidic inlets of the microchannels were defined by soft-contact photolithography (step 21). To completely cover the microstructure topography of approximately 5  $\mu$ m height, a 6  $\mu$ m thick photoresist was deposited. The aperture of the exposed areas was etched by a dry etching process of the  $Si_3N_4$  top layer until exposing the underlying thermally grown  $SiO_2$  (step 23). Then, the protective photoresist was stripped from the wafers by oxygen plasma. Fig. 3-5 shows the revealed silicon dioxide layer at both ends of the microchannels and the outlined effective length of the beams.

Fig. 3-4. (Top) 3D structural characterization of the patterned microchannels with a profilometer. Edges of the microstructures are slightly smoothed after the wet etching step with BHF solution. (Bottom) Topography of an array of four microchannels of 35  $\mu$ m width. The wafers present a compressive stress along the "x" and "y" axis after the deposition of the  $Si_3N_4$ .

| Step | Code     | Description                                                               | Wafer        |

|------|----------|---------------------------------------------------------------------------|--------------|

| 21   | FOTO-ESP | Photolithography of the front wafers side with mask CNM677-               | 1, 2, 3, 4 & |

|      |          | HOLE2                                                                     | 8            |

| 22   | ESPECIAL | Resin annealing at 200°C for 30 min                                       | 2, 3, 4 & 8  |

| 23   | GGIR-ING | Dry etching of Si <sub>3</sub> N <sub>4</sub>                             | 2, 3, 4 & 8  |

| 24   | DEC-RESI | Resin stripping                                                           | 2, 3, 4 & 8  |

| 25   | GHUM-ESP | Wet etching of SiO <sub>2</sub> TEOS 1:1 sacrificial layer                | 2, 3, 4 & 8  |

| 25b  | MES-DEK3 | 3D mapping of wafers topography                                           | 2, 3, 4 & 8  |

| 250  |          | SiO <sub>2</sub> Si <sub>3</sub> N <sub>4</sub> Doped SiO <sub>2</sub> Al | 2, 5, 1 & 0  |

Fig. 3-5. Aperture of the Si<sub>3</sub>N<sub>4</sub> structural layer to uncover the embedded sacrificial layer of silicon oxide. Also, the photo shows the specific width and length of the resonators in the central window.

The following steps consisted of removing the embedded sacrificial layer to constitute hollow cavities using a wet etching process. To set the optimum etching time of the sacrificial layer, not only the length of the largest structure (1480 µm) was taken into account but also the etch directions coming from the two openings located at both ends of the microchannels. Thus, it was determined that the effective sacrificial layer length to be etched was approximately 740 µm. For this task, two etchant solutions were considered based on their etching ratios shown in Table 3-1. If the BHF solution is employed to dissolve the sacrificial layer, then it is necessary to immerse the wafers for 3470 min, which will cause an over-etching of the Si<sub>3</sub>N<sub>4</sub> of approximately 26 µm. Instead, if the HF 49% acid is used, a 20 µm over-etching of the Si<sub>3</sub>N<sub>4</sub> will be expected for the 210 min required to etch the sacrificial layer. In sum, for this fabrication process, the selectivity between the sacrificial and structural materials was very low, and therefore it was not possible to create hollowed microfluidic channels. Nevertheless, the wafers were submerged in the BHF solution at different times, ranging from 8 to 12 min, to study the wet etching effects (step 25). The topography of the microchannels was characterized with the profilometer (step 25b) to determine the modifications of the microchannel dimensions, as can be seen in Fig. 3-6 and Fig. 3-7.

Table 3-1. Etching ratios of several materials at the cleanroom facilities of IMB-CNM

| Material                             | BHF (µm /min) | HF 49% acid ( μm /min) |

|--------------------------------------|---------------|------------------------|

| PSG                                  | 0.5671        | 20.200                 |

| SiO <sub>2</sub> PECVD TEOS (1:1)    | 0.2132        | 3.5000                 |

| SiO <sub>2</sub> PECVD TEOS (1:2)    | 0.1605        | 2.4000                 |

| Si <sub>3</sub> N <sub>4</sub> LPCVD | 0.0007        | 0.0125                 |

| Si <sub>3</sub> N <sub>4</sub> PECVD | 0.0076        | 0.0980                 |

| SiO <sub>2</sub> PECVD               | 0.2132        | 3.0000                 |

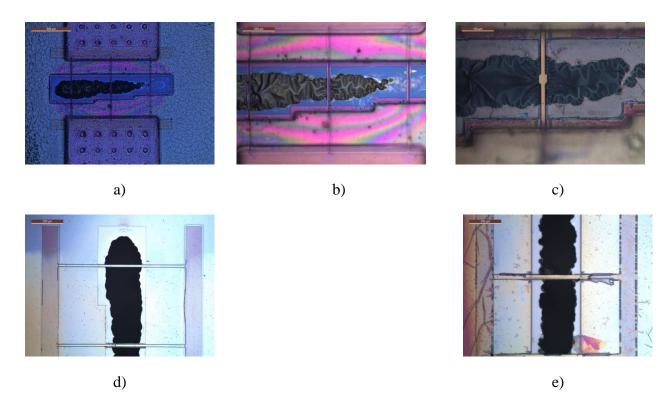

Fig. 3-6. Aspect of the microchannels after the wet etching of the sacrificial layer in which the structural layer was etched due to the low selectivity between the materials.

Fig. 3-7. Topography of the microchannels after wet etching the silicon oxide layer with BHF solution. Three features were captured by the profilometer at different locations of the microchannels. Besides, the structural layer was affected by the etchant solution due to the poor selectivity of both materials.

Despite the previous results, the fabrication process continued to probe the feasibility to release the structures from the substrate. At this point, several wafers were broken due to the exceeding residual stress of the  $Si_3N_4$  layers, which increased with the thickness of the layers. For example, the wafers of the second group (4, 5 and 6) were removed from the manufacturing process because

they fractures and imperfections across its surface. Thereafter, the two deposited layers of  $Si_3N_4$  from the backside of wafers were removed using RIE until exposing the underlying thermally grown  $SiO_2$  (step 27). In this step, a 6  $\mu$ m resin was deposited on the front side of the wafers to protect the microstructures. Afterwards, a 0.5  $\mu$ m layer of aluminium was deposited on the backside of wafers using electron beam evaporation (EBV) in step 29. This aluminium layer was used as a mask when releasing the structures from the front side of wafers by a deep silicon etching process (DRIE).

| Ctor | Codo                 | Description                                                               | Wafan       |

|------|----------------------|---------------------------------------------------------------------------|-------------|

| Step | Code                 | Description                                                               | Wafer       |

| 26   | FESPECIA<br>CCIP INC | Deposition of 6 µm of resin                                               | 2, 3, 4 & 8 |

| 27   | GGIR-ING<br>DEC-RESI | Dry etching of Si <sub>3</sub> N <sub>4</sub> from the backside of wafers | 2, 3, & 8   |

| 28   | DEC-RESI             | Resin stripping                                                           | 2, 3, & 8   |

|      |                      |                                                                           |             |

| 29   | MZ550ING             | Deposition of 0.5 μm of Aluminium                                         | 2, 3, & 8   |

|      |                      |                                                                           |             |

| 30   | FOTO-ESP             | Photolithography of backside of wafers with mask CNM677-GRID              | 2, 3, & 8   |

| 31   | QUAD-ESP             | Dry etching of 0.5 μm of Aluminium from back side of wafers               | 2, 3, & 8   |

| 32   | PGIOXXXX             | Dry etching of 50 nm of SiO <sub>2</sub> from the backside of wafers      | 2, 3, & 8   |

|      |                      |                                                                           |             |

| 33   | P601DEEP             | Deep dry etching of 295 μm of silicon                                     | 2, 3, & 8   |

|      |                      |                                                                           |             |

| 34   | QGALCXXX             | Wet etching of 0.5 μm of aluminium                                        | 2, 3, & 8   |

| 35   | DEC-RESI             | Resin stripping                                                           | 2, 3, & 8   |

| 36   | MSTMHXXX             | Wet etching of silicon with TMAH 25% @ 80°C                               | 2, 3, & 8   |

|      |                      |                                                                           |             |

| 37   | MST-ESP              | Wet etching of 500 Å of thermal $SiO_2$                                   | 2, 3, & 8   |

|      |                      |                                                                           |             |

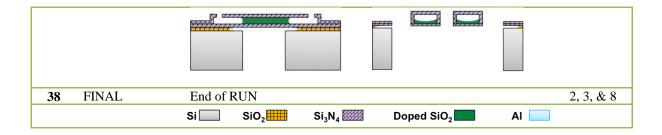

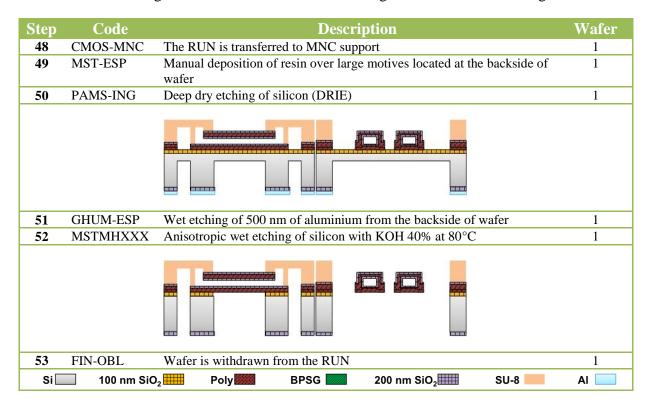

Rectangular marks underneath the resonators were defined at the backside of the wafers using soft-contact photolithography (step 30) and RIE. The aluminium material (step 31) and after that the thermally grown SiO<sub>2</sub> (step 32) were removed until uncovering the silicon substrate. Next, a helium pressure of 500 Pa was adjusted in the Alcatel 601E equipment chamber to start the DRIE process of silicon (step 33). For each wafer, an average etching time of 25 min was necessary to remove approximately 275 µm of silicon. After stripping the protective resin, the aluminium layer was removed using a diluted acid etchant for 4 min (step 34). The remaining 25 µm of silicon material were etched using a TMAH 25% (Tetramethylammonium Hydroxide) solvent at 80°C for approximately 1h and 50 min until revealing the thermally grown SiO<sub>2</sub> (step 36). Finally, the SiO<sub>2</sub> layer was removed by immersing the wafers for 45 s in BHF solution until releasing the microstructures (step 37).

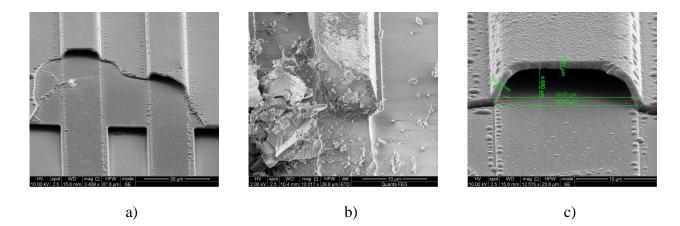

#### 3.1.3 General overview and evaluation of the fabrication process

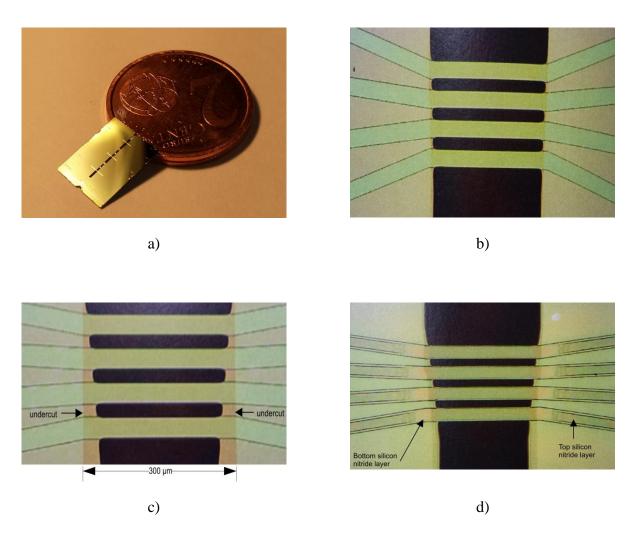

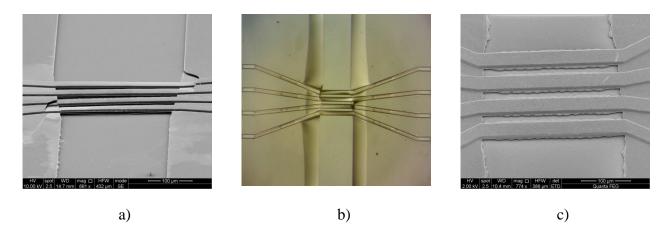

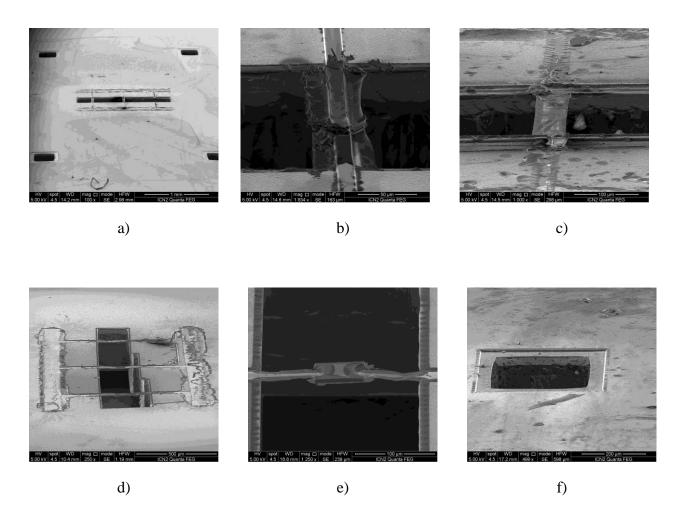

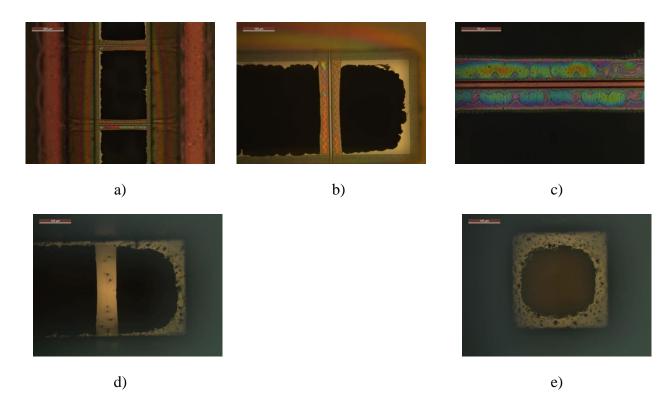

Fig. 3–8 shows a final device fabricated according to the first microfabrication approach. After ending the fabrication process, there were only three wafers left (2, 3 & 8) with half the number of chips (24) completely released. Devices with parallel alignment respect to the flat of the wafer were only released from the substrate because the last mask (CNM677\_GRID3 mask), used to release the structures, was printed backwards and thus, some of the motives were overlapped. We noticed an increase in the residual stress of the wafers in both the substrate and the deposited film. Particularly for wafers with silicon nitrate deposited by LPCVD since the deposited silicon nitride layer was thicker. The excessive film stresses led to deformation and cracking of the microchannels which in the end produced unusable devices. Furthermore, the structural layer of devices from wafer 8 was highly affected during the wet etching process of the sacrificial layer. The etching ratio of the silicon nitride deposited by PECVD (7.6 nm/min) was tenfold higher than that deposited by LPCVD (0.7 nm/min), and therefore it was more easily affected by the BHF solution. Fig. 3–8d shows the uncovered sacrificial layer after the wet etching process for devices with silicon nitride deposited by PECVD.

On the other hand, devices from wafers 2 and 3 had well-defined structures with slightly tensile residual stress. Nevertheless, at both clamps sides of the beams some devices had undercut. Fig. 3–8c and Fig. 3–8d describe the differences between well-released structures and those with an undercut. The dimensions of the undercut surface complied well with the zone designated for the angular clamping support (up to  $25~\mu m$ ). This can be explained due to the non-uniformity of the DRIE process throughout the wafer. In the center of the wafer, the silicon etching ratio was slower

than that outside the wafer, and therefore during the anisotropic wet etching of the silicon substrate some devices were rapidly released.

Fig. 3–8 a) Final view of a fabricated device using silicon nitride as structural material. b) An array of four suspended silicon nitride beams. c) Undercut produced after releasing the structures from the substrate which depended on the location of the device over the wafer. d) Partial etching of the silicon nitride material for devices with structural layer deposited by PECVD.

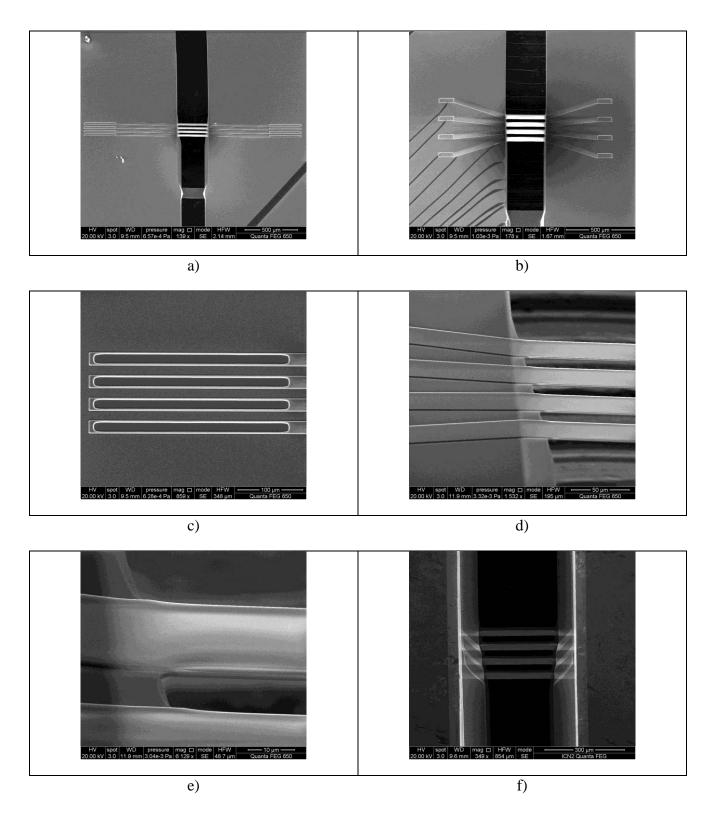

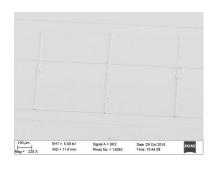

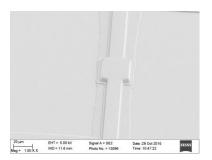

The dry etching process that outlined the effective length of the beams also affected the integrity of some structures, as detailed by the SEM micrographs of Fig. 3–9. The lateral edges of the beams were partially etched uncovering the embedded sacrificial layer for devices with silicon nitride thickness of  $0.5~\mu m$  and  $0.75~\mu m$ . Thus, the alignment of the photolithographic mask (CNM677-HOLE2) resulted challenging to outline features below  $1.5~\mu m$ , as was the case of these edges.

Fig. 3–9. SEM micrographs of a) - c) suspended silicon nitride beams with microfluidic inlets, d) undercut at the clamp region of the microbeams, e) partial etching of lateral walls of the microbeams and f) a bottom view of the beams after the bulk micromachining processes.

# 3.2 Fabrication process of HMB devices of the second generation

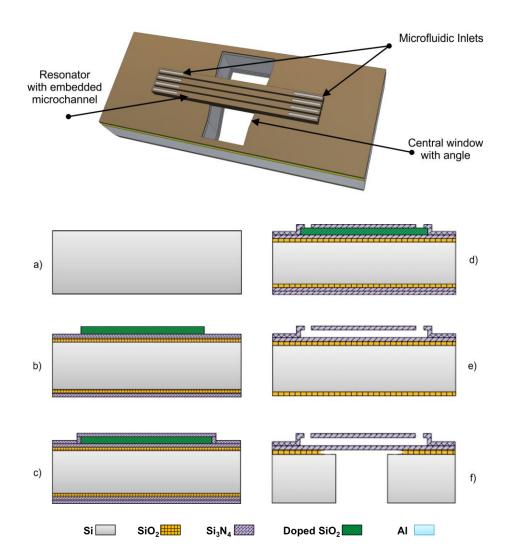

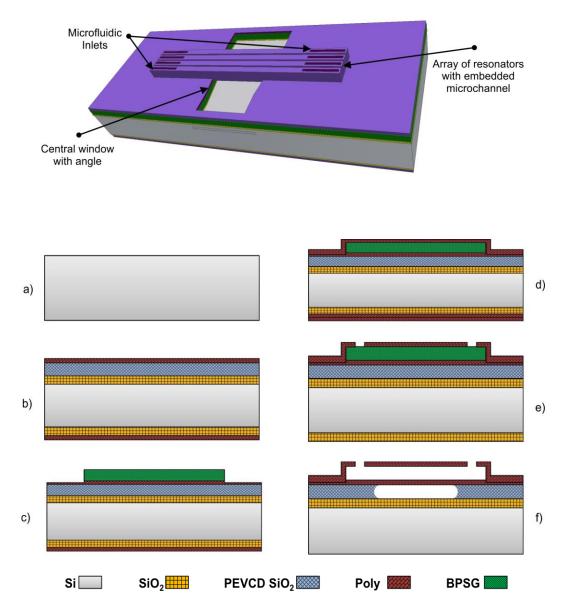

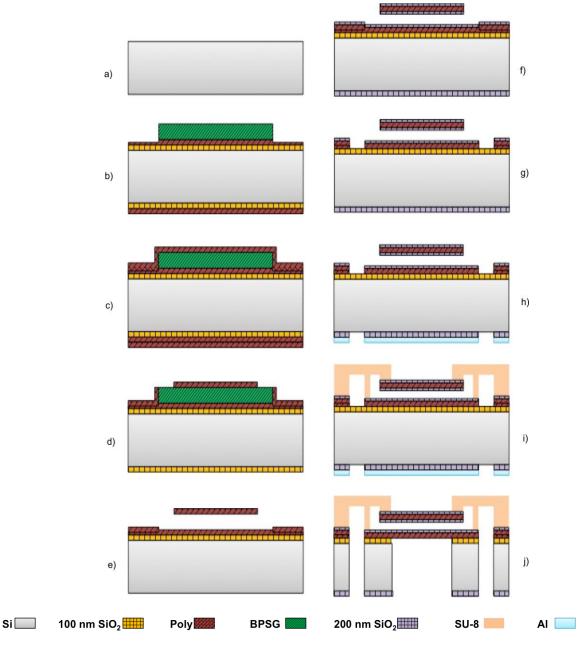

For the second fabrication of the resonators -low cost and well-known- surface micromachining techniques were employed. Fig. 3-10 shows an overview of the final device and the fabrication steps used in this technological process. Hollow microbridges were fabricated using 4-in, type P silicon wafers of 500  $\mu$ m thick, double side polished and with a resistivity of 10-20 ohm-cm. Polycrystalline silicon was used as structural layer and borophosphosilicate glass (BPSG) as sacrificial layer because of their high selectivity and high etching rate of the latter when using HF 49% acid as etchant solution.

Fig. 3-10. (*Top*) single device showing the architecture of the array of polysilicon beams with embedded microfluidic channels. (*Bottom*) a summary of the principal fabrication steps: a) silicon wafer, b) deposition of layers, c) patterning of microchannels, d)-e) channel enclosing and patterning of microfluidic inlets and f) wet etching of the sacrificial layer.

The process began by using three silicon wafers as based substrates. The curvature of the wafers was then measured along the  $0^{\circ}$  and  $90^{\circ}$  axes of the wafers with Dektak 150 profilometer equipment (step 3). This procedure showed a maximum deformation of 3  $\mu$ m in the center of the wafers. After a simple cleaning with piranha solution, a dielectric layer of SiO<sub>2</sub> of approximately 1.5  $\mu$ m thick was thermally grown on both sides of the wafers (step 5). Then, a SiO<sub>2</sub> (TEOS 2:1) layer was deposited by PECVD on top of the wafers until achieving a 4  $\mu$ m thickness (steps 7 and 8). This process was done in two consecutive depositions of 2  $\mu$ m without cleaning the surface of the wafers. The thickness of this layer (4  $\mu$ m) was chosen to avoid stiction while releasing the microstructures from the substrate. The stiction occurs while drying two paralleled and closely spaced microstructures after a wet etching process, which can cause the collapsing of the suspended microstructures due to capillary forces. Measurements with the Nanospec equipment verified that the final thickness of the deposited SiO<sub>2</sub> layer was approximately 53173  $\pm$  951 Å.

| 1 INICIO Preparation to begin RUN 2 MARC-PXB Marking of silicon wafers 3 MES-DEKS Wafer curvature measurement along 0° and 90° axes 4 NET-GEN General cleaning  5 OHC-1M5 Thermal growth of 1.5 μm of SiO <sub>2</sub> at 1100°C 6 NETG-SIM General simple cleaning  7 DAMIOX21 PECVD deposition of 2 μm of SiO <sub>2</sub> TEOS 2:1 8 DAMIOX21 PECVD deposition of 2 μm of SiO <sub>2</sub> TEOS 2:1 9 MES-NANO Measurement of the SiO <sub>2</sub> thickness with Nanospec equipment 10 NETG-SIM General simple cleaning | Step | Code     | Description                                            | Wafer |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|--------------------------------------------------------|-------|

| 3 MES-DEKS Wafer curvature measurement along 0° and 90° axes 4 NET-GEN General cleaning  5 OHC-1M5 Thermal growth of 1.5 μm of SiO <sub>2</sub> at 1100°C 6 NETG-SIM General simple cleaning  7 DAMIOX21 PECVD deposition of 2 μm of SiO <sub>2</sub> TEOS 2:1  8 DAMIOX21 PECVD deposition of 2 μm of SiO <sub>2</sub> TEOS 2:1  9 MES-NANO Measurement of the SiO <sub>2</sub> thickness with Nanospec equipment                                                                                                          | 1    | INICIO   | Preparation to begin RUN                               | 1-3   |

| 4 NET-GEN General cleaning  5 OHC-1M5 Thermal growth of 1.5 μm of SiO <sub>2</sub> at 1100°C  6 NETG-SIM General simple cleaning  7 DAMIOX21 PECVD deposition of 2 μm of SiO <sub>2</sub> TEOS 2:1  8 DAMIOX21 PECVD deposition of 2 μm of SiO <sub>2</sub> TEOS 2:1  9 MES-NANO Measurement of the SiO <sub>2</sub> thickness with Nanospec equipment                                                                                                                                                                      | 2    | MARC-PXB | Marking of silicon wafers                              | 1-3   |

| <ul> <li>5 OHC-1M5 Thermal growth of 1.5 μm of SiO<sub>2</sub> at 1100°C</li> <li>6 NETG-SIM General simple cleaning</li> <li>7 DAMIOX21 PECVD deposition of 2 μm of SiO<sub>2</sub> TEOS 2:1</li> <li>8 DAMIOX21 PECVD deposition of 2 μm of SiO<sub>2</sub> TEOS 2:1</li> <li>9 MES-NANO Measurement of the SiO<sub>2</sub> thickness with Nanospec equipment</li> </ul>                                                                                                                                                  | 3    | MES-DEKS | Wafer curvature measurement along 0° and 90° axes      | 1-3   |

| <ul> <li>NETG-SIM General simple cleaning</li> <li>DAMIOX21 PECVD deposition of 2 μm of SiO<sub>2</sub> TEOS 2:1</li> <li>DAMIOX21 PECVD deposition of 2 μm of SiO<sub>2</sub> TEOS 2:1</li> <li>MES-NANO Measurement of the SiO<sub>2</sub> thickness with Nanospec equipment</li> </ul>                                                                                                                                                                                                                                   | 4    | NET-GEN  | General cleaning                                       | 1-3   |

| <ul> <li>NETG-SIM General simple cleaning</li> <li>DAMIOX21 PECVD deposition of 2 μm of SiO<sub>2</sub> TEOS 2:1</li> <li>DAMIOX21 PECVD deposition of 2 μm of SiO<sub>2</sub> TEOS 2:1</li> <li>MES-NANO Measurement of the SiO<sub>2</sub> thickness with Nanospec equipment</li> </ul>                                                                                                                                                                                                                                   |      |          |                                                        |       |

| <ul> <li>7 DAMIOX21 PECVD deposition of 2 μm of SiO<sub>2</sub> TEOS 2:1</li> <li>8 DAMIOX21 PECVD deposition of 2 μm of SiO<sub>2</sub> TEOS 2:1</li> <li>9 MES-NANO Measurement of the SiO<sub>2</sub> thickness with Nanospec equipment</li> </ul>                                                                                                                                                                                                                                                                       | 5    | OHC-1M5  | Thermal growth of 1.5 μm of SiO <sub>2</sub> at 1100°C | 1-3   |

| <ul> <li>8 DAMIOX21 PECVD deposition of 2 μm of SiO<sub>2</sub> TEOS 2:1</li> <li>9 MES-NANO Measurement of the SiO<sub>2</sub> thickness with Nanospec equipment</li> </ul>                                                                                                                                                                                                                                                                                                                                                | 6    | NETG-SIM | General simple cleaning                                | 1-3   |

| <ul> <li>8 DAMIOX21 PECVD deposition of 2 μm of SiO<sub>2</sub> TEOS 2:1</li> <li>9 MES-NANO Measurement of the SiO<sub>2</sub> thickness with Nanospec equipment</li> </ul>                                                                                                                                                                                                                                                                                                                                                |      |          |                                                        |       |

| 9 MES-NANO Measurement of the SiO <sub>2</sub> thickness with Nanospec equipment                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7    |          |                                                        | 1-3   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |          | <u> </u>                                               | 1-3   |

| 10 NETG-SIM General simple cleaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |          |                                                        | 1-3   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10   | NETG-SIM | General simple cleaning                                | 1-3   |

| Si SiO <sub>2</sub> PEVCD SiO <sub>2</sub> Poly BPSG BPSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | çi       | SiO PEVCD SiO Poly                                     |       |

Thereafter, a 1  $\mu$ m thick layer of polycrystalline silicon was deposited by LPCVD at 580°C and 380 mtorr (step 11) followed by the deposition of 4  $\mu$ m of BPSG. The deposition of the sacrificial layer was done in two consecutive steps similar to the process described above. Nevertheless, the wafers presented lots of particles located on the surface and embedded in between the layers. For this reason, the 4  $\mu$ m sacrificial layer was stripped with BHF solution and the process was repeated (step 12). This time, four consecutive depositions of 1  $\mu$ m thick were done along with a cleaning process

with dip HF solution for 15 s and H<sub>2</sub>O after each deposition. To finally remove any residues, dirt or particles, the wafers were immersed in an ultrasonic bath with water for 10 min.

| Step     | Code                 | Description                                                           | Wafer      |

|----------|----------------------|-----------------------------------------------------------------------|------------|

| 11       | DPOLSENA             | LPCVD deposition of 1 μm of polycrystalline silicon (580°C/350 mTorr) | 1-3        |

|          |                      |                                                                       |            |

| 12       | DBPTEOSX             | PECVD deposition of 1 μm of doped SiO <sub>2</sub> BPSG               | 1-3        |

|          |                      | PECVD deposition of 1 μm of doped SiO <sub>2</sub> BPSG               | 1-3        |

|          |                      | PECVD deposition of 1 μm of doped SiO <sub>2</sub> BPSG               | 1-3        |

|          |                      | PECVD deposition of 1 μm of doped SiO <sub>2</sub> BPSG               | 1-3        |

|          |                      |                                                                       |            |

| 13       | HOLDRESP             | Particles on surface are removed using an ultrasonic bath for 10 min  | 1-3        |

| 14       | FOTO-ESP             | Photolithographic process of front wafer side with mask CNM677-BRID   | 1-3        |

| 15       | ESPECIAL             | Resin annealing at 200°C for 30 min                                   | 1-3        |

| 16       | PGIOXGUI             | Dry etching of doped SiO <sub>2</sub> BPSG                            | 1-3        |

| 17       | QGOXDXXX             | Wet etching of doped SiO <sub>2</sub> BPSG                            | 1-3        |

| 18       | AMRIEING             | Dry etching of 200 nm of polycrystalline silicon                      | 1-3        |

| 19<br>20 | DEC-RESI<br>QDRACXXX | Resin stripping Resin stripping with acid                             | 1-3<br>1-3 |

|          | QUI IOINI            |                                                                       | . 5        |

| 21       | MES-DEK3             | 3D mapping of the wafers topography                                   | 1-3        |

| 22       | NETG-SIM             | General simple cleaning                                               | 1-3        |

|          | Si                   | SiO <sub>2</sub> PEVCD SiO <sub>2</sub> Poly BPSG BPSG                |            |

The morphology of the microfluidic channels was patterned by soft-contact photolithography with mask CNM677-BRID (step 14) and the sacrificial layer etching with RIE (step 16). The dry etching equipment was operated at 90 mTorr, and at constant flow rate of 60 sccm of CHF<sub>3</sub> gas. The etching time for the BPSG layer was 600 s. To completely remove the BPSG material from the exposed areas, a wet etching step with BHF solution was done at different times for each wafer (step 17). Subsequently, another dry etching process of 200 nm of polycrystalline silicon was done for 70 s using the same photolithographic pattern and considering that the polycrystalline silicon material has an etching rate of 1900 Å/min (step 18). The purpose of this step was to improve the adhesion between the top and bottom structural layers by completely covering the sacrificial layer topology. The polycrystalline silicon material that remained after this etching step was 11754 Å. The next step

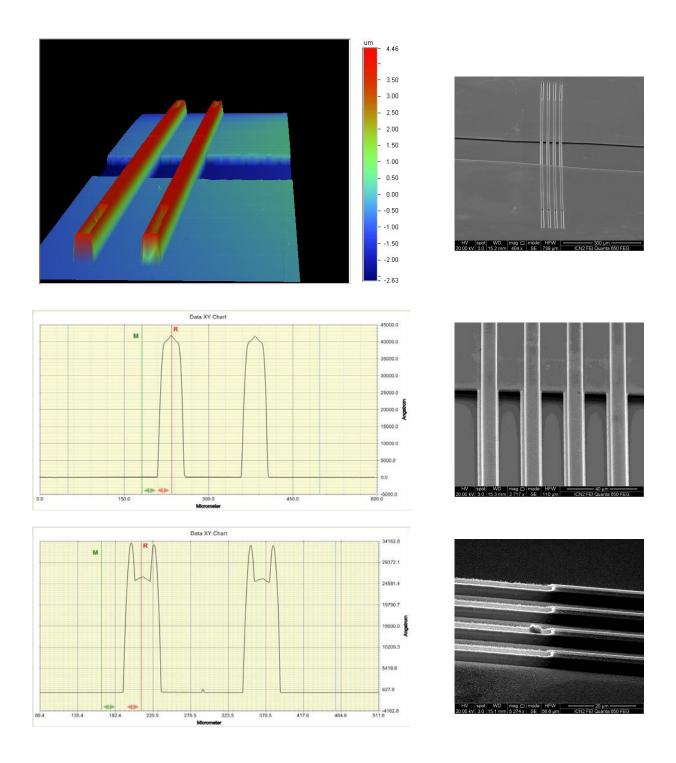

consisted of stripping the protective resin with acid to do a 3D mapping of the wafer topography with the profilometer (step 21), as shown in Fig. 3-11.

Fig. 3-11. (*Top*) 3D mapping of two BPSG microchannels with 4 μm height. (*Bottom*) the edges of the microchannel were slightly smoothed after the wet etching process with BHF etchant solution to remove residues of the sacrificial layer.

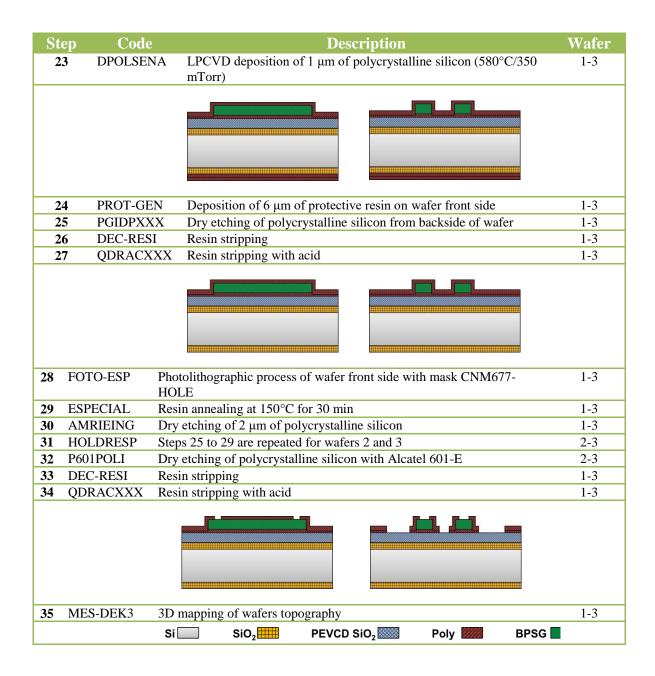

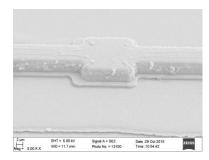

After a simple cleaning of wafers, another 1 µm layer of polycrystalline silicon was coated in order to enclose the microstructures and create a three-layer structure with the sacrificial layer in the middle (step 23). To remove the polycrystalline silicon deposited underneath the wafers, a 6 µm thick layer of protective resin was spun on the front side. Then, a RIE process etched the polycrystalline silicon material until uncovering the thermally grown SiO<sub>2</sub> layer (step 25). After stripping the protective resin on the front with reactive plasma and acid, access holes located at both ends of the microchannels and at the central trapezoidal frame that outlines the effective length the resonators were defined by soft-contact photolithography with MASK CNM677-HOLE (step 28). During this process, it was necessary to anneal the resin at 150°C for 30 min to stand for the dry etching of 2 µm of polycrystalline silicon material (step 32). The optimum dry etching time was conditioned based on the dry etching of wafer 1. Thereafter, a new 3D mapping of the structures was done after stripping the resin of the photolithographic process (step 35), as Fig. 3–12 describes.

From here, all the fabrication steps were done solely on wafer 1; the rest of wafers were put on hold. Wafer 1 was manually diced (step 36) into four pieces (M1, M2, M3 and M4) to find the optimum etching rates of the sacrificial layer using HF 49% acid solution as etchant. Each piece was assigned with a different etching times: 30 min, 5 min, 1 min and 20 min, correspondingly (steps 37 and 38). The resonators were released from the substrate in this procedure by dissolving the underlying silicon oxide (TEOS 2:1) at a lower etching rate (2.4 µm/min) than the BPSG sacrificial layer. After each isotropic wet etching, the samples were washed with deionized water and isopropyl alcohol and then dried in an oven at 100°C. For the case of sample M1, all microstructures vanished due to the over-etching of the underlying SiO<sub>2</sub>. As a result, the effective length of structures exceeded more than 300 µm and thus the released beams became fragile to manipulate while drying off the structures, as Fig. 3–13a shows.

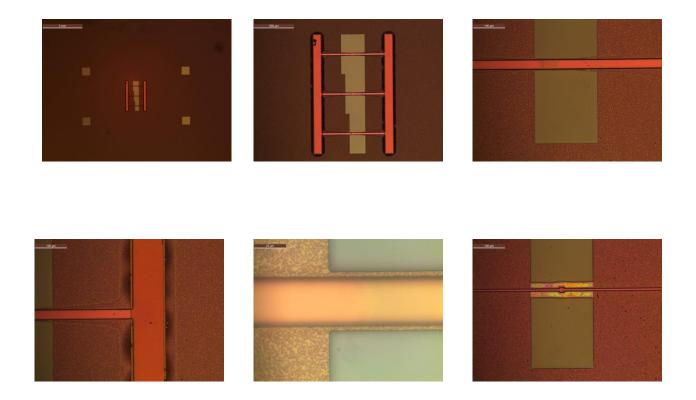

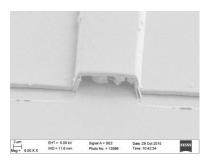

Fig. 3–12. (*Left*) morphology of two microchannels after the aperture of the microfluidic inlets. Also in this step the effective length of the beams was defined. The topography of the channels was taken from two locations: close to the clamp side of the beams and on top of the microfluidic inlets. (*Right*) SEM micrographs illustrating the corresponding topography of the microchannels.

Fig. 3–13. a) Sample M1 after the sacrificial layer wet etching. The underlying silicon oxide layer was over-etched which caused the collapsing of the beams at both clamp zones; b) cross section view of the embedded sacrificial layer in sample M2. Timing was not enough to empty and release the cavities and c) sample M4 shows the dimensions of a hollowed cavity after 20 min of isotropic wet etching with HF 49% acid.

For the cases of samples M2 and M3, the etching time was insufficient to empty and release the microstructures as can be seen in Fig. 3–13b. It was found that the optimum etching time was 20 min for the case of sample M4 with an average etching rate of 20 µm/min for the sacrificial layer. Fig. 3–13c shows a cross-sectional view and dimensions of a hollow cavity after this process. Then, a protective layer of 6 µm thick was deposited over sample M4 to dice the wafer manually into individual chips of 1 cm x 1 cm in size. The rest of the wafers were processed in a similar way after considering the optimized wet etching times. Afterwards, the protective resin was removed from devices using acetone for 10 min at room temperature, rinsing with isopropyl alcohol and drying the samples under nitrogen. Then, piranha solution for 10 min was employed to remove any organic traces. Samples were further rinsed with Mili-Q water and dried in an oven at 150°C to start the visual inspection by SEM micrographs of the devices with successfully fabricated microfluidic channels.

| Step | Code     | Description                                                             | Wafer |  |  |

|------|----------|-------------------------------------------------------------------------|-------|--|--|

| 36   | FEIN-ESP | Wafer is diced into four pieces (M1, M2, M3 and M4)                     |       |  |  |

| 37   | MST-ESP  | Wet etching of doped SiO <sub>2</sub> BPSG                              | 1     |  |  |

|      |          |                                                                         |       |  |  |

| 38   | MST-ESP  | Manual deposition of 6 μm of protective resin on front wafer side of M4 | 1     |  |  |

|      |          | and resin annealing at 100°C for 60 min                                 |       |  |  |

| 39   | FEIN-ESP | M4 sample is diced into 26 individual chips                             | 1     |  |  |

| 40   | DEC-ESP  | Resin stripping with plasma and piranha solution (t = 10 min)           | 1     |  |  |

| 41   | FIN-OBL  | End of process for wafer 1                                              | 1     |  |  |

| 42   | HOLDRESP | Stages 37 to 40 are repeated with optimum conditions                    | 2-3   |  |  |

| 43   | FINAL    | End of RUN                                                              | 2-3   |  |  |

|      | Si□      | SiO <sub>2</sub> PevcD SiO <sub>2</sub> Poly BPSG BPSG                  |       |  |  |

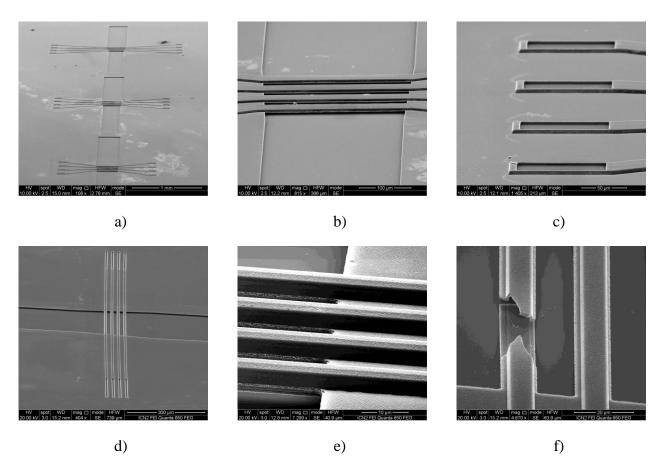

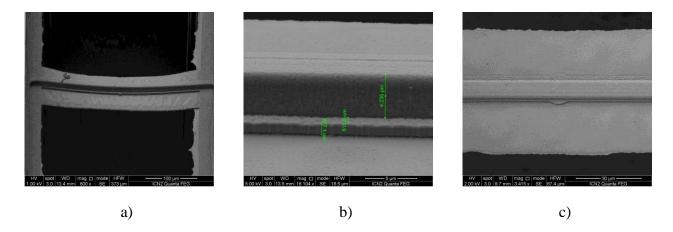

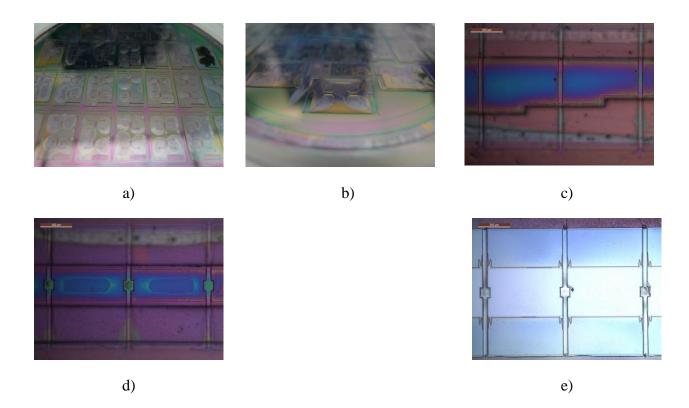

#### 3.2.1 General overview and evaluation of the fabrication process

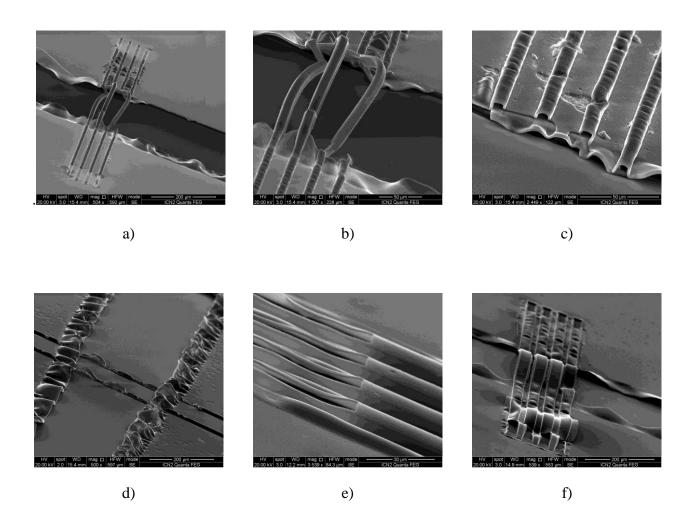

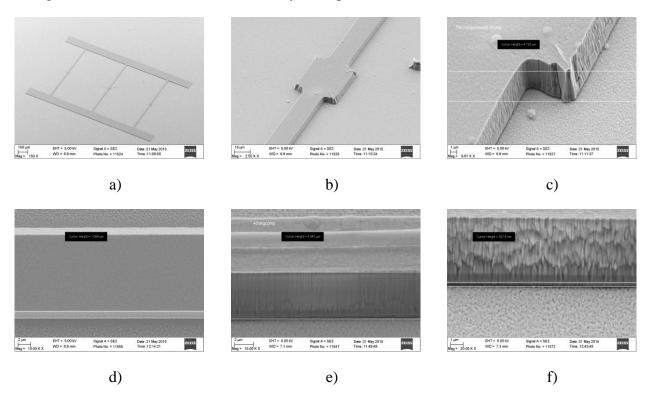

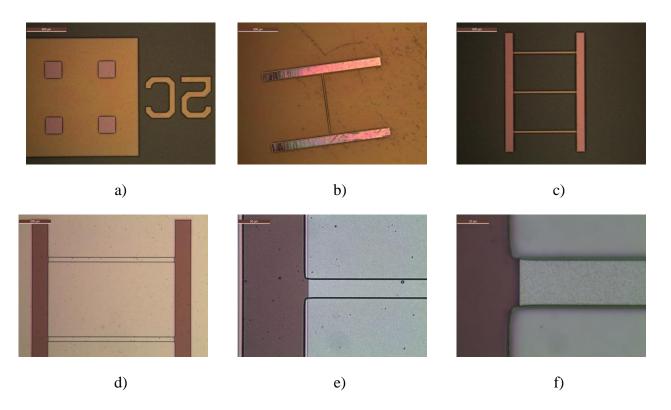

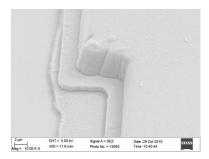

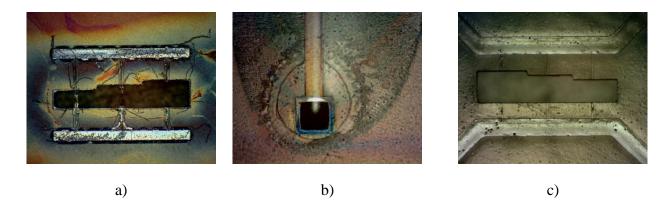

We have successfully built arrays of HMB resonators with the present fabrication approach. Fig. 3–14 shows a single device after finishing the process flow. Two completed wafers (2 & 3) were finished along with some devices from wafer 1 (only M4 sample). The resulted devices had dimensions of 0.8 x 1.0 cm a bit larger than those resulted from the first generation of HMB devices. The flow process allowed us to set optimum conditions on wafer 1 that influenced on the results of the rest of the wafers. As follows, we summarize the advantages and drawbacks of the present fabrication procedure.

Fig. 3–14. a) General on-chip distribution of three arrays of HMB resonators; b) Close view of a well-defined array of HMB resonators with a tilt angle of  $5^{\circ}$  at both clamp sides; c) Microfluidic inlets at both ends of each microfluidic channel; d) An array of four parallel HMB resonators of 20  $\mu$ m width; e) The microchannels protrude out from the substrate approximately 5  $\mu$ m and f) Successful wet etching of the sacrificial layer in the central part of the microbeams.

A visual inspection of the microstructures showed that the majority of released beams had collapsed after stripping the on top 6 µm protective resin spun over the devices to manually dice them. During the thermal annealing of this resin, the solvents evaporated, and thus the resin shrank causing that the released beams were under a compressive stress. As a result, the excessive stress broke the doubly clamp supports of the beams, see Fig. 3–15a. In other devices, the top polycrystalline silicon

layer was released from the substrate and also the microfluidic inlets cracked. Moreover, the resonators became more fragile as a funtion of the over-etching of the underlying silicon oxide. The etching ratio of the underlying silicon oxide was tenfold lower than the BPSG material and thus some undercut of the resonators was expected. Fig. 3–15b shows a lateral over-etching of approximately 25  $\mu$ m at each clamp side of the resonators. The undercut of resonators can be substantially reduced by including another photolithography mask to empty and release the resonators in two different wet etching processes.

Fig. 3–15. a) Collapsing of an array of beams after stripping the protective resin with acetone and water. Tensile forces yielded a breakdown of the structures making them non-functional. b) A 25 µm undercut of the released beams located at each clamp region. c) Deformation of resonator edges after the photolithography of mask CNM677-HOLE using a wrinkled resin.

Another important issue occurred on devices from wafer 1. During the photolithography with mask CNM677-HOLE the aspect of the deposited resin was wrinkled. This defect could be derived from the UV source light aging or by the quality of the deposited resin. Therefore, the wrinkled pattern was transferred onto wafer 1 producing an irregular definition of the microchannel edges. Fig. 3–15a shows this effect on a microstructure with 35  $\mu$ m width. Hence, to prevent the deformation of devices from other wafers, both the deposition of the resin and irradiation of the mask were carried out manually.

Unlike the first generation of devices, the effective wet etching of the sacrificial layer was due to the high selectivity between the structural (polycrystalline silicon) and sacrificial layer (BPSG). In the previous process, the sacrificial layer consisted of an undoped oxide layer that rendered low selectivity with respect to the silicon nitride structural layer. Interestingly, the wet etching ratio of the BPSG layer, in the second generation of HMB devices, was even faster than expected. Generally, the etching ratio of BPSG material is  $20 \, \mu \text{m/min}$ , if we consider the size of the longest microfluidic channel of about  $740 \, \mu \text{m}$ . Theoretically the expected time to completely remove the sacrificial layer should be  $37 \, \text{min}$ . In here, the time was reduced to  $20 \, \text{min}$ . This can be explained regarding the doping conditions of the sacrificial layer. Some studies have demonstrated that doping the oxide exclusively with phosphorous material can render even higher etching ratios [7].

Finally, deposition of polycrystalline silicon material by LPCVD showed good step coverage of the microchannels. However, the quality of the deposited layers was influenced by the properties of the underlying material. For example, polycrystalline silicon deposited on top of the microchannels showed a better distribution of grains with more compact boundaries than those deposited over the rest of the wafer. In this case, the underlying crystalline phase of polycrystalline silicon affected the properties of the top polycrystalline silicon layer yielding a rough surface with greater grain growth. Polycrystalline silicon is a polycrystalline material that can experience grain growth and phase transitions into other crystal structures while being deposited in thin films. This aspect is of great importance because a non-uniform layer can create zones of low material density leading to long-term instabilities.

#### 3.2.2 Oxidation schemes

Silicon dioxide material plays an important role, like silicon, in the fabrication of MEMS devices. Throughout a fabrication process, silicon dioxide has various functions such as passivation layer, electric isolation layer and capacitor dielectric. Additionally, thick oxides (100 - 1000 nm) can be used as masking layers for diffusion and etching processes, and even as sacrificial layers. One of the major advantages that silicon oxide offers is with respect to its hydrophilic properties given that this material is amorphous and produces planar surfaces when deposited over substrates. For instance, thin films of silicon dioxide have contact angles in the range of 45° to 65°. This property makes silicon dioxide suitable for the integration of new devices compatible with microfluidics.

In the fabrication of HMB devices we used polycrystalline silicon material as the structural layer of the resonators for several reasons. Deposition of polycrystalline silicon layers by the present fabrication scheme resulted in low-tensile strength structures with values between 800 to 1100 MPa [8], which prevented the deformation of the structures. Moreover, using polycrystalline silicon as structural material reduced the etching time of the embedded sacrificial layer to a few minutes. However, despite the excellent mechanical and thermal properties of MEMS devices fabricated with polycrystalline silicon material, their compatibility with liquid phase analytes results challenging. Polycrystalline silicon has hydrophobic properties that can yield contact angles between 85° and 110°, and so liquid samples, such as water, can easily be repelled. On the other hand, one of the advantages that polycrystalline silicon outstands with respect to devices fabricated with silicon nitride is that it can easily be oxidized by different methods such as thermal oxidation or by direct streaming of oxidation agents. This advantage is of importance, i.e. in modifying the hydrophilic properties of the inner microfluidics walls to facilitate the filling of resonators with fluids of different viscosities. Furthermore, a thin oxide grown on the polycrystalline silicon layer can be used as a cleaning method to reveal a smoother surface when removed by an etchant solution such as HF 49% acid.

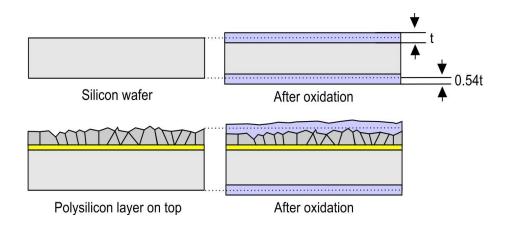

Oxide layers can easily be obtained through various methods. For instance, thin oxides can grow under ambient conditions to conform nanometric thick layers. Unfortunately, these oxides are not stoichiometric and have poor density and quality. In silicon microtechnology, there are two basic oxidation schemes based on thermal processes: wet and dry. A typical thermal process of a silicon

wafer is carried out at temperatures of 950-1100°C inside a furnace, and can last a couple of hours, depending on the final oxide thickness. Thermal oxidation is a slow process that depends on several conditions such as silicon crystal orientation and doping level. For instance, the oxidation rate of <111> silicon is higher than that of <100> silicon, and lightly doped substrates oxidize slower than highly doped [7]. Furthermore, when a thermal oxidation process takes place, the resulting oxide is approximate twice the volume of silicon it replaces. As shown in Fig. 3-16, for a silicon dioxide layer of thickness D, the replaced silicon thickness is about 0.54D. These oxide layers are usually measured by optical methods such as ellipsometry, interferometry or reflectometry. A quick and easy way to determine their thicknesses is by comparing the oxide colour with a specific colour chart of oxides given that each oxide thickness has a corresponding colour. Deal and Grove have also proposed a model to estimate the oxide thickness; this model predicts a linear oxidation rate initially, followed by a parabolic behaviour for the case of thicker oxides [7].

Fig. 3-16. Comparison of a silicon wafer oxidized with a thickness "t" to an oxidation scheme of polycrystalline silicon. The replaced volume of silicon material corresponds to a thickness of 0.54t.

We have done a study to take advantage of the hydrophilic properties of silicon oxide to enhance the wettability of the structural polycrystalline silicon layers of the resonators. In this way, the microchannel intrinsic resistance will be reduced to facilitate the filling of the microcavities by capillary forces. Consequently, once the microchannels were already filled, less applied hydrostatic pressure would be required to allow the fluidic samples to flow freely. Henceforth, we have proposed five schemes to oxidize the structural layer of some of our devices of the second generation using the model proposed by Deal and Grove to estimate the oxidation time according to the desired oxide thickness. Oxide thickness of approximately 50 nm, 100 nm, 150 nm and 200 nm were thermally grown by dry oxidation at 1100°C. An 1 µm oxide layer was also thermally grown at 1150°C by wet oxidation. These procedures were carried out at the Autonomous University of Barcelona (UAB) cleanroom facilities under non-contaminant conditions, according to the parameters shown in Table 3-2. Before the oxidation process, a visual inspection of the selected chips revealed that the majority of released microbeams had collapsed after stripping the top protective resin. The morphology of the microstructures can also influence on the uniform oxidation

of the substrates, particularly over convex and concave corners of the patterned structures. Afterwards, the devices were properly cleaned before the thermal process with piranha solution, rinsed with plenty of water and dried in an oven at 200°C for 1h. A test silicon wafer was also introduced into the furnace to evaluate the oxide thickness by ellipsometry after the oxidation process.

Table 3-2. Oxidation conditions for devices with polycrystalline silicon material. The time was determined according to the desired thickness of the oxidation layer.

| 750°C in N <sub>2</sub> | Temperature ramp  | Dry oxidation process at 1100°C with | Temperature ramp  | 750°C in N <sub>2</sub> |

|-------------------------|-------------------|--------------------------------------|-------------------|-------------------------|

| atmosphere              | increases with a  | $0_2$ at a flow rate of 120 sccm for | decreases with a  | atmosphere              |

| for 55 min              | positive slope of | $T_{dry} = TBD min$                  | negative slope of | for 55 min              |

|                         | 7°C/min           |                                      | -7°C/min          |                         |

|                         |                   | Wet oxidation process at 1150°C with |                   |                         |

|                         |                   | water vapour for                     |                   |                         |

|                         |                   | $T_{water} = TBD min$                |                   |                         |

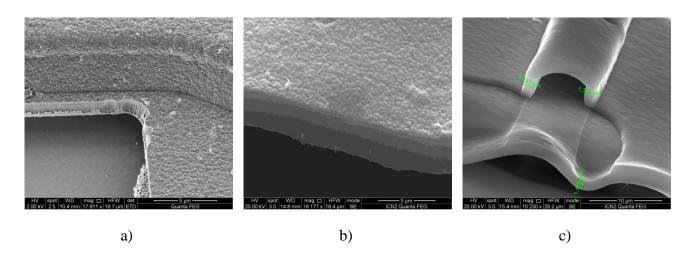

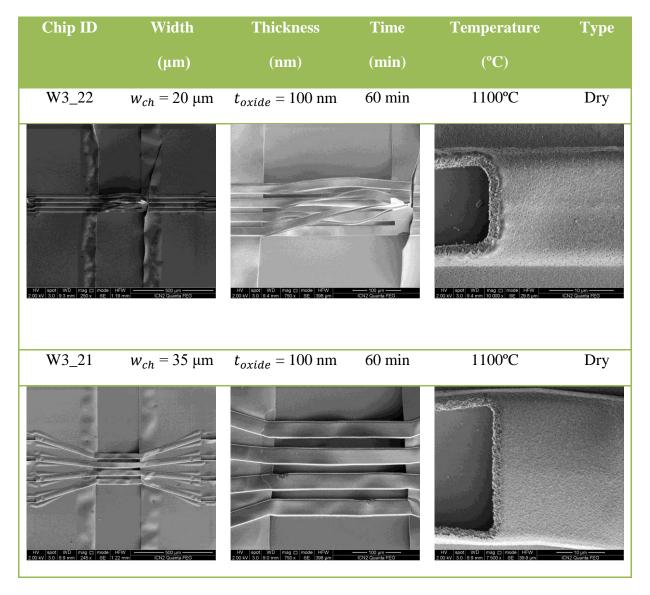

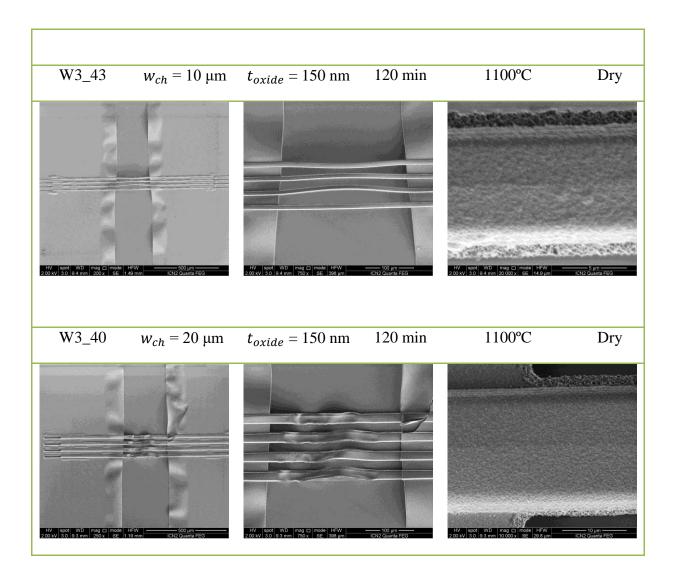

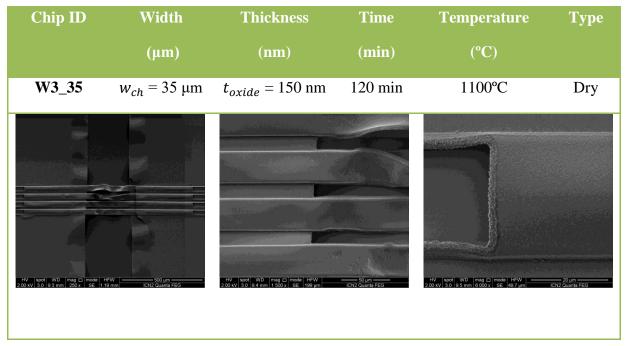

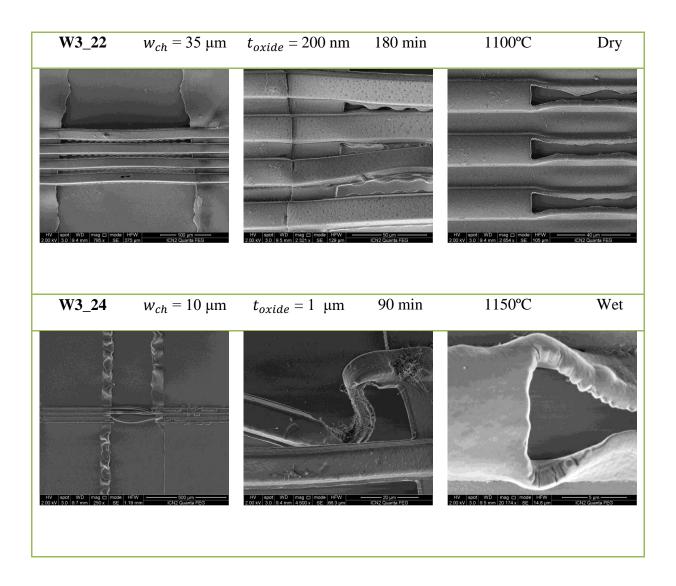

After the oxidation process, all samples were characterized using SEM to study the morphology and thickness of the conformally grown oxide layer. Measurements by ellipsometry provided imprecise oxide thicknesses given the lack of surface planarization of the wafer. The resulted non-uniformity can be associated with the following reasons: i) polycrystalline silicon consists of grains with various orientations and thus different oxidation rates can be expected according to the orientation of these grains (which are commonly orientated towards to (110) direction), ii) polycrystalline materials have two different diffusion paths, through the bulk and along the grain boundaries producing localized regions of thicker oxide layers, and thus more advanced models are required to estimate the final oxide layer thickness, as illustrated in Fig. 3-16, and iii) polycrystalline silicon is also more easily consumed than silicon material during the oxidation process given that the oxidation rate of undoped polycrystalline silicon lies between (100) and (111) silicon oxidation rates.

Furthermore, after the oxidation process of the devices, the majority of the released structures were under compressive stress forces. Thermally grown oxides are under compressive stress because the oxide volume is larger than the volume of substrate material they replace. Typical stress values are on the order of 300 MPa [7]. As seen in Fig. 3–17, the middle part of the beams was distorted upwards. The distortion ratio of the suspended beams was directly influenced by the width of the microchannels: wider structures had lower structural deformation than thinner ones. Since the temperature of both wet and dry oxidation processes was properly stabilized and monitored, time was the only varying parameter that might have influenced over the deformation of the structures. Furthermore, zones that were affected by the over-etching with HF 49% acid along the border of the central grid were contorted. It has been demonstrated that the stress of microstructures can be

reduced by performing annealing processes above 1000°C [7], but in our case, those suspended structures were highly susceptible to be deformed because of their reduce thicknesses.

Fig. 3–17. a) Grain size and distribution of an undoped polycrystalline silicon sample. The surface is rough and grains have a different orientation. b) A structural polycrystalline silicon layer with a 200 nm of grown oxide in which the grain size is smaller and compact, and the original polycrystalline silicon volume is consumed on both sides of the structural layer. c) A microchannel with a 1  $\mu$ m thick layer of oxide where the original polycrystalline silicon layer was completely consumed. The surfaces of the channel are clearly smooth with a more uniform grain distribution.

An appropriate cleaning of the substrates was predominant to achieve oxide layers with high quality. Devices whereby a 50 nm layer of oxide was grown displayed black spots throughout the chip surface. These spots might have come from contaminated residues or zones that still had moisture as Table 3-3 resumes. Furthermore, wider microchannels suffered from clogging of the structural layers. Regarding the quality of the grown oxide layer, the visual inspection of the structures showed that the grain density of wider microchannels (35 µm) was greater than the exhibited by thinner microchannels (10 µm) for all the oxidation schemes. Smoother and more planar surfaces were created by increasing the oxide thickness. For instance, the wet oxidation scheme allowed the complete replacement of the whole polycrystalline silicon layer by conformally creating an 1 µm thick oxide structural layer as Fig. 3–17c shows. The quality of the polycrystalline silicon material deposited by LPCVD during the fabrication process also influenced on the porosity and density distribution of grains of the thermally grown oxides. For example, the device of Fig. 3-18f, with a 200 nm oxide layer, displayed holes along some of its grain boundaries. In here, the replacement of polycrystalline silicon material uncovered areas with poor grain density and thus they were not easily conformed by the oxide layer. In general, the dry oxidation was slower than the wet oxidation approach because the concentration of the oxidant was much greater in the latter one. For instance, the time to produce a polycrystalline silicon oxidation of about 1 µm was reduced by half (90 min) with respect to the dry oxidation layer of 200 nm (180 min). In sum, the oxidation of the structured devices was constrained because the compressive stress upon the microchannels walls became excessively large particularly for suspended structures, leading to deformation of their original morphology. Table 3-3 shows an overview of the visual characterization of the oxidation processes for several devices.

Fig. 3–18. a) - c) Aspect of the array of resonators after growing 1  $\mu$ m layer of oxide by wet oxidation in which the structures are under compressive stress. d) - e) Contortion of the edges of the central grid were affected by the over-etching with HF 49% acid after growing an oxide layer of 150 nm. Also, the inlets of the microchannels were partially closed. f) The top structural layer was slightly detached from the substrate is some devices with a grown oxide of 200 nm.

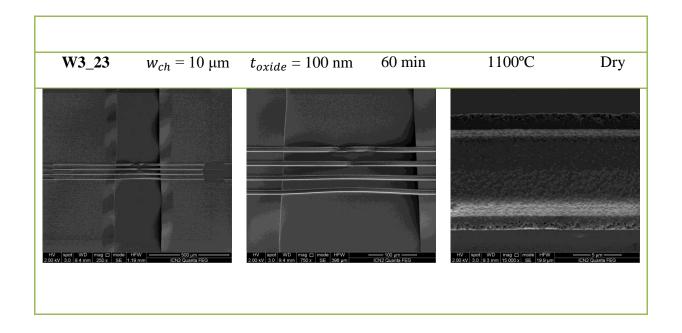

Table 3-3. Summary of the oxidation schemes for polycrystalline silicon resonators

| Chip ID                                                  | Width                        | Thickness                                                                | Time                       | Temperature                                                       | Type                                      |

|----------------------------------------------------------|------------------------------|--------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------|-------------------------------------------|

|                                                          | (µm)                         | (nm)                                                                     | (min)                      | (°C)                                                              |                                           |

| W3_18                                                    | $w_{ch} = 10 \ \mu m$        | $t_{oxide} = 50 \text{ nm}$                                              | 15 min                     | 1100°C                                                            | Dry                                       |

| HV spot WD mag □ mode 2 00 tV S0 9 s mm 200 x SE 1       | FFW C50 ym EON Gardin FEG    | HV spot WD mag D mode HFW 2.00 W 3.0 95 mm 850 x SE 351 um               | 100 µm.<br>ICN2 Quanta FEG | HV   spot   WD   mag     mode   HFW                               | 9 µm<br>ICN2 Quanta FEG                   |

| W3_19                                                    | $w_{ch} = 20 \ \mu \text{m}$ | $t_{oxide} = 50 \text{ nm}$                                              | 15 min                     | 1100°C                                                            | Dry                                       |

| HV spot W0 mag mode 200 kV 30 93 mm 250 x SE 1           | NFW CN2 Quarta FEG           | WD   mag                                                                 | 100 Jm.<br>ICN2 Quarts FEG | HV (stot) WD mag g mode HFW 200 kV 3.0 9.3 mm 10 000 x SE 29.8 μm | 10 juiti<br>ICN2 Quarta FEG               |

| W3_20                                                    | $w_{ch} = 35 \ \mu \text{m}$ | $t_{oxide} = 50 \text{ nm}$                                              | 15 min                     | 1100°C                                                            | Dry                                       |

| HV spot WD mag mode 2 00 kV 3 0   \$4 mm   250 x   \$E 1 | NFW 500 µm FEG               | 10 soot WD mag   mode HFW   2.00 kV   3.0   9.4 mm   750 x   SE   569 μm | — 100 µm ICM2 Quanta FEG   | HV   spot  WD   mag   mode  HFW                                   | 20 µm ——————————————————————————————————— |

# 3.3 Fabrication process of HMB devices of the third generation

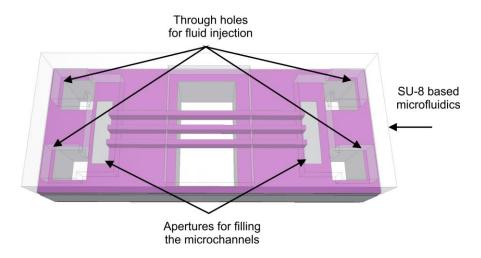

In this approach, the manufacture consisted of a sacrificial layer process of borophosphosilicate glass (BPSG) material, using polycrystalline silicon as a structural layer as in the previous fabrication process, but considering two objectives mainly: integrating on-chip microfluidics for fluid delivery and reducing the over-etching effect of the resonators as much as possible. The microfluidic delivery network for filling the embedded microchannels was built of SU-8 polymer, which demonstrated a good coverage step over the structures. The bypass microchannels were enclosed using a novel technique of SUEX lamination on top of the SU-8 resin. Also in this procedure, access through-holes were etched across the wafers using a combination of both surface and bulk micromachining techniques to inject the fluid sample from beneath the resonators

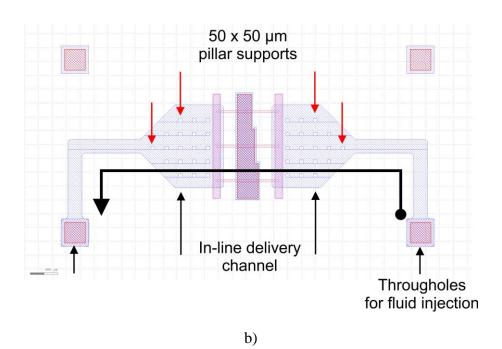

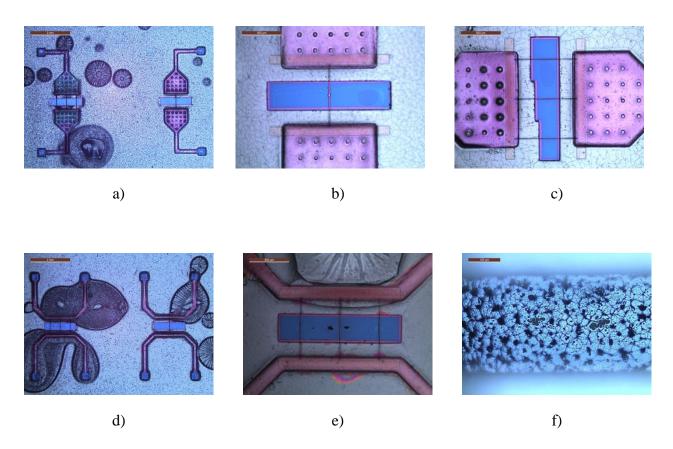

Fig. 3-19 shows the most important features of the HMB devices included in this fabrication scheme and a general overview of the main fabrication steps is introduced in Fig. 3-20.

Fig. 3-19. General view of the main features implemented for the fabrication of HMB devices. Surface and bulk micromachining techniques define the suspended structures with embedded microfluidic channels. Access through-holes are etched across the wafer for liquid injection from below the structures. SU-8 and SUEX polymers are used to integrate the microfluidic delivery channels on top of the structures.

#### 3.3.1 Mask design

The second batch of masks was designed specifically for the fabrication process using SU-8. In this case, six soda-lime photomasks of 5 inches in size were drawn in Klayout Software and printed by Compugraphics Company (Spain). The MFS for this type of mask was 1.5  $\mu$ m. Additionally, another mask was included in the fabrication process to pattern an alternative design for the bypass microfluidic channels. This mask was made of acetate with MFS of 7  $\mu$ m.

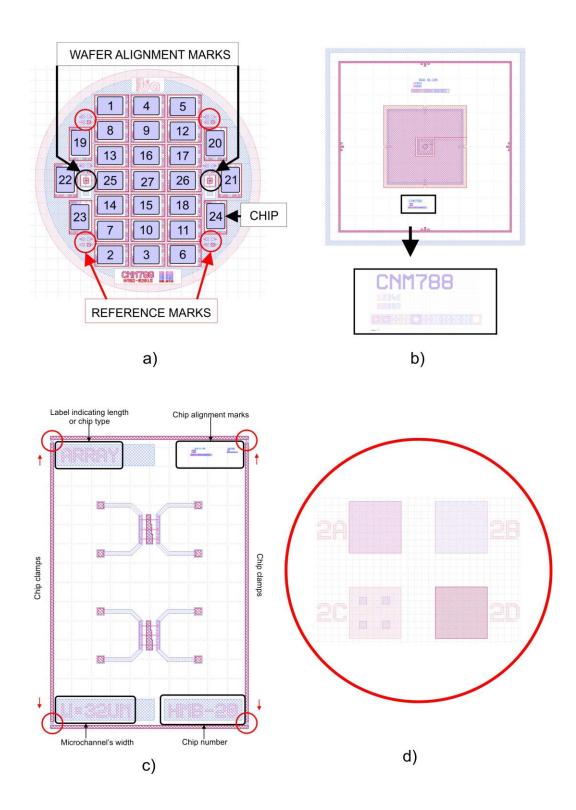

Fig. 3-21 shows twenty-seven devices distributed all over the mask design, including the doubled side alignment marks located in the center at a separation distance of 55 mm. Unlike the first batch

of masks, specific marks were designed throughout the wafer to monitor the main fabrication processes. The distribution of these motives facilitated various processes such as wafer inspection, layer thickness measurements, and dry and wet etching steps, among others. The dimensions of each device were  $1.5 \times 1$  cm and the alignment of the masks is presented schematically in Annex 2.

Fig. 3-20. Summary of the main fabrication steps: a) Initial silicon substrate, b) patterning of microchannels, c) microchannels enclosing, d) patterning of microfluidic inlets, e) wet etching of the sacrificial layer, f) oxidation of microchannels, g) patterning of fluid delivery inlets and definition of resonators, h) bulk micromachining steps, i) patterning and enclosing of polymer based microfluidics with SU-8 resin and SUEX epoxy and j) release of resonators and etching of fluidic inlets for liquid injection.

The content of each mask is described in detail as follows:

CNM788 HMB-BRID1. Similar to mask CNM677-BRID1, this is the first alignment mask that defines the dimensions of the microchannels. As

Fig. 3-21 shows, each device includes two configurations: a single microchannel (upper position) and an array of three microchannels (bottom position). Based on the experience from previous fabrication processes, the length of the microchannels was set to 900  $\mu$ m to reduce the etching time of the sacrificial layer. For configurations that included an array of microchannels, the separation distance between each beam was set to 500  $\mu$ m to overcome the superposition of the mechanical response of resonators with and effective length set to 200  $\mu$ m, 250  $\mu$ m and 300  $\mu$ m correspondingly. Also, the design of some resonators included a rectangular square in the middle of the microchannels. This section of the microchannel can work as a mechanical trap with the aim of increasing the residence time of fluids or streaming analytes.

The microfluidic inlets for all the microchannels were connected together to facilitate the entrance of fluids inside the cavities. This mask also included labels for indicating the device number, microchannels width, and alignment marks, as

Fig. 3-21c shows.

CNM788 HMB-HOLE2. This mask is aligned with respect to CNM788 HMB-BRID1 mask to define the fluidic inlets of the microchannels. Two aperture holes of 1500 x 110 µm of size located at both ends of the microchannels are outlined to uncover the sacrificial layer. Unlike mask CNM677-HOLE2, this mask just defines the fluidic inlets of the microchannels (see Fig. 3-22a). The effective length of the resonator and the outer frame motives were included in the next alignment mask to avoid the over-etching of resonators while removing the sacrificial layer with HF 49% acid.

CNM788 HMB-OPEN3. In this mask, the effective length of the resonators is defined including the outer frame to release the devices from the substrate. Clamp supports are designed on every corner side of a single device. During the fabrication process, this mask is aligned with respect to CNM788 HMB-HOLE2 mask. Moreover, four square holes (of 400 µm x 400 µm in size) are outlined around every configuration for the microfluidic inlets of the bypass channels as can be seen in Fig. 3-22a.

CNM788 HMB-GRID6. This mask is aligned with respect to CNM788 HMB-BRID1 mask using the double-sided alignment marks. The main features of this mask are like those from CNM788 HMB-OPEN3 mask with the exception that bulk micromachining steps are carried out to release the structures from beneath the silicon wafer (see Fig. 3-22a). Access through-holes are also defined for the bypass microfluidic channels inlets along with the outer frame of the devices.

CNM788 HMB-SU8A. In this mask, the polymer bypass fluidic channels are designed to fill the microfluidic channels of the resonators. Both channels of 200 µm width are placed along the fluidic inlets of the microchannels constituting an H-shaped microfluidic network, see Fig. 3-22a. During the fabrication process, this mask is aligned with respect to CNM788 HMB-OPEN3 mask.

CNM788 HMB-SU8A(ACETATE). Similar to mask CNM788 HMB-SU8A this design includes polymer channels to fill the resonators but with a single input/output fluidic configuration, also known as in-line. Initially, the channel has a 200  $\mu$ m width, and then, it gradually expands to 1200  $\mu$ m to cover all the fluidic entrances of the microchannels (see Fig. 3-22b). The same design is patterned on the other side of the microchannels. To reduce chances of clogging over wider areas of the microchannels, the mask design includes well-distributed pillar supports of 50  $\mu$ m x 50  $\mu$ m in size. This mask is made of acetate and therefore, the resolution is lower that the soda-lime counterpart. Nevertheless, the MFS complies well with the minimum feature size of motives.

CNM788 HMB-SU8B. This mask is aligned with respect to CNM788 HMB-SU8A mask and it is used during the lamination process of SUEX epoxy to enclose the bypass fluidic channels. Basically, it uncovers the epoxy from above the microstructures to allow the incidence of light for the mechanical characterization of the beams. It also uncovers the epoxy from the cutting marks of the devices to release them from the wafer, Fig. 3-22.

Fig. 3-21. General view of the main features in the mask design: a) twenty-seven devices distributed all over the mask design, b) double-sided wafer alignment marks and on-chip reference marks, c) design of a single device that integrates two configurations of HMB resonators, identification labels and outer frame with four clamps on every corner and d) reference marks to follow up and verify specific fabrication steps.

a)

Fig. 3-22. Main features of the HMB devices: a) an array of three resonators with lengths of 200  $\mu$ m, 250  $\mu$ m and 300  $\mu$ m, respectively. Wide fluidic inlets (1500  $\mu$ m x 110  $\mu$ m) are incorporated at both ends of the microchannels. Also, access through-holes are outlined for injection of fluid beneath the wafer. In this design, an H-shaped microfluidic configuration fills up the inner cavities and b) a simple input/output microfluidic configuration fills up the microchannels. It also integrates well-distributed pillar supports to avoid clogging of the polymer channels.

# 3.3.2 Fabrication process at cleanroom facilities

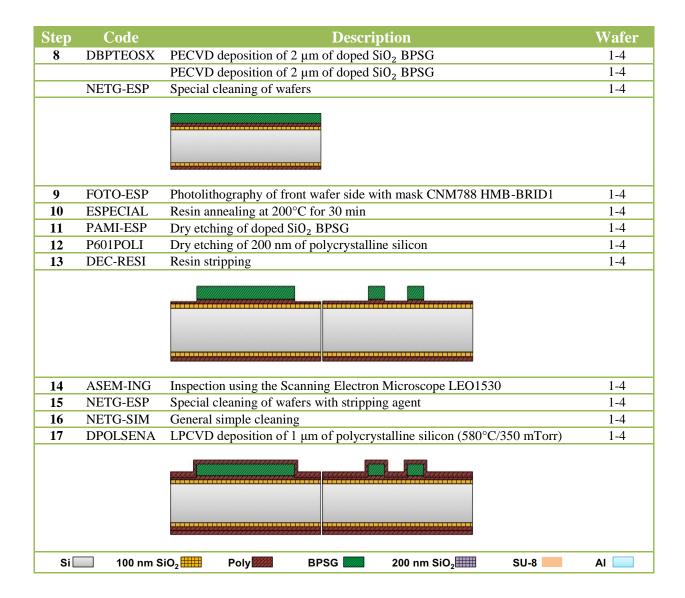

The microchannels were built using 4-in two side polished, type P silicon wafers of 300  $\mu$ m thick with a resistivity of 10-20 ohm-cm. Four silicon wafers were used as substrates, and their curvature was measured in the profilometer along the 0° and 90° axes (step 3) which yielded a compressive stress of wafers according to their curvature values (up to 4.5  $\mu$ m).

| Step | Code       | Description                                                           | Wafer |

|------|------------|-----------------------------------------------------------------------|-------|

| 1    | INICIO     | Preparation to begin RUN                                              | 1-4   |

| 2    | MARC-PXA   | Marking of silicon wafers                                             | 1-4   |

|      |            |                                                                       |       |

| 3    | MES-PRO    | Curvature measurement of backside of wafer                            | 1-4   |

| 4    | NET-GEN    | General cleaning                                                      | 1-4   |

| 5    | OHC-1000   | Thermal growth of 100 nm of SiO <sub>2</sub> at 950°C                 | 1-4   |

| 6    | NETG-SIM   | General simple cleaning                                               | 1-4   |

|      |            |                                                                       |       |

| 7    | DPOLSENA   | LPCVD deposition of 1 μm of polycrystalline silicon (580°C/350 mTorr) | 1-4   |

|      |            |                                                                       |       |

| Si   | 100 nm SiO | Poly BPSG 200 nm SiO <sub>2</sub> SU-8                                | AI 🔃  |

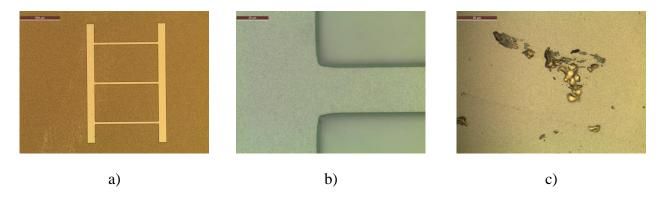

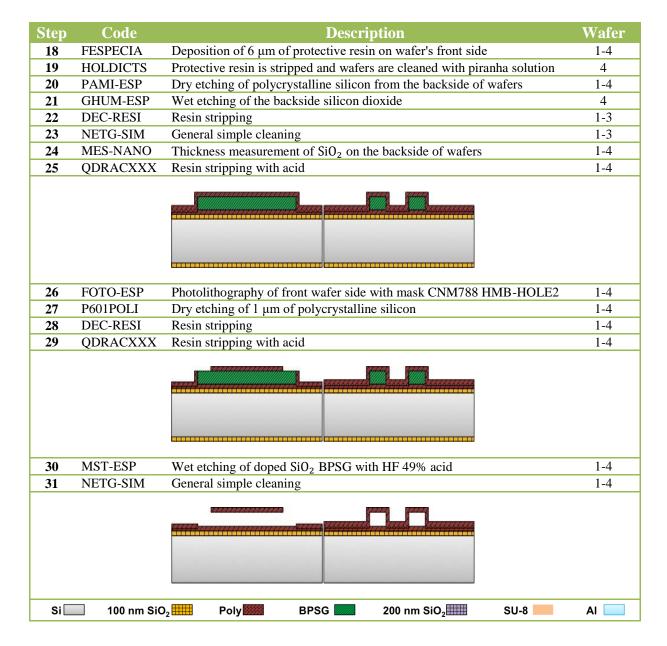

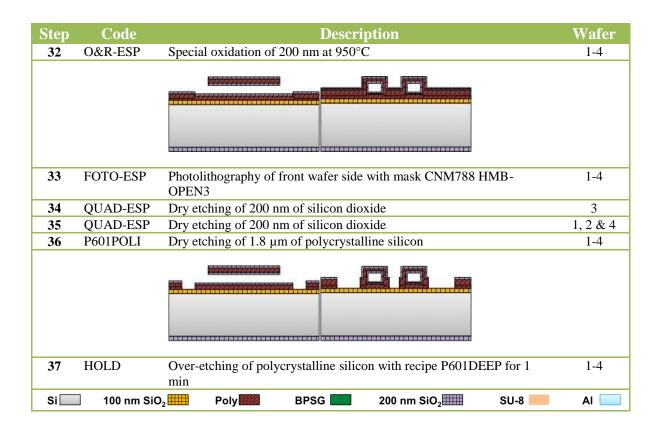

Then, a 100 nm layer of  $SiO_2$  was thermally grown to isolate the silicon substrate from the following processes (step 5). As follows, a 1  $\mu$ m layer of polycrystalline silicon was coated by LPCVD (step 7). In this step, a variation in the flow rate of the source gases produced an irregular deposition of polycrystalline silicon, which formed a ring of varying polycrystalline silicon thickness over the wafer perimeter. A two consecutive deposition of 2  $\mu$ m of doped  $SiO_2(BPSG)$  was further carried out (step 8). After the deposition, however, there were particle counts on the surface and embedded in between the deposited layers as Fig. 3–23a shows. These particles and residues were reduced by immersing the wafers in a dip HF 5% solution for 15 s and doing an ultrasonic bath with water for 10 min.

Fig. 3–23. a) Multiple particle counts after the two consecutive layer depositions of the BPSG material and b) patterning of the microfluidic channels using photolithography and RIE with a protective resin of 4  $\mu$ m. Some microchannels include a rectangular square in the middle of the doubly clamped resonator as a mechanical trap for increasing the residence time of fluid samples.