# MULTILEVEL TILING FOR NON-RECTANGULAR ITERATION SPACES

#### Marta Jiménez

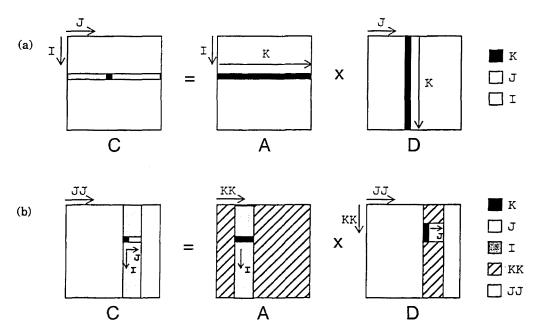

Departamento de Arquitectura de Computadores Universitat Politècnica de Catalunya Barcelona (Spain). March, 1999

A THESIS SUBMITTED IN FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE Doctor por la Universitat Politècnica de Catalunya

# MULTILEVEL TILING FOR NON-RECTANGULAR ITERATION SPACES

Author: Marta Jiménez

Advisor: Agustín Fernández

A mis padres y, especialmente, a Roger.

#### **ABSTRACT**

Microprocessor-based systems are increasingly becoming the workhorse for all scientific and engineering computation. They have numerical processing capabilities that already rival older generations of supercomputers. Over the last decade, microprocessor design strategies have focused on increasing the computational power available on a single chip. These advances in computational capacity have been achieved by reducing cycle time and also via architectural changes such as pipelined floating-point functional units, multiple instruction issue and out-of-order execution. Nevertheless, a high computation bandwidth is meaningless unless it is matched by a similarly powerful memory subsystem. Unfortunately, while on-chip operation speeds have improved dramatically, the performance of memory has not. The result has been an imbalance between computation speed and memory speed and this imbalance has led machine designers to use complex memory systems based on a hierarchy of levels.

However, to achieve high levels of performance it is not enough by improving the hardware structures. Compiler techniques should also be developed to fully utilize the architectural advances. In fact, the efficiency of architectural improvements depends on the compiler ability to change the structure of programs for taking full advantage of them. In the past few years, compilers have provided some support both to improve ILP and to optimize code for complex memory hierarchies. However, existing compiler technology is oriented mostly towards simple numerical codes containing simple loop nests that describe rectangular iteration spaces. This is understandable since transformations are easy to apply on this type of loop nests. Nevertheless, several linear algebra algorithms typically used in numerical codes consist of complex loop nests defining non-rectangular iteration spaces. Current commercial compilers are unable to restructure and optimize these types of codes and, therefore, poor performance is achieved on these complex loop nests.

This fact has led many programmers to restructure their algorithms by hand to perform well on particular memory systems, a situation that has lead to machine-specific programs. Additionally, manufacturers have tried to minimize the complexity of writing optimized code by providing numerical libraries that attain high performance under their machine. However, not all applications can take advantage of these libraries and there are many situations in which none of the routines provided can specifically solve the task at hand. We believe that restructuring a code

viii ABSTRACT

to achieve high performance should be the job of the compiler. Compilers, not programmers, should handle the machine-specific details required to attain high performance on each particular architecture.

The main motivation of this thesis is to develop new compilation techniques that address the lack of performance of complex numerical codes consisting of loop nests defining non-rectangular iteration spaces. Specifically, we focus on the loop tiling transformation (also known as blocking) and our purpose is the improvement of the loop tiling transformation when dealing with complex numerical codes. Our goal is to achieve via the loop tiling transformation the same or better performance as hand-optimized vendor-supplied numerical libraries.

We will observe that the main reason why current commercial compilers perform poorly when dealing with this type of codes is that they do not apply tiling for the register level. Instead, to enhance locality at this level and to improve ILP, they use/combine other transformations that do not exploit the register level as well as loop tiling. Tiling for the register level has not generally been considered because, in complex numerical codes, it is far from being trivial due to the irregular nature of the iteration space. Our first contribution in this thesis will be a general compiler algorithm to perform tiling at the register level that handles arbitrary iteration space shapes and not only simple rectangular shapes.

Our method includes a very simple heuristic to make the tile decisions for the register level. At first sight, register tiling should be performed so that whichever loop carries the most temporal reuse is not tiled. This way, register reuse is maximized and the number of load/store instructions executed is minimized. However, we will show that, for complex loop nests, if we only consider reuse directions and do not take into account the iteration space shape, the tiled loop nest can suffer performance degradation. Our second contribution will be a proposal of a very simple heuristic to determine the tiling parameters for the register level, that considers not only temporal reuse, but also the iteration space shape. Moreover, the heuristic is simple enough to be suitable for automatic implementation by compilers.

However, to be able to achieve similar performance to hand-optimized codes, it is not enough by tiling only for the register level. With today's architectures having complex memory hierarchies and multiple processors, it is quite common that the compiler has to perform tiling at four or more levels (parallelism, L2-cache, L1-cache and registers) in order to achieve high performance. Therefore, in today's architectures it is crucial to have an efficient algorithm that can perform multilevel tiling at multiple levels of the memory hierarchy. Moreover, as we will see in this thesis, multilevel tiling should always include the register level, as this is the memory hierarchy level that yields most performance when properly tiled.

When multilevel tiling includes the register level, it is critical to compute exact loop bounds and to avoid the generation of redundant bounds. The reason is that the complexity and the amount of code generated by our register tiling technique both depend polynomially on the number of loop bounds. However, to date, the drawback of generating exact loop bounds and eliminating redundant bounds has been that all techniques known were extremely expensive in terms of compilation time and, thus, difficult to integrate in a production compiler. Our third contribution in this thesis will be a new implementation of multilevel tiling that computes exact loop bounds at a much lower complexity than traditional techniques. In fact, we will show that the complexity of our implementation is proportional to the complexity of performing a loop permutation in the original loop nest (before tiling), while traditional techniques have much larger complexities. Moreover, our implementation generates less redundant bounds in the multilevel tiled code and allows removing the remaining redundant bounds at a lower cost. Overall, the efficiency of our implementation makes it possible to integrate multilevel tiling including the register level in a production compiler without having to worry about compilation time.

The last part of this thesis is dedicated to studying the performance of multilevel tiling. We will discuss the effects of tiling for different memory levels and present quantitative data comparing the benefits of tiling only for the register level, tiling only for the cache level and tiling for both levels simultaneously. Finally, we will compare automatically-optimized codes against hand-optimized vendor-supplied numerical libraries, on two different architectures (ALPHA 21164 and MIPS R10000), to conclude that compiler technology can make it possible for complex numerical codes to achieve the same performance as hand-optimized codes on modern microprocessors.

### **AGRADECIMIENTOS**

Deseo expresar mi más sincero agradecimiento a todas las personas que, con su ayuda, han hecho posible la realización de este trabajo:

A Agustín Fernández, por dirigir esta tesis y animarme continuamente a seguir adelante.

A José M. Llabería, por supervisar todo este trabajo, por todo lo que me ha enseñado y por todo el tiempo que me ha dedicado.

A Dolors y a Toni, por acompañarme durante todos estos años, por su ayuda y sus ánimos.

A Sergi y a Mildred, por aceptarme durante tantos años como compañera de despacho.

A todo el personal del LCAC y a los administradores de sistemas del CEPBA, por su excelente soporte técnico.

A Anna, Luis, Montse, Enric, Jose Ramón, Pepe y a todo el departamento de Arquitectura de Computadores, por ser magníficos compañeros de trabajo.

A Herr Huther, Herr Boyer y, muy especialmente, a Don José Cruz Santana, por todo lo que me enseñaron durante mi infancia.

A Pau Calpe y Gonzalo Martín, por estar a mi lado en los momentos más difíciles y por todo lo que hemos compartido y vivido juntos.

A mis tíos, Ramón y Ma. Angela, y a mis primas, Carmen, Elisabet y Angela, por acogerme durante mis primeros años en Barcelona y hacer que me sintiera como en casa.

A toda mi familia de Barcelona, especialmente a Ramón Espasa, Carme Sans, Marina Espasa y Carme Alfonso, por todo su cariño y por su apoyo continuo durante todos estos años.

A mi hermana Carmen, por hacerme reir cada día con sus divertidísimos e-mails y por ser algo más que una hermana.

A mis padres, José Luis y Carmen, y a mis hermanos, José Luis, Ching Lee, Isaac, Cristian y Carmen, por su infinito amor, por su incesante apoyo y por mucho más de lo que puedo expresar con palabras.

Finalmente, y con todo mi cariño, a Roger. Sin ti, este trabajo no habría sido posible.

This work was supported in part by the Ministry of Education of Spain under contracts TIC-92-0880, TIC-95-0429 and TIC-98-0511 and by the CEPBA (European Center for Parallelism of Barcelona).

# **CONTENTS**

| 1 | INT  | RODUCTION 17                        |  |  |  |

|---|------|-------------------------------------|--|--|--|

|   | 1.1  | Motivation                          |  |  |  |

|   | 1.2  | The Memory Latency Problem          |  |  |  |

|   | 1.3  | Coping with Memory Latency          |  |  |  |

|   |      | 1.3.1 Hardware Strategies           |  |  |  |

|   |      | 1.3.2 Compiler Strategies           |  |  |  |

|   | 1.4  | Loop Tiling in Commercial Compilers |  |  |  |

|   | 1.5  | Thesis Overview                     |  |  |  |

|   | 1.6  | Related Work                        |  |  |  |

|   | 1.7  | Thesis Organization                 |  |  |  |

| 2 | LOC  | LOOP TILING BASICS 35               |  |  |  |

|   | 2.1  | The Loop Tiling Transformation      |  |  |  |

|   | 2.2  | Preliminary Concepts                |  |  |  |

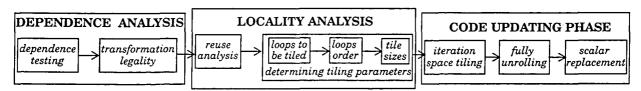

|   | 2.3  | Automatic Loop Tiling               |  |  |  |

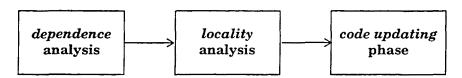

|   |      | 2.3.1 Dependence Analysis           |  |  |  |

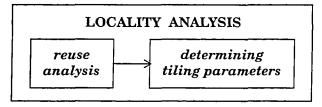

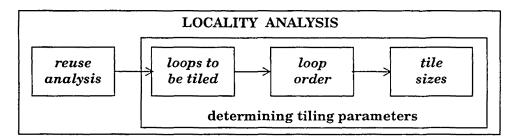

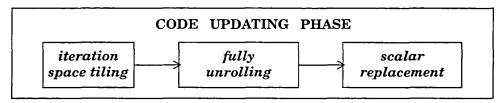

|   |      | 2.3.2 Locality Analysis             |  |  |  |

|   |      | 2.3.3 Code Updating Phase           |  |  |  |

|   | 2.4  | Non-rectangular Iteration Spaces62  |  |  |  |

|   | 2.5  | Summary                             |  |  |  |

| 3 | TILI | NG FOR THE REGISTER LEVEL65         |  |  |  |

|   | 3.1  | Introduction                        |  |  |  |

|   | 3.2  | Implementation of Register Tiling   |  |  |  |

xiv CONTENTS

|   |      | 3.2.1    | Overview                                    |

|---|------|----------|---------------------------------------------|

|   |      | 3.2.2    | A Step-by-step Example of Register Tiling71 |

|   |      | 3.2.3    | Index Set Splitting Algorithm74             |

|   |      | 3.2.4    | Complexity and Code Expansion               |

|   | 3.3  | Benefit  | s of Register Tiling89                      |

|   |      | 3.3.1    | Reducing Load/Store Instructions            |

|   |      | 3.3.2    | Improving Instruction Level Parallelism92   |

|   |      | 3.3.3    | Register Tiling vs. Outer Unrolling93       |

|   | 3.4  | Locality | y Analysis for the Register Level94         |

|   |      | 3.4.1    | Tile Directions                             |

|   |      | 3.4.2    | Iteration Space Shape98                     |

|   |      | 3.4.3    | Heuristic                                   |

|   | 3.5  | Perforn  | nance Evaluation                            |

|   |      | 3.5.1    | Evaluation Process                          |

|   |      | 3.5.2    | Performance Results                         |

|   | 3.6  | Related  | l Work                                      |

|   | 3.7  | Summa    | rry                                         |

| 4 | SIMU | JLTANE   | EOUS MULTILEVEL TILING                      |

|   | 4.1  | Introdu  | ection                                      |

|   | 4.2  | Conven   | tional Tiling Implementation                |

|   |      | 4.2.1    | Implementation                              |

|   |      | 4.2.2    | Complexity                                  |

|   | 4.3  | Simulta  | aneous Multilevel Tiling                    |

|   |      | 4.3.1    | Framework                                   |

|   |      | 4.3.2    | Strip-mining all Loops at all Levels        |

|   |      | 4.3.3    | Loop Permutation                            |

|   |      | 4.3.4    | SMT Summary145                              |

|   |      | 4.3.5    | SMT Example                                 |

|   |      |          |                                             |

|                  | 4.4 Efficient Implementation of SMT |         |                                           | 147 |

|------------------|-------------------------------------|---------|-------------------------------------------|-----|

|                  |                                     | 4.4.1   | Computing the Bounds of TI-loops          | 147 |

|                  |                                     | 4.4.2   | Examining fewer Simple Bounds             | 148 |

|                  |                                     | 4.4.3   | Steps of the Efficient SMT Implementation | 152 |

|                  |                                     | 4.4.4   | SMT Algorithm                             | 156 |

|                  | 4.5                                 | Compl   | exity of the Efficient SMT Implementation | 160 |

|                  | 4.6                                 | Redun   | dant Bounds                               | 165 |

|                  | 4.7                                 | Compa   | aring SMT vs. Conventional Techniques     | 178 |

|                  |                                     | 4.7.1   | Complexity                                | 178 |

|                  |                                     | 4.7.2   | Redundant Bounds                          | 180 |

|                  | 4.8                                 | Relate  | d Work                                    | 182 |

|                  | 4.9                                 | Summ    | ary                                       | 184 |

| 5                | MUI                                 | LTILEV  | EL TILING EVALUATION                      | 185 |

|                  | 5.1                                 | Introdu | uction                                    | 186 |

|                  |                                     |         | of Loop Tiling                            | 187 |

|                  |                                     | 5.2.1   | Tiling for the Register Level             | 187 |

|                  |                                     | 5.2.2   | Tiling for the Cache Level                | 190 |

|                  |                                     | 5.2.3   | Tiling for the Cache and Register Levels  | 192 |

|                  | 5.3                                 | Evalua  | tion Process                              | 194 |

|                  |                                     | 5.3.1   | Benchmarks Programs                       | 194 |

|                  |                                     | 5.3.2   | Target Architectures                      | 195 |

|                  |                                     | 5.3.3   | Code Generation                           | 195 |

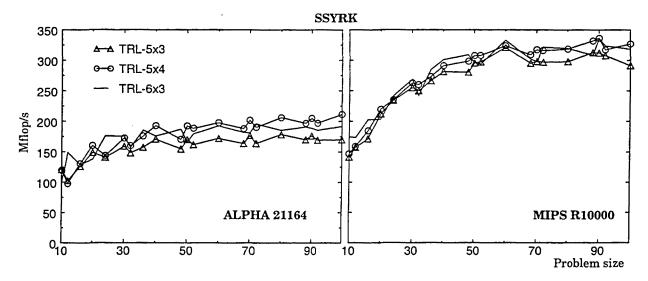

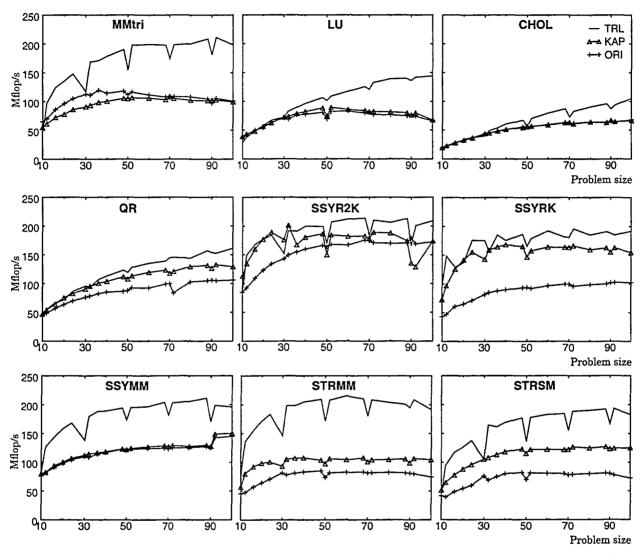

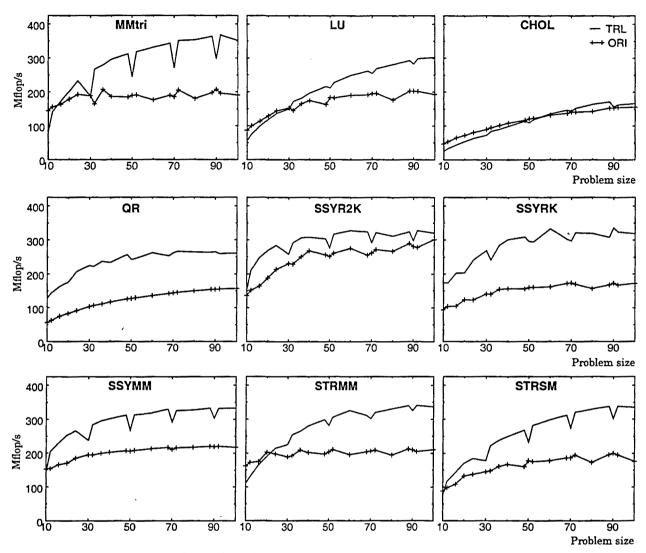

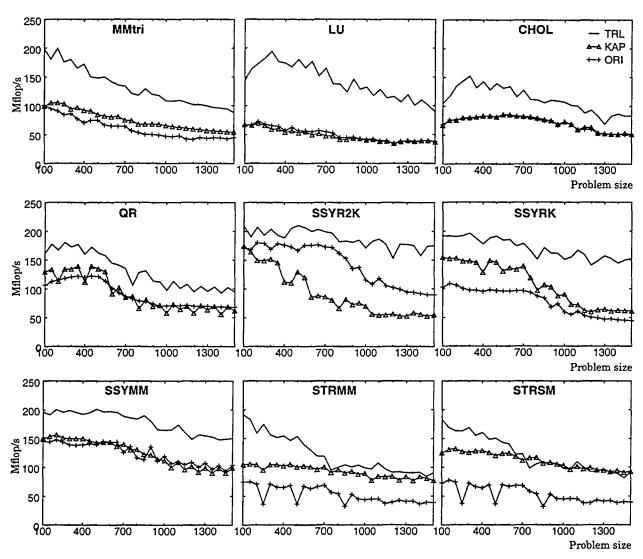

|                  | 5.4                                 | Perform | nance Evaluation                          | 198 |

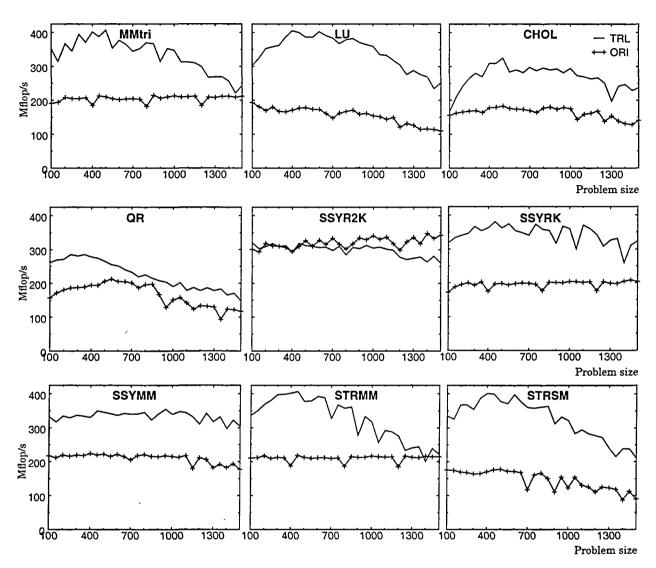

|                  | 5.5                                 | Hand v  | s. Automatically-Optimized Codes          | 209 |

|                  |                                     | 5.5.1   | Evaluation Process                        | 209 |

|                  |                                     | 5.5.2   | Performance Results                       | 211 |

| 5.6 Related Work |                                     |         |                                           | 216 |

|                  | 5.7                                 | ary     | 217                                       |     |

xvi CONTENTS

| 6   | CON  | ICLUSIONS AND FUTURE WORK         |  |  |

|-----|------|-----------------------------------|--|--|

|     | 6.1  | Conclusions                       |  |  |

|     | 6.2  | Future Work                       |  |  |

| A   | FOU  | RIER-MOTZKIN ALGORITHM 225        |  |  |

|     | A.1  | Introduction                      |  |  |

|     | A.2  | Implementation                    |  |  |

| В   | PRO  | PROOF 229                         |  |  |

|     | B.1  | Introduction                      |  |  |

|     | B.2  | Proof                             |  |  |

|     | B.3  | Back to the Notation of Chapter 3 |  |  |

| C   | BEN  | CHMARK PROGRAMS                   |  |  |

| D   | PRO  | oof 239                           |  |  |

| RII | SLIO | SRAPHY 243                        |  |  |

# 1

# INTRODUCTION

### **Summary**

In this chapter we present the motivation behind this thesis. Our goal is to improve current compiler technologies to achieve high performance on complex numerical codes. The main reason numerical codes perform poorly on modern microprocessors is that they do not utilize the memory system effectively, specially the register level. In this chapter, we review different hardware and compiler techniques developed to maximize the effectiveness of the memory system and we explain why current commercial compilers still perform poorly when dealing with complex codes. Finally, we conclude with a thesis overview, a summary of related work and the thesis organization.

#### 1.1 MOTIVATION

Microprocessor-based systems are increasingly becoming the workhorse for all scientific and engineering computation. They have numerical processing capabilities that already rival older generations of supercomputers and the microprocessors used in these systems will continue to improve due to every-increasing clock rates and new architectural advances. In contrast to the vector-based machines that have long dominated high performance computing, these new scalar systems are considerably more cost-effective since they contain commercial microprocessors that are mass-produced for the large general-purpose computing market. In addition, these microprocessors can be used to build large-scale multiprocessors capable of aggregate peak rates sometimes improving that of current vector machines.

The performance of a microprocessor-based computer is determined by the performance of its memory system. While on-chip operation speeds have improved dramatically, the performance of memory has not. Thus as the processor cycle time comes down, the latency to main memory has been increasing. To ameliorate these problems, machine designers have turned to complex memory systems based on a hierarchy of levels. The idea behind a *Memory Hierarchy* is to place a small high-speed memory close to the processor which is backed up by increasingly larger but slower memories. The key issue for high performance under a memory hierarchy is the minimization of data transfers between the different memory levels.

Unfortunately, modern microprocessors using such memory hierarchies perform poorly on numerical applications. Numerical codes tend to operate on very large data sets that do not fit in the small high-speed memories that are close to the processor. The result is a large amount of data being transferred between the different memory levels, yielding poor memory system performance. However, numerical codes tend to have patterns of data usage that are regular in structure and that include opportunities for data reuse. These regularities have led many programmers to restructure their algorithms by hand to increase data reuse and better exploit the memory hierarchy. The drawback of this approach is that manually optimized codes are difficult to write, difficult to debug and, even worse, hardly understandable once finished. Moreover, manually optimizing a certain code introduces machine parameters that have nothing to do with the problem being solved and which must be adjusted for each computer where the algorithm must be run if good performance is to be achieved.

Manufacturers have tried to minimize the complexity of writing optimized code by providing numerical libraries that attain high performance under their particular memory hierarchy. The BLAS3 library [38][39], for example, provides a set of standard linear algebra operations which are highly optimized for each specific machine. On top of the BLAS standard interface, higher level library packages such as LAPACK<sup>1</sup>[9] have been built. These higher level packages provide a rich variety of

mathematical algorithms that take advantage of the BLAS3 vendor-optimized routines. However, not all applications can take advantage of these libraries and there are many situations in which none of the routines provided can specifically solve the task at hand.

We believe that restructuring a code to better exploit the memory hierarchy should be the job of the compiler. Although the library approach just described can handle some situations, in general we believe that compilers should take the responsibility of optimizing code to exploit the memory hierarchy. Compilers, not programmers, should handle the machine-specific details required to attain high performance on each particular architecture. Algorithms should be expressed in a natural, machine-independent form and the compiler should apply the appropriate transformations to optimize the resulting code.

In the past few years, compilers have provided some support to optimize code for complex memory hierarchies. Compiler algorithms to manage the memory hierarchy automatically have been developed and shown through experimentation to be effective. However, existing compiler technology is oriented mostly towards simple numerical codes containing simple loop nests with constant loop bounds. This is understandable since transformations are easy to apply on this type of loop nests. Nevertheless, several linear algebra algorithms typically used in numerical codes consist of complex loop nests that have complex functions as their loop bounds. Current commercial compilers are unable to restructure and optimize these types of codes and, therefore, poor performance is achieved on these complex loop nests.

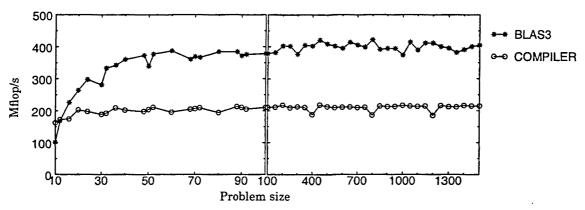

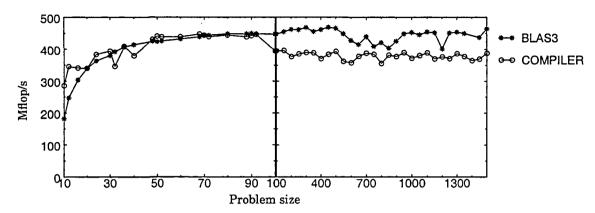

As an example, Fig. 1.1 shows the performance (in Mflop/s) obtained by the linear algebra problem STRMM, varying the problem size. Measurements were taken on a R10000 processor. The STRMM problem is a matrix by matrix multiplication with one of the matrices being triangular. The circle curve shows the performance obtained if we directly compile the code of STRMM using the f77

Figure 1.1: Performance of STRMM on the R10000 processor, varying the problem size.

<sup>1.</sup>LAPACK, "Linear Algebra Package", is a project originated by Jack Dongarra. This project put together a new set of linear algebra functions, supposed to supplant both the LINPACK and EISPACK packages. To achieve maximum efficiency across all types of hardware, the LAPACK routines are based on the BLAS3 routines.

Figure 1.2: Performance of SGEMM on the R10000 processor, varying the problem size.

compiler with maximum level of optimization. The star curve shows the performance obtained if we call the vendor-optimized BLAS3 library [38] to perform the operation. It is well known that the BLAS3 library is highly hand-optimized to properly exploit the machine characteristics. We can see how current compilers achieve poor performance compared with the hand-optimized code provided by the BLAS3 library.

In contrast, let's now look at how commercial compilers behave on *simple* numerical codes. Figure 1.2 shows the performance obtained by the linear algebra problem SGEMM. SGEMM consists of a very simple loop nest, performing a rectangular matrix by matrix multiplication. We can see how, in this case, the native compiler is able to achieve higher performance than in the STRMM problem. Nevertheless, the hand-optimized BLAS3 library still performs better for large problem sizes.

The conclusion is that, despite all the effort put in current compilers to achieve high performance in numerical codes, hand-optimized codes still outperform them. Moreover, this performance difference between hand-optimized codes and automatic-optimized codes is more noteworthy in complex numerical codes as seen in the STRMM problem.

The goal of this thesis is to develop new compilation techniques that address the lack of performance of complex numerical codes when run under a memory hierarchy. Compiler algorithms to restructure complex numerical codes are developed and shown through experimentation to be effective.

The remainder of this chapter reviews different hardware techniques developed for coping with the memory latency problem and different compilers strategies proposed for fully realizing the architectural advances. Then we will explain why current commercial compilers still perform poorly when dealing with complex scientific applications. Finally, we conclude this chapter with a thesis overview, a summary of related works and the thesis organization.

#### 1.2 THE MEMORY LATENCY PROBLEM

Over the last decade, microprocessor design strategies have focused on increasing the computational power available on a single chip. This advances in power have been achieved by reducing cycle time and also via architectural changes such as pipelined floating-point functional units, multiple instruction issue and out-of-order execution.

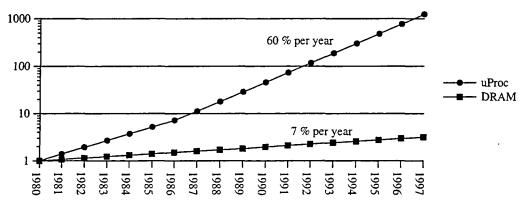

Unfortunately, a high computation bandwidth is meaningless unless it is matched by a similarly powerful memory subsystem. Although microprocessor speed has been increasing dramatically the speed of memory has not kept pace. Figure 1.3 shows the evolution, in relative terms, of microprocessors and DRAM speeds over the past 16 years. As it can be seen, from 1986 onward the microprocessor cycle time has been improving at a rate of 60% per year, approximately. Meanwhile, DRAM speeds have been slowly improving at a rate of only 7% per year. Producers of DRAM's have mostly focused on improving cost per bit and density per chip rather than favoring faster cycle times. The result is that, although density has gone from 16 Kbits in a chip in 1976 to 64 Mbits in a chip in 1996 (a 4000-fold improvement), these chips have only moved from a 400ns cycle time down to a 80ns cycle time (a 5-fold improvement). Today, memory chips are on the order of 10 to 100 times slower than CPUs.

Also, the instruction level parallelism available in recent microprocessors has increased. Since several instructions are being issued in the same processor cycle, the total amount of data requested per cycle to the memory system is much higher. This increase in requested data can be partially supported by an adequate increase in the number of memory ports. However, while most of current microprocessors are able to issue up to 4 instructions per cycle, the number of memory ports has not increased enough to support this degree of instruction parallelism.

These factors have led to a situation where each off-chip memory access can have extremely large latencies. As a result, and depending on the degree of cache-friendliness, the total execution time of a program can be greatly dominated by average memory access time.

Figure 1.3: Relative evolution of microprocessor and DRAM speeds (source [101]).

#### 1.3 COPING WITH MEMORY LATENCY

The memory latency problem has been attacked from two different fronts. First, computer architects have proposed several hardware mechanisms that ameliorate the memory latency problem: lockup-free caches, memory hierarchies, prefetching, out-of-order execution, etc. Second, compiler techniques have been developed to fully utilize the hardware structures available. In this section we will briefly review different hardware techniques developed for coping with the memory latency problem and different compilers strategies proposed for fully realizing these hardware proposals.

#### 1.3.1 Hardware Strategies

To reduce the memory latency problem, computer architects have proposed several strategies that can be divided into two categories: those for tolerating memory latency and those for avoiding latency. Latency tolerance means doing "something else" while data is being fetched from memory while latency avoidance tries to approximate memory access time to processor cycle time. The result of both techniques is a reduction on the number of processor cycles spent waiting for memory accesses to complete. Hardware strategies for tolerating latencies include write buffers, non-blocking loads, lockup-free caches, prefetching, out-of-order execution and multithreading, and the most common hardware mechanisms for latency avoidance are memory hierarchies, victim caches and pseudo-associative caches.

One way to tolerate memory latency is to allow memory references to be buffered. This technique was initially applied only to writes in the form of write buffers. Using write buffers, the processor does not have to wait for a write to complete. Instead, it performs a write by simply issuing it to the write buffer, a simple operation that is performed in one cycle. The advantage of a write buffer is not only that the processor does not stall when executing a write, but also that bus contention is reduced by delaying writes until idle bus cycles occur [61].

Buffering read accessed is more difficult because, unlike writes, the processor typically cannot proceed until the read access completes, since it needs the data that is being read. With non-blocking loads and lockup-free caches it is possible to buffer read accesses. A non-blocking load [43] allows the CPU to continue executing on a cache miss. That is, rather than stalling at the time a load is performed, the processor postpones stalling until the data is actually used, thus hiding the latency of the memory request with the following independent instructions. Non-blocking loads were later combined with lockup-free caches [75] to escalate their potential benefits. A lockup-free cache is able to supply data resulting from a cache hit even while processing a prior miss. Also, lockup-free caches typically allow multiple outstanding cache misses, thus giving the processor more possibilities to continue executing instructions while the misses are being served.

Another hardware advance to tolerate memory latencies is hardware prefetching [12][47][100][114]. It tolerates memory latency by performing data requests sufficiently far in advance of the use of the data in the execution stream. Obviously, this approach requires lockup-free caches so that processors can proceed while prefetched data are being fetched. Prefetching also requires the ability to predict which data items are needed ahead of time, a difficult task to be done in hardware and that can yield to a high rate of useless prefetching that can actually lower performance. An alternative to hardware prefetching is for the compiler to insert prefetch instructions to request the data before they are needed [72][93][102][119]. Issuing prefetch instructions incurs an instruction overhead, thus, care must be taken to ensure such overhead does not exceed the benefits.

Besides these hardware mechanisms, in the last decade there has also been important architectural improvements, such as *out-of-order* and *multithreaded* execution, to attack the memory latency problem. *Out-of-order* architectures [8][68][117][130] attack the memory latency problem by allowing memory accessing instructions to precede while other instructions are waiting for memory data. That is, memory instructions are allowed to slip ahead of execution instructions. *Multithreaded* processors [2][41][118], however, deal with the memory latency problem by switching between threads of execution every time a long latency operation (such as a cache miss) threatens to halt the processor.

All previous strategies cope with the memory problem by tolerating latencies. Another way of dealing with this problem consists of avoiding latencies. *Memory hierarchies* [53] are the most widespread approach for latency avoidance. It consists of placing small high-speed memories close to the processor and larger slower memory further from the processor. If data that will be used multiple times are stored in the fast memory closer to the processor, then they can be retrieved more quickly in following requests, thus reducing the average memory latency.

The likelihood of finding data in the faster memory levels depends not only on the size, replacement policies and organization of the levels, but also on the inherent locality of reference within the applications. The principle of locality says that if a program refers to any given word in memory, there is a high likelihood that in the near future the program will refer to the same location in memory (temporal locality) or a nearby location (spatial locality). Since most applications exhibit a reasonable amount of locality, memory hierarchies are generally quite useful. The whole hierarchy in a modern virtual memory system may include up to six different memory levels: disk-backing store, main memory, one, two or even three levels of high speed cache memory and the register file<sup>2</sup>.

More recent approaches to avoid memory latency are victim caches and pseudo-associative caches. Victim caches [62] improve the performance of direct-mapped caches through the addition of a small, fully associative cache between the first level cache and the next level in the hierarchy. Pseudo-associative caches [3][19][64][112], however, consist in cache organizations that modify a

<sup>2.</sup> Registers are often considered separate from the rest of the memory hierarchy, because they are managed explicitly by the compiler, however we think, and so we do in this work, that registers can be fruitfully treated as part of the hierarchy.

set-associative cache to achieve an average access time close to that of a direct-mapped cache, thus obtaining the miss rate of set-associative caches and the hit speed of direct-mapped. Basically, victim and pseudo-associative caches both promise to improve miss rate without affecting the processor clock rate.

#### 1.3.2 Compiler Strategies

Due to design and technology limitations, the efficiency of all previous hardware mechanisms and architectural improvements depends on the compiler ability to change the structure of programs for taking full advantage of them. For instance, mechanisms that tolerate memory latencies are effective if the compiler can schedule instruction streams with enough parallelism between the instructions, while latency avoidance mechanisms are effective only when a compiler can determine that values will be reused and should be kept in the fastest level of the memory hierarchy. Thus, to fully realize all recent architectural advances and, therefore, achieve high performance on modern superscalar processors, compilers need to find ILP to utilize machine resources effectively, and they also need to transform the program to achieve a high degree of data locality to maximize the effectiveness of the memory system.

When optimizing a program, the most gains will come from optimizing the regions of the program that require the most time. These regions usually are the repetitive regions that correspond to iterative loops whose loop body contains n-dimensional array variables. In this work we focus on this type of regions.

Several compiler strategies have been developed to exploit a program's ILP and/or to improve the memory hierarchy utilization inside loop nests. These strategies can be classified into two different classes: strategies that change the original data layout of the array variables and strategies based on loop restructuring transformations that reduce the number of executed instructions and/or change the order in which statements are executed.

Strategies that change the original data layout of array variables are padding (or data alignment) and data transformations. Padding [11][82][107] is a technique that involves the insertion of dummy elements in a data structure, while data transformations [10][63][66][92][99] consist on simply reorganizing the original data layout. The goal of both techniques is avoiding self and cross interferences, thus reducing conflict misses and improving the memory hierarchy utilization. These techniques are usually combined with loop restructuring transformations to yield high performance.

Next, we review the most relevant loop restructuring transformations that aim at improving ILP and/or the memory hierarchy utilization [24][79][124]; we note that most of these transformations can be combined together to maximize the effectiveness of the memory system and, at the same time, improve ILP.

Compiler transformations such as inner unrolling<sup>3</sup> [129] and software pipelining [56][79][106] were proposed to improve ILP, but they do not aim at enhancing data locality. Both techniques draw out parallelism between iterations of the original loop body, but they are implemented in different ways. Inner unrolling replaces the body of the loop by several copies of the body and adjusts the loop-control code accordingly. Software pipelining reorganizes loops such that each iteration in the software-pipelined code is made from instructions chosen from different iterations of the original loop. Both transformations, in addition to yielding a better scheduled inner loop with a good degree of parallelism, each reduce a different type of overhead. Inner unrolling reduces the overhead of the loop (the branch and counter-update code) and software pipelining reduces the number of times that the loop is not running at peak speed to once per loop at the beginning and end. Because these techniques attack two different types of overhead, the best performance is usually obtained by combining them.

There are other compiler transformations whose goal is to enhance data locality at the cache level, but not to improve program's ILP. These transformations are loop permutation, loop fusion and loop fission [96][129]. Some programs have nested loops that access data in memory in non-sequential allocated order. Simply permuting the loops in the nest can make the code access the data in the order it is stored, thus improving spatial locality. Loop fusion enhances temporal locality by combining loops when they use the same data [88][113]. Some programs have separate sections of code that access the same arrays, performing different computations on the common array. By fusing the code into a single loop, the data that are loaded into the cache can be used repeatedly before being swapped out. Finally, loop fission (the inverse of loop fusion) can also improve memory locality by breaking up a loop that refers to a large amount of data into a sequence of smaller loops, each of which has disjoint or smaller data requirements. This way, the program's working set is reduced ad therefore data locality improved.

Scalar replacement [20][23] is a code transformation that also enhances data locality, but at the register level. One concern in generating good object code for loops that manipulate subscripted variables is that very few compilers even try to allocate such variables to registers, despite the fact that register allocation is often done very effectively for non-subscripted scalar variables. Scalar replacement finds opportunities to reuse array elements and replaces the reuses with references to scalar temporaries, hence making them available for register allocation.

A compiler transformation which is able both to improve ILP and to enhance data locality is outer unrolling (also called unroll-and-jam) [20][23]. Outer unrolling draws out parallelism between iterations of the original loop body and enhances data locality at the register level in the unrolled dimension of the iteration space. It consists in unrolling an outer loop in a nest and then jamming the resulting inner loops back together. Outer unrolling can introduce more computation into an innermost loop body without a proportional increase in memory references. We note that outer

<sup>3.</sup> We use the term inner unrolling to refer to unrolling to clearly distinguish it from outer unrolling.

unrolling can be applied repeatedly to several loops in a nest and, in this case, data reuse is exploited in all the unrolled dimensions. It is well known that exploiting data reuse in several dimensions of the iteration space, whenever possible, improves the performance of the memory hierarchy [80][97].

Finally, another compiler transformation, and perhaps the most famous one, to enhance data locality is Loop Tiling (also called Blocking) [97] [110][121][128]. Loop tiling has been typically used to enhance data locality at the cache level. It consists in dividing the iteration space defined by the loop structures into regular tiles, creating a blocking of the data arrays. The order in which the tiles are traversed determines the order in which the data blocks are accessed. The idea is to shorten the distance between successive references to the same memory location, so that the probability of finding the associated data in the memory level being exploited is higher.

Futhermore, loop tiling has other interesting properties. First, it exploits data reuse in several dimensions of the iteration space [98][121]. As mentioned before, this capability can improve the effectiveness of the memory level being exploited. Second, by performing multilevel tiling, data locality can be enhanced in several memory levels simultaneously. Multilevel tiling consists in repeatedly applying loop tiling for each level, dividing a tile of a higher level into subtiles. Each level of tiling exploits one level of the memory hierarchy. And third, loop tiling for the register level has the desirable property that it always increases ILP.

Thus, *loop tiling* is a very powerful transformation that has the potential of outperforming the other code transformations mentioned above since it is capable to achieve the three main optimizations mentioned so far:

- improves a program's ILP, when it is applied at the register level,

- exploits data reuse in several dimensions of the iteration space and

- enhances data locality at several memory levels simultaneously.

We want to note that loop tiling is implemented by combining other loop transformations, such as loop permutation, unrolling and scalar replacement. Although loop tiling can be seen as a combination of other transformations, we refer to it as a single transformation because it is a particular combination that yields to blocked algorithms.

As a quick summary, Table 1.1 presents all previous mentioned compiler transformations specifying for each one its main goals (improves ILP and/or data locality), at which level data locality is enhanced and in how many dimensions data reuse is exploited. We want to note that most of the transformations may indirectly achieve other benefits; for instance, scalar replacement might improve ILP by reducing the number of memory instructions executed in the loop body. In Table 1.1, however, we only indicate the main goals of each transformation, ignoring secondary effects that the transformation might have.

| Compiler<br>Transformation | Improves<br>ILP | Improves<br>Data Locality              | Number of reuse<br>dimensions exploited |

|----------------------------|-----------------|----------------------------------------|-----------------------------------------|

| inner unrolling            | Yes             | No                                     |                                         |

| software<br>pipelining     | Yes             | No                                     |                                         |

| loop permutation           | No              | at cache level                         | 1                                       |

| loop fusion                | No              | at cache level                         | 1                                       |

| loop fission               | No              | at cache level                         | 1                                       |

| scalar<br>replacement      | No              | at register level                      | 1                                       |

| outer unrolling            | Yes             | at register level                      | several*                                |

| loop tiling                | Yes             | at several memory level simultaneously | several                                 |

Table 1.1: Summary of the goals of different compiler transformations. (\*) Outer unrolling can be applied to more than one loop in a nest and, in this case, it exploits data reuse in all the unrolled dimensions.

There are several works that focus on combining all these transformation to achieve high performance [24][27][108][122][124]. They try to select the best combination of transformations that yield better performance. The set of transformations that they manipulate to select a good combination is limited by its legality<sup>4</sup> and also by the ability of being able to generate the transformed code.

In this thesis we will focus on the loop tiling transformation, since it is the transformation that individually achieves more performance. The other loop transformations, if taken individually, realize some of the goals that loop tiling achieves, but not as many. Therefore, the main motivation of this thesis will be the improvement of the loop tiling transformation. Of course, loop tiling can sometimes be combined with some of the previous transformations to further improve its performance. For instance, loop fusion can be applied before loop tiling to enhance temporal locality. However, this thesis will look at the performance of the loop tiling transformation in isolation.

#### 1.4 LOOP TILING IN COMMERCIAL COMPILERS

With today's architectures having complex memory hierarchies, it is necessary that the compiler performs tiling at three or more levels (L2-cache, L1-cache and registers) to achieve high performance. Previous work has shown that, when tiling for multiple memory levels, the register level is the most important one, more so than the cache levels [23][58][80], although for loop nests with very large working sets, tiling for various cache levels is also important. Being able to enhance data locality at

<sup>4.</sup> A loop transformation is legal if it does not violate the original data dependences.

the register level is extremely important in today's superscalar microprocessors, since the register level directly feeds the processor functional units. The typical bandwidth provided between the register file and the functional units is three or four times larger than the bandwidth provided by the first level cache. Typically, one can find at least 6 ports in the floating point register file whereas only one or two ports in the first level cache are provided. If the register level is not properly exploited, then the number of first level cache ports bounds processor performance. In general, when performing multilevel tiling the compiler should always include the register level in order to achieve high performance.

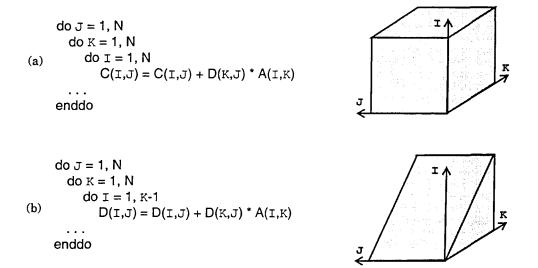

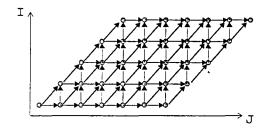

How do current commercial compilers deal with these issues? First of all, let's define a *simple* loop nest as a set of nested loops whose bounds are constant and, therefore, describe a *rectangular* iteration space. On the other hand, we define a *complex* loop nest as a set of nested loops whose bounds are maximum or minimum of affine functions of the surrounding loops iteration variable. This kind of loop nests describe *non-rectangular* iteration spaces. As an example, Fig. 1.4 shows the code and its associated iteration space for both a simple and a complex loop nest. The codes correspond to the SGEMM and the STRMM problems used in Section 1.1.

We have observed that current commercial compilers perform quite well when dealing with simple loop nests. For these codes, compilers essentially perform loop tiling for several memory levels. For small problem sizes they perform tiling only for the register level and, for large problem sizes, where cache levels affects processor performance, they also perform tiling for these other levels. Only when loop tiling is not a *legal* transformation, compilers use combinations of other transformations, such as inner and outer unrolling, software pipelining, loop fusion and loop fission, that are less restrictive from the legality point of view.

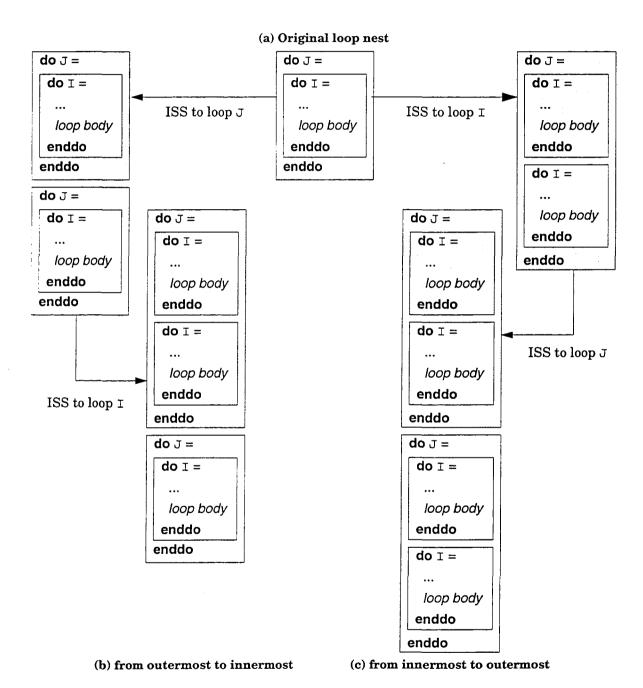

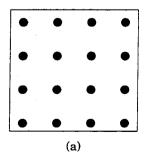

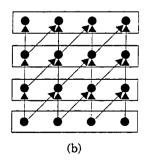

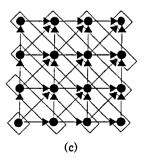

**Figure 1.4:** a) Simple loop nest code and its iteration space shape (SGEMM) b) Complex loop nest code and its iteration space shape (STRMM).

For complex loop nests, however, current compilers perform poorly. For these codes, compilers only perform loop tiling at the cache level. They do not apply tiling to the register level, despite it is legal. Instead, to enhance locality at the this level, they use or combine other transformations, that do not exploit the register level as well as loop tiling.

Now, our question is why compilers do not apply loop tiling at the register level in complex loop nests despite being legal? Tiling for the register level is not generally considered because the transformed loop nest is not easy to rewrite. Generating a transformed tiled loop nest for the register level consists of two steps: rewriting the body of the loop nest and rewriting the loop bounds.

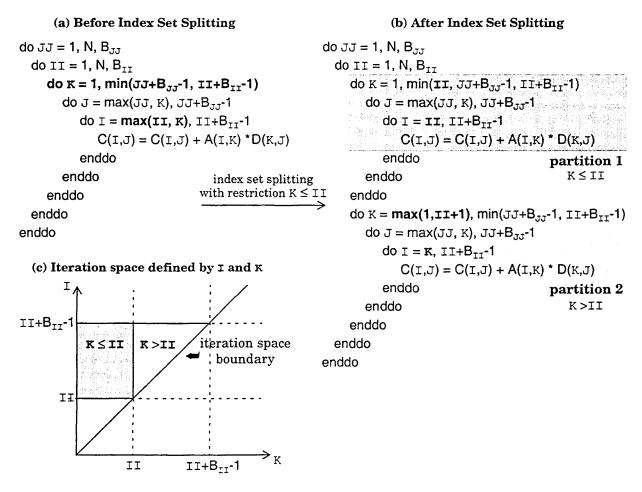

At the register level, after dividing the original iteration space into tiles, it is necessary to rewrite the loop body by fully unrolling the loops that traverse the iterations inside the register tiles, because registers are only addressable using absolute addresses. In complex loop nests, the action of fully unrolling the loops is far from being trivial due to the irregular nature of the iteration space[121]. Currently, production compilers can only perform this unrolling for simple loop nests. In this thesis, we propose an implementation of tiling for the register level that handles arbitrary iteration space shapes and not only rectangular shapes.

Rewriting the loop bounds is also more difficult in complex loop nests than in simple loop nests. The bounds of a tiled loop nest can be *exact* or not. We say that a loop nest has *exact* bounds if it never executes an empty iteration. As an example, the code of Fig. 1.5a has exact loop bounds while the code of Fig. 1.5b has not. Every time K is equal to N, loop I does not perform any iteration. In addition, a loop nest can have *redundant* bounds. We say that a loop bound is *redundant* if it can be removed from the loop and the resulting loop nest executes exactly the same iterations as the original loop nest. In Fig. 1.5c, the lower bound J of loop I is redundant.

Computing exact bounds and avoiding the generation of redundant bounds is critical when multilevel tiling includes the register level. As mentioned before, when tiling is being applied at the register level, it is necessary (after dividing the original iteration space into tiles) to fully unroll the loops that traverse the iterations inside the register tiles. The complexity of these second step of register tiling and the amount of code generated depend on the number of bounds of the loops that have to be fully unrolled, and thus, it is convenient to compute exact and non-redundant bounds when multilevel tiling includes the register level.

Figure 1.5: a) Loop nest with exact bounds b) Loop nest without exact bounds. Every time K is equal to N, loop I does not perform any iteration. c) Loop nest with redundant bounds. The lower bound J of loop I is redundant.

Moreover, another advantage of computing exact and non-redundant bounds is to avoid increasing a program's execution time. If the compiler does not compute exact bounds and generates redundant bounds, a fraction of a program's execution time is wasted in evaluating useless bounds (redundant bounds or bounds of loops that will end up in empty iterations). This fraction of time is usually insignificant, but it can become important if loop tiling is applied to several levels of the memory hierarchy.

Traditionally, exact loop bounds computation has not been performed because its complexity is doubly exponential and, therefore, for certain classes of loops, can be extremely time consuming. Of course, for simple loop nests that define rectangular iteration spaces, the cost of computing exact bounds is "reasonably" cheap. However, this is not the case for complex loop nests defining non-rectangular iteration spaces. In this thesis, we also propose an implementation of multilevel tiling that computes exact bounds, tries to avoid redundant bounds and its cost is sufficiently low that is viable to be implemented in a production compiler.

#### 1.5 THESIS OVERVIEW

This thesis is focused on the study of a code transformation to enhance data locality and to extract ILP from numerical codes. More precisely, we center on the loop tiling transformation applied to loop nests that define *non-rectangular* iteration spaces. For this kind of loop nests, that commonly appear in numerical applications, current compilers are not able to perform multilevel tiling and, thus, high performance is not achieved. In this thesis we show that multilevel tiling can also be applied to loops defining *non-rectangular* iteration spaces so that they achieve high performance on modern microprocessors.

The primary contributions of this thesis are the following:

- The proposal of a general compiler algorithm to perform tiling at the register level in arbitrary iteration space shapes.

- The proposal of a very simple heuristic to make the tile decisions for the level register level when dealing with non-rectangular iteration space.

- The proposal of a new compiler algorithm to compute *exact* loop bounds when multilevel tiling is performed. This algorithm improves upon conventional techniques on its cost, therefore making possible the inclusion of multilevel tiling in production compilers.

- A study of the effects of (1) tiling only for the register level, (2) tiling only for the cache level and (3) tiling for both the register and cache levels and a performance comparison between hand-optimized codes and automatic-optimized codes.

#### 1.6 RELATED WORK

Several other researchers have also worked on code transformation to enhance the data locality and to extract ILP. This section summarizes their work and relates it to ours.

The first work on compiler transformation for maximizing cache locality was from Gallivan et al. [48][49][50]. They present a technique to describe the amount of data that must be in the cache for reuse to be possible. They call this the *reference window*. The window for a dependence describes all of the data that is brought into the cache for the two references from the time that one datum is accessed at the source until it is used again at the sink. A family of reference windows for an array represents all of its elements that must fit in the cache to capture all of reuse. To determine if the cache is large enough to hold every window, the window sizes are summed and compared against the size of the cache. If the cache is too small, blocking transformation can be used to decrease the size of the reference window. Their work basically is focused on analysis of cache and local memory behavior in loop nests to decide if loop tiling is profitable, and they do not give an algorithm for choosing the best tile sizes. Additionally, they do not explain how the tiled code is generated.

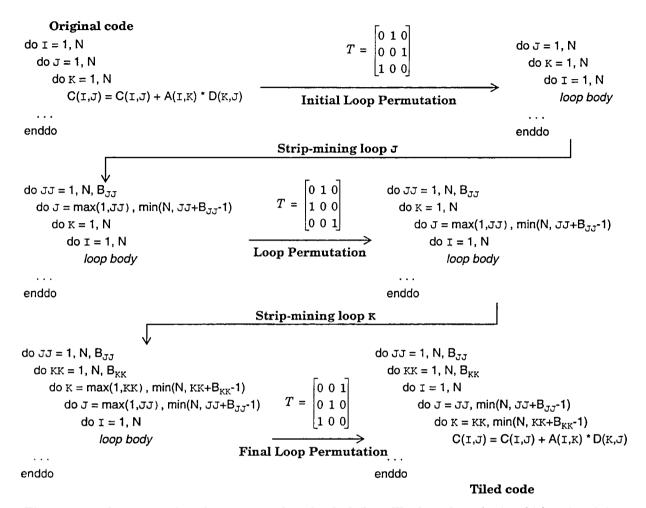

Wolfe's memory performance work [125][126][127][128] has concentrated on developing transformations to reshape loops to improve their cache performance. His loop transformation approach consists of individual loops and statements which can be transformed by a sequence of simple transformations that operate on one or two loops at time. The effectiveness of applying a specific transformation to a given goal is usually easy to measure. Unfortunately, it is often the case that several transformation will need to be applied successively. In this case, the best first transformation to apply is not obvious and the search of the best sequence of transformations must be performed exhaustively. The weakness in his approach is the lack of a decision algorithm to choose which transformation to apply to a nest. Wolfe also shows how tiling (or blocking) can be used to improve the memory performance of program loops and shows that his techniques for advanced loop permutation can be used to tile loops with non-rectangular iteration spaces and loops that are not perfectly nested. In particular, he discusses blocking at the cache level for triangular and trapezoidal shaped iteration spaces, but he does not present an algorithm and does not discuss tiling at the register level.

Wolf et al. [121][122][123] use an alternate approach to Wolfe's proposal based on matrix transformations. They model loop transformations such as loop permutation, reversal and skewing as unimodular transformations on the iteration space. A compound transformation is just a unimodular transformation, being a product of several elementary transformations. This model makes it possible to determine the best compound transformation directly by maximizing some objective function. They also provide a framework for determining memory usage within loop nests and use that framework to apply loop permutation, loop skewing, loop reversal and loop tiling. They give algorithms for

computing the tile size and the best order of the tiles and present a method for determining the bounds of a transformed loop nest after applying a unimodular transformation or loop tiling. Their "compute bound" algorithm is very fast and simple. However the resulting code may contain redundant bounds and the loop bounds are not exact. As mentioned before, not computing exact bounds and the presence of redundant bounds can be negative if the register level is being exploited. Their method is able to perform tiling on several levels of the memory hierarchy, but, at the register level, they only exploit data reuse in one dimension of the iteration space and indicate that tiling more than one dimension is not trivial for complex loop nests. Moreover, they do not propose a method to determine tile sizes at the register level.

Carr et al. [23][24][25][27] discuss promotion of array references into registers (scalar replacement), and tiling for the register level via the unroll-and-jam transformation. As mentioned before, unroll-and-jam enhances data locality at the register level in the unrolled dimension, and it can be applied repeatedly to several loops in a nest to exploit data reuse at several levels. Indeed, applying unroll-and-jam to several loops in a nest is comparable to applying loop tiling at the register level. They use unroll-and-jam for exploiting reuse at the register level and improving ILP and discuss how to implement unroll-and-jam in the presence of triangular and trapezoidal loop nests. For these complex cases, they give the code transformation directly. To this end, they use pattern recognition techniques on the bounds of the loops and when the loop bounds do not match one of his patterns, no general algorithm to split the iteration space into simple ones that could be recognized through patterns is presented. Moreover, to decide the loops to be unrolled-and-jammed, they examine the dependence graph and search which loops carry most true and input dependences. They do not consider other parameters such as iteration space shape.

Porterfield's dissertation [102] contains a study of compiler techniques for improving data cache performance. His work is focused on how the application of various transformations - fission, fusion, permutation, unrolling, loop tiling - change the cache behavior, but he does not study the register level. He also does not deal with the code updating phase. He was also the first to explore software controlled prefetching for uniprocessors [22][102]. He proposed a compiler algorithm for inserting prefetches into dense-matrix codes. Then, Mowry [93][94][95] extended his work by automating the whole process and exploring prefetching for multiprocessors. Techniques for tolerating memory latency such as software prefetching can be combined with loop tiling to cope with whatever memory latency cannot be reduced through locality optimizations.

Two main differences can be pointed out between this thesis and previous work. First, we mostly focus on the "code updating" phase of the optimizing compilers, instead of the "decision algorithms" that determine the best tile sizes and the order of the tiles. Second, we also pay special attention to the register level instead of the cache level while previous work in the literature regarding loop tiling has mostly focused on enhancing data locality at the cache level and exploiting coarse-grain parallelism.

#### 1.7 THESIS ORGANIZATION

This work is organized as follows:

- Chapter 2 gives some background on the loop tiling transformation and presents transformations and assumptions on which our compiler strategies are based.

- Chapter 3 describes our algorithm to perform tiling for the register level in complex loop nests and presents our locality analysis to make the tiling decisions at this level. We also present experiments to validate the effectiveness of our algorithm and compare against other transformations performed by current production compilers.

- Chapter 4 describes our efficient implementation of multilevel tiling to compute exact bounds, that we refer to as Simultaneous Multilevel Tiling. We compare our implementation against conventional techniques in terms of complexity and redundant bounds generated and present some experimental results.

- Chapter 5 presents a detailed evaluation of loop tiling. First, we discuss and evaluate the effect of tiling for one memory level (cache or registers) and tiling for multiple memory levels. In the second part of this chapter, we compare our automatic-optimized codes against the vendor hand-optimized codes and we show how compiler technology can make it possible for complex numerical codes to achieve high performance on modern microprocessors.

- Finally, Chapter 6 summarizes the contributions of this thesis and present open areas for future research.

| , |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

# LOOP TILING BASICS

#### Summary

In this chapter we gives some background on the loop tiling transformation. We review previous work related to loop tiling and presents the framework and assumptions on which our compiler strategies are based on. The chapter is organized as follows: In Section 2.1 we explain in what loop tiling consists and illustrate it with an example. In Section 2.2 we give some preliminary concepts needed for a better understanding of the following sections. Section 2.3 explains the three challenges that confront a compiler to apply loop tiling to a loop nest: dependence analysis, locality analysis and generating the transformed code. Finally, Section presents the assumptions on which our compiler strategies are based on and Section 2.5 summarizes this chapter.

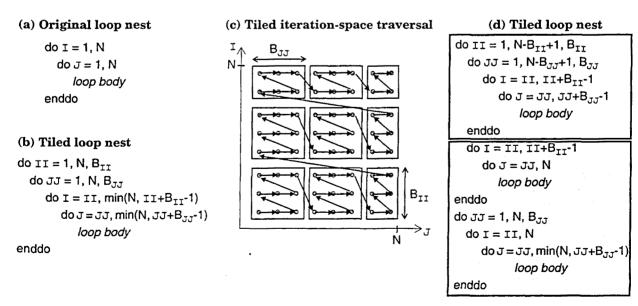

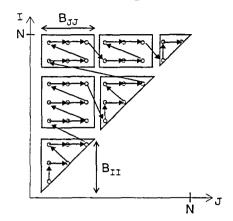

#### 2.1 THE LOOP TILING TRANSFORMATION

Loop Tiling is a well known loop transformation that a compiler can use to automatically create block algorithms. The advantage of block algorithms is that, while computing within a block, there is a high degree of data locality, allowing better register, cache or memory hierarchy performance [1][39][48][67][121][127]. Tiling is also a good paradigm for multiprocessors [123][128]. If tiling can be done so that different blocks are independent of each other, then different blocks can be assigned to different processors. In this chapter, however, we only focus on the loop tiling ability to enhance data locality.

To illustrate tiling and its importance, we present a simple example program and show how loop tiling enhances data locality. The example used is a matrix multiplication program, shown in Fig. 2.1a. In this code, the same row of A is used repeatedly by iterations of the middle (J) loop. If N is large relative to the cache size, so that an entire row of an array does not fit into the cache, then elements of the row may not be in the cache between reuses. For the D matrix, reuses of array elements occur in the outermost (I) loop. Between reuses of elements in D, the whole array is brought into the cache, which means that references to D will not hit in the cache. In the case of improving register utilization, it suffices to note that a register file is typically much smaller than N, so that the nest will not significantly benefit from register allocation of elements of either D or A.

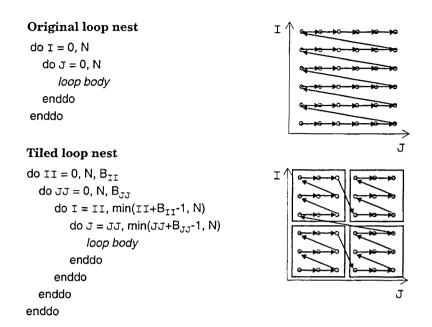

Loop tiling consists of dividing the iteration space defined by the loop structures into regular tiles (or blocks) of some size and shape (typically squares or cubes), and then traversing the tiles to cover the whole iteration space. Loop tiling alters the order in which individual iterations are executed so that iterations from loops of the outer dimensions are executed before completing all the iterations of the inner loop. Thus, the distance between successive references to the same memory location is shortened and the probability of finding the associated data in the memory level being exploited is higher.

```

(a) Original code

(b) Tiled code

do I = 1, N

do JJ = 1, N, B_{JJ}

do J = 1, N

do KK = 1, N, B_{KK}

do K = 1, N

do I = 1, N

C(I,J) = C(I,J) + A(I,K) * D(K,J)

do J = JJ, min(N, JJ+B_{TJ}-1)

do K = KK, min(N, KK+B_{KK}-1)

enddo

enddo

C(I,J) = C(I,J) + A(I,K) * D(K,J)

enddo

enddo

enddo

enddo

enddo

enddo

```

Figure 2.1: (a) Original code of matrix multiplication C=A x D. (b) Code after loop tiling.

Loop Tiling Basics 37

Figure 2.1b shows the matrix multiplication program after loop tiling. Tiling reduces the number of intervening iterations between data reuses. Therefore, reuses of data occur more closely in time and the amount of data fetched between data reuses is reduced. This allows reused data to still be in the cache or register file, and hence reduces memory accesses. The tile size  $B_{JJ} \times B_{KK}$  can be chosen to allow maximum reuse for a specific level of the memory hierarchy.

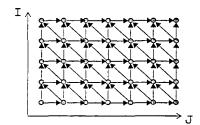

Figure 2.2a shows how data items are accessed in the non-tiled matrix multiplication previously shown in Fig. 2.1a. The same element C(I,J) is used by all iterations of the innermost (K) loop; it can be register allocated and is fetched from memory only once. The same row of A accessed in the innermost loop is reused in the next iteration of the middle (J) loop, and the same column of D is reused in the outermost (I) loop. Whether the data remains in the cache at the time of reuse depends on the size of the cache. Unless the cache is large enough to hold at least one NxN matrix, the data D will have been displaced before reuse. If the cache cannot hold even one row of the NxN matrix, then A data in the cache will also not be reused. In this latter case (worst case),  $2N^3+N^2$  words of data need to be read from main memory in  $N^3$  iterations. This high ratio of memory fetches to numerical operations significantly degrades machine performance, since memory fetches are of high latency.

By comparison, Fig. 2.2b shows how data items are accessed in the tiled matrix multiplication of Fig. 2.1b. Essentially, the patterns are the same as before, but operations are only performed on a  $B_{JJ} \times B_{KK}$  submatrix of D. If  $B_{JJ}$  and  $B_{KK}$  are chosen properly, this submatrix fits in the cache and can be reused over and over. This allows all three matrices to have excellent reuse; ignoring interferences in the cache, the total main memory words accessed will be  $(N^3/B_{JJ})+(N^3/B_{KK})+N^2$ , which is an improvement of about a factor of  $B_{JJ}$  (assuming  $B_{JJ} \approx B_{KK}$ ) over the non-tiled case.

Figure 2.2: Data access pattern in (a) untiled and (b) tiled matrix multiplication.

Loop tiling is a powerful transformation that enhances locality of reference. Although we have only shown how loop tiling enhances locality at the cache level, loop tiling can also be applied at other memory levels, including the register file. For instance, by taking a small blocking size such that the block can be held in registers, we can reduce the number of loads and stores in a program. Chapter 3 deals with tiling for the register level.

#### 2.2 PRELIMINARY CONCEPTS

In this section, we give a brief overview of some important concepts that are used throughout this thesis. In particular, concepts that are useful for program analysis and program restructuring.

#### **Loop Nest Representation**

We consider algorithms specified by a number of nested loops with the following form:

do

$$I_1 = L_1$$

,  $U_1$

do  $I_2 = L_2$ ,  $U_2$

...

do  $I_n = L_n$ ,  $U_n$

loop body

enddo

The bounds of the loops are of the form:

$$\mathsf{L}_{i}^{\cdot} = \max(l_{i,\,0}, l_{i,\,1}, l_{i,\,2}, \ldots) \qquad \qquad \mathsf{U}_{i} = \min(u_{i,\,0}, u_{i,\,1}, u_{i,\,2}, \ldots)$$

and  $l_{i,j}$ ,  $u_{i,j}$  are linear functions that can be expressed as follows:

$$l_{i,j} = \sum_{k=1}^{i-1} a_{i,j}^k \cdot \mathbf{I}_k + \Upsilon_{i,j} \qquad \qquad u_{i,j} = \sum_{k=1}^{i-1} b_{i,j}^k \cdot \mathbf{I}_k + \varphi_{i,j}$$

where  $a_{i,j}^k, b_{i,j}^k \in Z$   $(1 \le k \le i-1)$ ,  $\Upsilon_{i,j}$  and  $\varphi_{i,j}$  are constants or parameters (problem size) and  $\mathbb{I}_k$   $(1 \le k \le i-1)$  are loop control variables.

#### **Iteration Space**

Any single iteration of the n-deep loop nest can be represented by a n-dimensional vector,

$$\vec{\mathbf{I}} = (\mathbf{I}_1, ..., \mathbf{I}_n)^t$$

where each component of this vector is associated with one of the loops. The leftmost component of the vector is associated with the outermost loop and the rightmost component with the innermost loop.

Figure 2.3: (a) Example loop nest. (b) Bounded Iteration Space (BIS).

The set of iterations determined by the bounds of the n nested loops is a convex subset of  $Z^n$ . We call this set the *Bounded Iteration Space* (BIS):

BIS =

$$\{\overrightarrow{\mathbf{I}} = (\mathbf{I}_1, ..., \mathbf{I}_n)^t | (\mathbf{L}_1 \le \mathbf{I}_1 \le \mathbf{U}_1, ..., \mathbf{L}_n \le \mathbf{I}_n \le \mathbf{U}_n) \}$$

Figure 2.3 shows an example of a loop nest (2.3a) and the corresponding BIS (2.3b).

The BIS can be specified in matrix form [54][77]. Taking into account the semantics of a do-loop, each of the linear functions  $l_{i,j}$  and  $u_{i,j}$  defines an inequality of the form:

$$\begin{split} &\sum_{k=1}^{i-1} a_{i,j}^k \cdot \mathbf{I}_k + \Upsilon_{i,j} \leq \mathbf{I}_i \\ &\mathbf{I}_i \leq \sum_{k=1}^{i-1} b_{i,j}^k \cdot \mathbf{I}_k + \phi_{i,j} \end{split}$$

Putting all these inequalities together, the following matrix inequality can be built:

$$A \cdot \vec{1} \leq \beta$$

Every row of matrix A defines a lower bound component  $l_{i,j}$  (or an upper bound component  $u_{i,j}$ ) and it is built from coefficients  $a_{i,j}^k$  and -1 (or  $-b_{i,j}^k$  and 1). The n elements of vector  $\vec{1}$  are the iteration control variables  $\mathbf{I}_i$ , and  $\beta$  is a vector whose components are the coefficients  $-\Upsilon_{i,j}$  (or  $\phi_{i,j}$ ).

As an example, the bounds of the BIS shown in Fig. 2.3 are represented by the following matrix inequality:

$$\begin{array}{ccc} 0 \leq \mathtt{I}_1 & & \mathtt{I}_1 \leq 4 \\ 0 \leq \mathtt{I}_2 & & \mathtt{I}_2 \leq 6 \end{array} \Rightarrow \left[ \begin{array}{c} 1 & 0 \\ 0 & 1 \\ -1 & 0 \\ 0 & -1 \end{array} \right] \cdot \left[ \begin{array}{c} \mathtt{I}_1 \\ \mathtt{I}_2 \end{array} \right] \leq \left[ \begin{array}{c} 4 \\ 6 \\ 0 \\ 0 \end{array} \right]$$

### **Data Dependences**

Data dependence relations are used by the compiler to represent the essential ordering constraints among statements and the reuse of values in a program. We say that a dependence exits between two references if there exits a control-flow path from the first reference to the second and both references access the same memory location [76]. A dependence is

- a true dependence if the first reference writes to the location and the second reads from it,

- an anti-dependence if the first reference reads from the location and the second writes to it,

- an output dependence if both references write to the location, and

- an input dependence if both references read from the location.

When a code is transformed for optimization, the relative order of reads and writes to a particular memory location must be preserved; if not, the transformed code could produce incorrect results. In particular, true, anti and output dependences must be preserved. Input dependences, however, do not need to be preserved, but it is important to identify them when evaluating reuse of values in a program. Next, we introduce the terminology and notation used to represent data dependence relations in loops.

In loops, the data dependence relations are represented by n-dimensional vectors called dependence vectors:  $\vec{d} = (\delta_1, ..., \delta_n)^t$ .

Each component of a dependence vector is associated with one of the n nested loops, from the outermost to the innermost loop (left to right). The dependence vectors can provide different types of information (distances  $(\delta_i \in Z)$ ), directions  $(\delta_i = \{<, >, =, *\})$ , etc.) depending on the goals of the dependence analysis [125].

If the dependence vector provides distances, then each component of the vector is the number of iterations of the corresponding loop that separates two consecutive accesses to the data item associated to the dependence. For example, given the loop nest of Fig. 2.3a, the true dependence from  $A(I_1,I_2)$  to  $A(I_1-1,I_2)$  has a distance vector of (1,0), the true dependence from  $D(I_1,I_2)$  to  $D(I_1-1,I_2+1)$  has a distance vector of (1,-1), the anti-dependence from  $D(I_1,I_2+1)$  to  $D(I_1,I_2)$  has a distance vector of (0,1) the true dependence from  $A(I_1,I_2)$  of the first statement to  $A(I_1,I_2)$  of the second statement has a distance vector of (0,0) and the input dependence from  $A(I_1,I_2)$  of the second statement to  $A(I_1-1,I_2)$  of the first statement has a distance vector of (1,0).

If the dependence vector provides directions, then each component of the vector is the sign of the data dependence distance. Using the notation proposed by Wolfe [125], a forward direction "<" means that the dependence crosses an iteration boundary forward (from iteration i to iteration i+1, for example), that is, the sign of the distance is positive. A backward direction ">" means that the dependence crosses an iteration boundary backward (from iteration i to iteration i-1), that is, the sign

of the distance is negative. An equal direction "=" means that the dependence does not cross an iteration boundary, that is, the dependence distance is zero. And an asterisk "\*" is used when the direction is unknown or when all three of <, >, = apply. This annotation for data dependence relations is simpler but less precise than distance vectors.

The loop associated with the outermost (leftmost) non-zero distance vector entry is said to be the carried loop and if all distance vector entries are zero, the dependence is loop independent. In the example above, there are three dependences carried by loop  $\mathbb{I}_1$ , one dependence carried by  $\mathbb{I}_2$  and one loop independent dependence.

Given a loop nest, all dependence vectors are always lexicographically positive  $(\overrightarrow{d} \ge \overrightarrow{0})$ . This means that, if the dependence vector provides distances, then, the first non null component of the vector is positive and, if the dependence vector provides directions (following the previous notation), the first component different from =, must be equal to <.

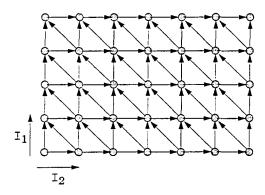

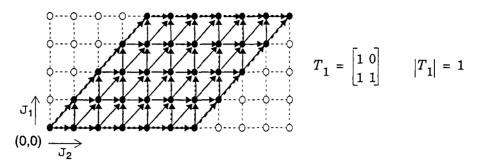

Another concept is the *iteration space dependence graph* [129] that represents the constraints that prevent reordering of iterations of a loop. The iteration space associated with a loop contains one point for each iteration of the loop. If any statement in one iteration of the loop depends on any statement in a different iteration of the loop, that is, if there is a true, anti or output dependence that is not loop independent, the dependence would be represented by an arrow from the source iteration to the target iteration (input dependences do not prevent reordering of iterations). The iteration space dependence graph of the example in Fig. 2.3a is shown in Fig. 2.4. Note that the original execution order preserves dependences.

Figure 2.4: Iteration space dependence graph of the code in Fig. 2.3a

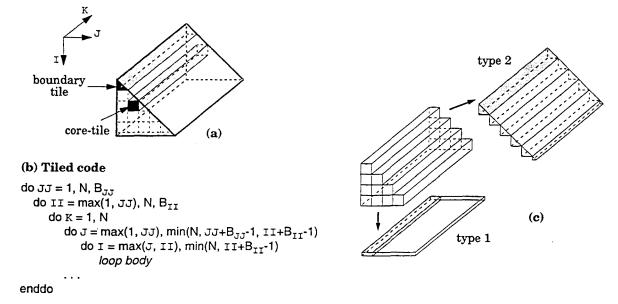

**Figure 2.5:** TIS obtained through the unimodular transformation  $T_1$ .