## MULTILEVEL TILING FOR NON-RECTANGULAR ITERATION SPACES

#### Marta Jiménez

Departamento de Arquitectura de Computadores Universitat Politècnica de Catalunya Barcelona (Spain). March, 1999

A THESIS SUBMITTED IN FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE Doctor por la Universitat Politècnica de Catalunya

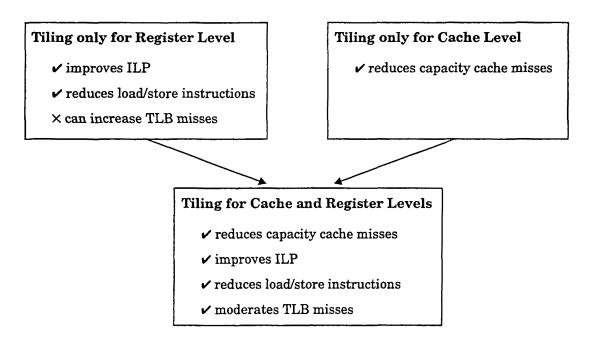

#### SIMULTANEOUS MULTILEVEL TILING

#### Summary

This chapter presents a new cost-effective algorithm to compute exact loop bounds when Multilevel Tiling is applied to a loop nest having affine functions as bounds. Traditionally, exact loop bounds computation has not been performed because its complexity is doubly exponential on the number of loops in the multilevel tiled code and, therefore, for certain classes of loops, can be extremely time consuming. Although computation of exact loop bounds is not very important when tiling only for cache levels, it is critical when tiling includes the register level. As shown in Chapter 3, both the cost of tiling for the register level and the amount of code generated depend on the number of loop bounds in the multilevel tiled code. This chapter presents a new Multilevel Tiling technique that computes exact loop bounds whose complexity is much lower than the complexity of conventional techniques. To achieve this lower complexity, our technique deals simultaneously with all levels to be tiled, rather than applying tiling level by level as is usually done. This chapter will compare our implementation against conventional techniques in terms of complexity and loop bounds generated and present some experimental results.

#### 4.1 INTRODUCTION

Loop Tiling is a transformation that a compiler can use not only to achieve data locality in different levels of the memory hierarchy [27][83][97][122], but also to exploit parallelism [69][84][123]. With today's architectures having complex memory hierarchies and multiple processors, it is quite common that the compiler has to perform tiling at four or more levels (parallelism, L2-cache, L1-cache and registers) in order to achieve high performance.

Multilevel tiling consists of dividing a tile of a higher level into smaller subtiles, where each level of tiles exploits one level of the memory hierarchy or one level of parallelism. As shown in Chapter 2, conventional tiling techniques implement one level of tiling using repeatedly the strip-mining and the loop permutation transformations [129]. Then, to implement multilevel tiling several researchers propose applying tiling level by level [28][121], going from the outermost (parallelism) to the innermost level (registers).

Previous research in multilevel tiling code generation can be divided in two main groups: techniques that compute the resulting tiled loop nest with exact loop bounds [7][77] and techniques that do not compute exact loop bounds [122]. We say that a loop nest has *exact* bounds if it never executes an empty iteration (recall the example of Fig. 1.5 on page 29). Clearly, a loop nest with exact bounds is more efficient because the loop will not waste time in empty iterations. However, to date, the drawback of generating exact loop bounds was that all techniques known were extremely expensive and, thus, difficult to integrate in a production compiler.

Another problem related to the generation of multilevel tiled loop nests is the generation of redundant bounds [5][16]. We say that a loop bound is redundant if it can be removed from the loop and the resulting loop nest executes exactly the same iterations as the original loop nest. Current techniques able to eliminate redundant bounds are also very expensive in terms of compilation time and, as above, have not been included in production compilers.

Solving the problems of exact and redundant bounds would be very beneficial for two main reasons: first, as just mentioned, it avoids increasing a program's execution time. If the compiler does not compute exact bounds and generates redundant bounds, a fraction of a program's execution time is wasted in evaluating useless bounds (redundant bounds or bounds of loops that will end up in empty iterations). This fraction of time is insignificant if tiling is applied to rectangular iteration spaces or for one or two levels of the memory hierarchy. However, it can be very important if tiling is applied to non-rectangular iteration spaces and for several levels of the memory hierarchy.

Second, and most important, computing *exact* bounds and avoiding the generation of redundant bounds is critical when multilevel tiling includes the register level. The reason is that, as shown in Chapter 3, the number of times that Index Set Splitting is applied and the amount of code generated both depend polynomially on the number of bounds of the loops that have to be fully unrolled (the

innermost loops after tiling). If the number of generated loop nests increases excessively, the compiler might waste a lot of time performing the instruction scheduling and the register allocation of loop nests that will be never executed. Thus, when multilevel tiling includes the register level, it is convenient to compute exact bounds and to eliminate redundant bounds, at least in the innermost loops.

Traditionally, exact loop bounds computation has not been performed because its complexity is doubly exponential on the number of loops in the multilevel tiled code and, therefore, for certain classes of loop nests, can be extremely time consuming. Of course, simple loop nests that define rectangular iteration spaces, incur in the best-case complexity and, for this type of loop nests, the cost of computing exact bounds is linear on the number of loops in the multilevel tiled code. However, this is not the case for complex loop nests defining non-rectangular iteration spaces. These complex loop nests are commonly found in linear algebra programs or can arise as a result of applying transformations such as loop skewing<sup>1</sup>. Moreover, conventional multilevel tiling implementations generate many redundant bounds in the innermost loops and eliminating these redundant bounds is also a very time consuming job that can increase a program's compile time significantly [5][16].

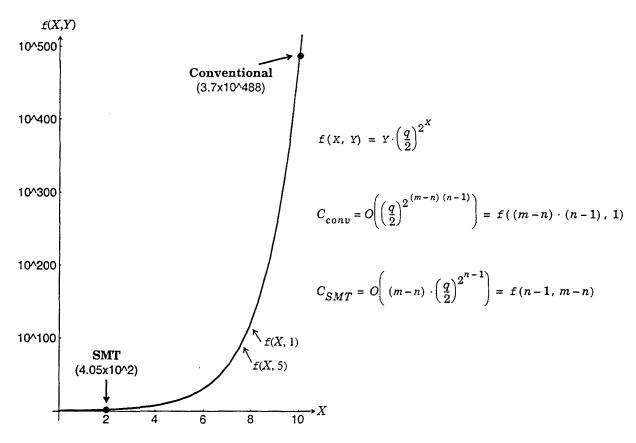

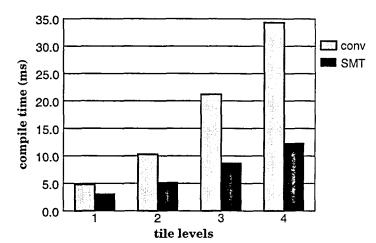

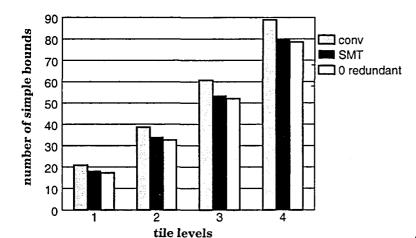

In this chapter we present a new implementation of multilevel tiling that computes exact loop bounds at a much lower complexity than traditional techniques. Moreover, our implementation generates less redundant bounds in the multilevel tiled code and allows removing the remaining redundant bounds in the innermost loops at a much lower cost than traditional implementations. Using our algorithm, tiling for the register level becomes viable even in the face of complex loop nests and/or when tiling for many levels. The main idea behind our algorithm is that we deal with all levels to be tiled simultaneously, instead of applying tiling level by level as traditional implementations do. We evaluate analytically the complexity of our implementation and show that it is proportional to the complexity of performing a loop permutation in the original loop nest, while conventional techniques have much larger complexities. We then compare our implementation against traditional techniques for typical linear algebra codes having very simple affine functions as bounds and show that our method is between 1.5 and 2.8 times faster. Moreover, for loop nests having not so simple bounds<sup>2</sup> (but still bounds commonly found in linear algebra programs), the speedups achieved can be as high as 2300. We also compare both implementations in terms of redundant bounds generated and cost of eliminating these redundant bounds. We show that eliminating redundant bounds in a multilevel tiled code generated with our proposal is between 2.2 and 11 times faster than in a code generated with conventional techniques.

The rest of this chapter is organized as follows. In Section 4.2 we briefly review how conventional techniques implement multilevel tiling and evaluate their complexity. In Section 4.3 we show how multilevel tiling can be performed dealing with all levels simultaneously. In Section 4.4 we give our

<sup>1.</sup>As shown in Chapter 2, loop skewing is sometimes necessary to allow loop tiling to be applied.

<sup>2.</sup> Bounds that are affine functions of multiple outer loop index variables

efficient implementation of multilevel tiling and in Section 4.5 we evaluate its complexity. In Section 4.6 we show how our technique avoids the generation of some special redundant bounds and reduces the cost of eliminating the remaining redundant bounds. In Section 4.7 we compare our implementation against conventional techniques in terms of complexity, number of redundant bounds generated and cost of eliminating redundant bounds. In Section 4.8 we present the previous work related to multilevel tiling and, in Section 4.9, we summarize this chapter.

Finally, we want to note that, in this chapter, multilevel tiling implementation refers only to the compilation phase of updating the transformed loop nest, that is, it refers to computing the loop bounds in the final tiled code.

#### 4.2 CONVENTIONAL TILING IMPLEMENTATION

In this section we briefly review how a conventional technique implements multilevel tiling and we evaluate its complexity.

From now on, we assume that the loop bounds in the original code are max or min functions of affine functions of the surrounding loops iteration variables. We will refer to each affine function as a *simple bound*. We also assume that the loop nest to be tiled is fully permutable and perfectly nested. Extensions to handle non-perfectly nested loops were explained in Chapter 2. Another important assumption is that the bounds in the original code are exact. If they were not exact, it would be necessary to apply the Fourier-Motzkin Elimination algorithm<sup>3</sup> to obtain the exact bounds [16][77].

#### 4.2.1 Implementation

As shown in Chapter 2, conventional tiling techniques implement one level of tiling using two well-known transformations: strip-mining and loop permutation [123][129]. Strip-mining is used to partition one dimension of the iteration space into strips and the loop permutation is used to establish the order in which the iterations inside the tiles are traversed. To perform one level of tiling, it is usually necessary to partition the iteration space in more than one dimension (multi-dimensional tiling). Conventional techniques apply strip-mining and loop permutation repeatedly, as many times as dimensions have to be partitioned<sup>4</sup>.

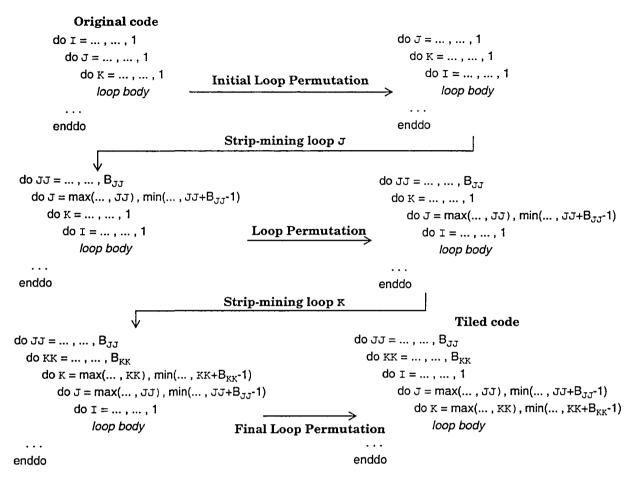

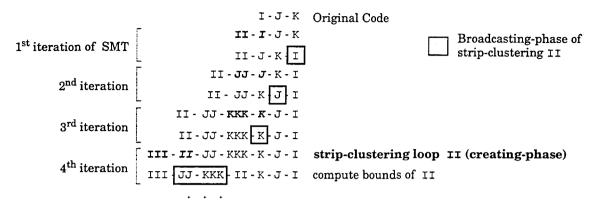

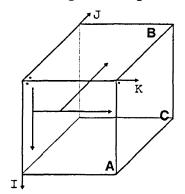

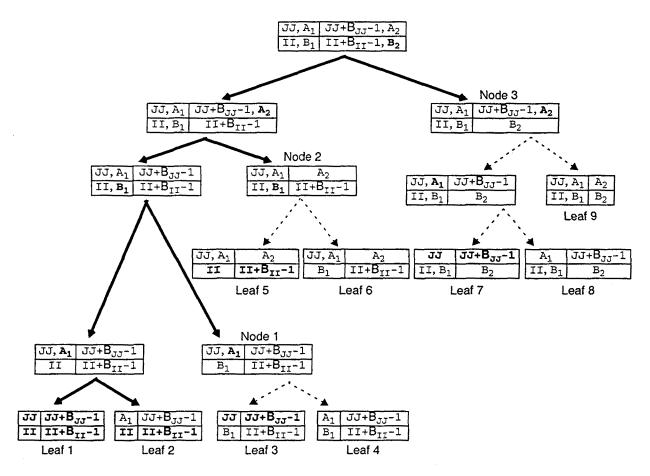

Figure 4.1 reviews how conventional tiling implementations work. We are tiling two dimensions of the 3-dimensional iteration space (two-dimensional tiling) where  $B_{JJ}$  and  $B_{II}$  are the tile sizes in each dimension. Conventional implementations perform both transformations (strip-mining and loop permutation) as many times as dimensions have to be partitioned. Strip-mining decomposes a loop

<sup>3.</sup>By applying the Fourier-Motzkin Elimination algorithm to the original code, independently of whether a loop permutation is performed or not, the bounds of the Minimum Convex Space described by the loop structure are obtained.

<sup>4.</sup>A previous loop permutation must be performed if the loop order of the original loop nest is not such that the outermost loop is the loop to be strip-mined first.

Figure 4.1: Conventional implementation of one level of tiling. We show the order in which strip-mining and loop permutation are applied to partition two dimensions of the 3-dimensional iteration space (two-dimensional tiling).  $B_{JJ}$  and  $B_{II}$  are the tile sizes in each dimension.

into two loops where the outer loop steps between tiles and the inner loop traverses the points within a tile. After strip-mining, a loop permutation is performed to order the inner loops (the loops that traverse the points within a tile) such that the next loop to be strip-mined becomes the outermost of them. After strip-mining all desired loops, a final loop permutation is required to order the inner loops as desired for the final code. In the final tiled code, the outer loops are the loops that step between tiles (from now on, we will refer to them as *tile-loops* or TI-loops for short) and the inner loops are the loops that traverse the points within the tiles (from now on, we will refer to them as *element loops* or EL-loops<sup>5</sup> for short). For further details refer to Chapter 2, Section 2.3.3.

The loop bounds after strip-mining are directly obtained by applying the formula of strip-mining (see Fig. 4.5 on page 134). The loop bounds after a loop permutation can be obtained using the theory of unimodular transformations [13][121], since the loops involved in the permutation are always loops

<sup>5.</sup>In Chapter 3, we distinguished between the non-tiled loop and the *element loops* that traverse the iterations inside the register tiles. In this chapter, however, we refer to the non-tiled loop as an EL-loop.

that have steps equal to 1 and, therefore, they define a convex iteration space. To compute the exact bounds, the Fourier-Motzkin Elimination algorithm is used when the loop permutation unimodular matrix is applied [121][129]. Finally, recall that it is not necessary to rewrite the loop body because (1) the strip-mining transformation does not modify the loop body and (2) although the loop permutation does, we use in the transformed code the same names for the loop iteration variables as in the original code.

Multilevel tiling has been implemented by applying tiling level by level [28][121], going from the outermost (i.e., parallelism) to the innermost level (i.e., register level). As an example, in Fig. 4.1 another level of tiling can be performed by applying tiling again to loops I, J and K of the resulting code.

#### 4.2.2 Complexity

The most expensive steps of conventional implementations of tiling are the loop permutation transformations or, more precisely, the steps needed to compute the exact bounds using the Fourier-Motzkin Elimination algorithm (FM algorithm) [7][16][77]. To better clarify the context of this section we first briefly review how the Fourier-Motzkin algorithm is applied to compute the exact bounds and we also review its complexity. The FM algorithm is explained in Appendix A.

#### Fourier-Motzkin Elimination Algorithm

Let lp and bd be the number of loops and simple bounds in a loop nest before applying a loop permutation transformation, respectively. The FM algorithm is an algorithm that iterates lp-1 times and computes the exact loop bounds in the transformed code from innermost loop to outermost loop. In each iteration of FM, two different steps are performed:

- In the first step, all simple bounds of the yet-to-be-processed loops are examined. All simple bounds that are affine functions of the loop iteration variable being solved become simple bounds of this loop.

- In the second step, each of the lower simple bounds of the iteration variable solved in the first step is compared with each of the upper simple bounds. These comparisons generate inequalities that might become new simple bounds of the yet-to-be-processed loops. Note that in the second step of the FM algorithm, the number of simple bounds in each iteration can grow quadratically in the worst case [129].

Let's now examine the complexity of the FM algorithm. In the worst case, the first loop iteration variable to be solved is involved in the bd simple bounds of the loop nest. After the first step of FM, the loop iteration variable can have bd/2 lower simple bounds and bd/2 upper simple bounds. Comparing

<sup>6.</sup> The bounds of the outermost loop are obtained directly after the FM algorithm has finished.

each of the lower simple bounds with each of the upper simple bounds may give rise to  $(bd/2)^2$  new inequalities. If half of the  $(bd/2)^2$  new inequalities were lower simple bounds of the next loop iteration variable to be solved and the other half were upper simple bounds, comparing all of them would result in  $(bd^2/8)^2$  inequalities. Therefore, since all bd simple bounds could potentially involve all lp iteration variables, the complexity of the FM algorithm is:

$$C_{FM} = O\left(\frac{bd^{2^{(lp-1)}}}{2^{(2^{lp}-2)}}\right) \approx O\left(\left(\frac{bd}{2}\right)^{2^{(lp-1)}}\right)$$

Thus, the complexity of the FM algorithm depends doubly exponentially on the number of loops involved in the permutation.

#### Complexity of Conventional Implementations of Multilevel Tiling

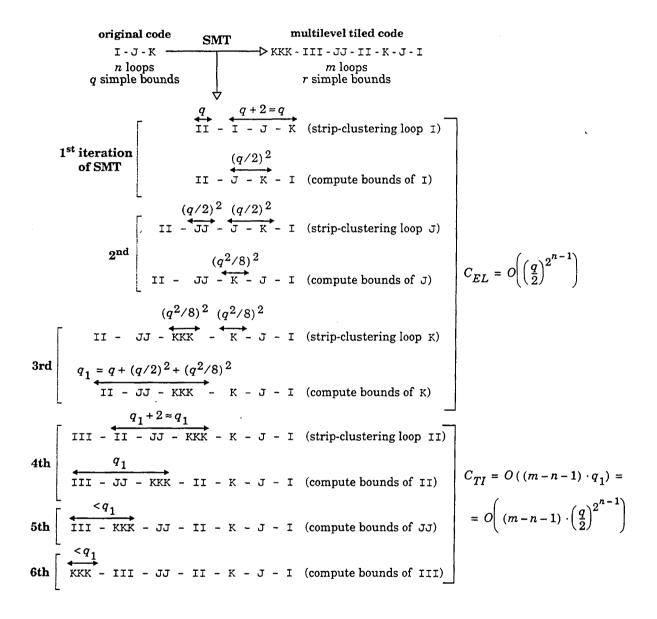

We now turn to the cost analysis of conventional implementations of multilevel tiling. Let n and q be the number of loops and simple bounds in the original loop nest, respectively, and let m be the number of loops in the code after multilevel tiling.

A conventional implementation of multilevel tiling executes (m-n) times the FM algorithm on a set of n loops (the n innermost loops). In the worst case, the number of simple bounds involved the first time the FM algorithm is executed is q+2 (q simple bounds of the original code and 2 simple bounds introduced by the previously applied strip-mining). Thus, after the loop permutation, the n innermost EL-loops together can potentially have  $q_1$  simple bounds, where:

$$q_1 = (q+2) + \left(\frac{(q+2)^2}{2^2}\right) + \dots + \frac{(q+2)^{2^{n-1}}}{2^{2^n-2}} \approx \frac{q^{2^{n-1}}}{2^{2^n-2}} \approx \left(\frac{q}{2}\right)^{2^{n-1}}$$

The next execution of the FM algorithm will deal with  $q_1 + 2 \approx q_1$  simple bounds. Note that each time the FM algorithm is executed, the total number of simple bounds in the n innermost loops together could increase, in the worst case, doubly exponentially. Therefore, the complexity of conventional multilevel tiling techniques is:

$$O\!\!\left( \left( \frac{q}{2} \right)^{2^{n-1}} + \left( \frac{q_1}{2} \right)^{2^{n-1}} + \ldots + \left( \frac{q_{(m-n-1)}}{2} \right)^{2^{n-1}} \right) \approx O\!\!\left( \left( \frac{q}{2} \right)^{2^{n-1}} + \left( \frac{q}{2} \right)^{2^{2n-2}} + \ldots + \left( \frac{q}{2} \right)^{2^{(m-n)\,n-\,(m-n\,))}} \right)$$

Rounding off this expression to the complexity of the last execution of the FM algorithm, it can be expressed by the following formula:

$$C_{conv} = O\left(\left(\frac{q}{2}\right)^{2^{(m-n)(n-1)}}\right)$$

Note that the complexity of conventional multilevel tiling depends doubly exponentially not only on the number of loops involved in the loop permutation, but also on the number of times the FM algorithm is executed (number of TI-loops in the final code).

#### 4.3 SIMULTANEOUS MULTILEVEL TILING

In this section we will show how multilevel tiling can be implemented to deal with all levels simultaneously. The idea behind our Simultaneous Multilevel Tiling algorithm (SMT) consists in applying first strip-mining to all loops at all levels and, afterwards, performing once a single loop permutation transformation to obtain the desired order of the loops.

After applying strip-mining to all loops at all levels, we will obtain a new loop nest that describes a non-convex iteration space. Then, we want to apply a loop permutation transformation to this new loop nest. Although there has been much work [45][85][87][105] addressing the problem of rewriting in a systematic way a loop nest according to a non-singular transformation, we cannot make a direct use of these non-singular transformation theories, because they always assume that the source iteration space is a convex space. In our case, however, the source iteration space is non-convex. In this section, we will describe a method to obtain the transformed iteration space when applying a loop permutation transformation to the non-convex space obtained after applying strip-mining to all loops at all levels.

This section is organized as follows: First, we present the framework where we develop our technique. Second, we show how strip-mining is applied to all loops at all levels. Third, we will describe the method needed to obtain the transformed iteration space when applying the loop permutation transformation to the non-convex space. Fourth, we summarize all steps performed by the SMT algorithm and, finally we give an example to illustrate the whole transformation process.

#### 4.3.1 Framework

As we have already explained in Chapter 2, the set of iterations determined by the bounds of n nested loops is a convex subset of  $\mathbb{Z}^n$ , and we will refer to it as BIS (Bounded Iteration Space):

BIS =

$$\{\overrightarrow{\mathbf{I}} = (\mathbf{I}_1, ..., \mathbf{I}_n)^t | (\mathbf{L}_1 \le \mathbf{I}_1 \le \mathbf{U}_1, ..., \mathbf{L}_n \le \mathbf{I}_n \le \mathbf{U}_n) \}$$

where  $\vec{1}$  is a *n*-dimensional vector which represents any single iteration of the *n*-deep loop nest and  $L_i$  ( $U_i$ ) is the lower (upper) bound of loop  $I_i$ . The bounds of the loops are max or min functions of affine functions of the surrounding loops iteration variables (i.e. they define a non-rectangular iteration space).

The BIS can be specified in a matrix form [54][77] as follows:  $A \cdot \vec{1} \leq \beta$ , where each row of matrix A and vector  $\beta$  has the coefficients of the loop iteration variables and the independent term of each lower or upper simple bound, respectively. The n elements of vector  $\vec{1}$  are the loop iteration variables  $(\vec{1}_1, ..., \vec{1}_n)$ .

<sup>7.</sup>A transformation represented by a matrix T is non-singular if T has an inverse ( $|T| \neq 0$ ).

A transformation, represented by matrix T, maps each iteration  $\vec{1}$  of BIS into one iteration  $\vec{J}$  of the Bounded Transformed Iteration Space (BTIS):

BTIS =

$$\{\vec{J} = T \cdot \vec{I} | \vec{I} \in BIS\}$$

The Minimum Convex Space (MCS) which contains all the points of the BTIS can be put in matrix form, using the transformation matrix T and the matrix inequality which represents the bounds of the BIS:

$\left. \begin{array}{c}

A \cdot \vec{1} \leq \beta \\

T \cdot \vec{1} = \vec{J}

\end{array} \right\} \qquad \Rightarrow \qquad \begin{array}{c}

A \cdot T^{-1} \cdot \vec{J} \leq \beta \\

\hat{A} \cdot \vec{J} \leq \beta

\end{array}$

The exact bounds of the MCS can be extracted from the matrix inequality  $\hat{A} \cdot \vec{J} \leq \beta$ , using the Fourier-Motzkin algorithm [16][77].

When T is unimodular, all the integer points of the BTIS have an integer antiimage in the BIS. Therefore, the transformed loop nest must scan all the integer points of the BTIS. In this case, the bounds of the MCS can be directly used to build the loop nest required to scan the BTIS.

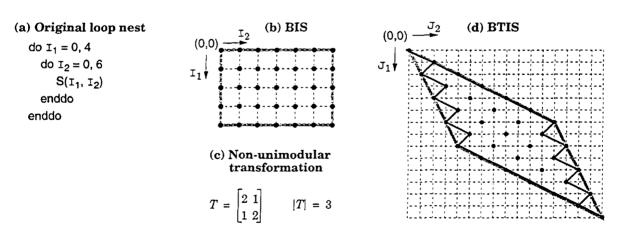

However, when T is non-unimodular (its determinant is different from  $\pm 1$ ) there are holes (integer points without integer antiimage) in the BTIS and, in particular, in the boundaries of the BTIS. In this case, to scan correctly the BTIS, all these holes must be skipped. In particular, the bounds of the MCS obtained through the FM algorithm must be corrected to obtain the precise bounds of the BTIS. As an example, consider the loop nest shown in Fig. 4.2a and its corresponding BIS (Fig. 4.2b). After applying the non-unimodular transformation T (Fig. 4.2c) to BIS, we obtain the BTIS shown in Fig. 4.2d.

The grey lines represent the bounds of the MCS and the continuous black lines that bound the shadowed area are the precise bounds of BTIS. Finally, the black dots are the points of BTIS with integer antiimage in BIS.

Figure 4.2: (a) Example loop nest. (b) Bounded Iteration Space (BIS) for this loop nest. (c) Non-unimodular transformation T. (d) BTIS obtained after applying the non-unimodular transformation T to BIS. The black dots represent the points in BTIS with integer antiimage in BIS.

Fernández et al. [45] address the problem of correcting in a systematic way the bounds of the MCS given by the FM algorithm, in order to produce the precise bounds of the BTIS. To characterize the BTIS, they use the Hermite Normal Form H of the transformation matrix T [111]. Both H and T generate the same lattice in  $\mathbb{Z}^n$ . Since H is lower triangular, it permits an easy characterization of the BTIS. The holes of the BTIS are skipped using steps greater than 1 in the loops. These steps are just the elements on the diagonal of matrix H. And the precise bounds of the BTIS are obtained by combining the bounds of the MCS obtained through the FM algorithm with some special non-linear functions [44][115] that involve the non-diagonal elements of H.

Let  $L_i^T$  and  $U_i^T$  ( $1 \le i \le n$ ) be the bounds of the MCS of the BTIS, obtained by the FM algorithm, along dimension  $J_i$  and let  $h_{ij}$  and  $h'_{ij}$  be the elements of H and  $H^1$  respectively. Then, the transformed code is:

$$\begin{split} \operatorname{do} \, \operatorname{J}_1 &= \left\lceil L_1^T/h_{11} \right\rceil \cdot h_{11}, U_1^T, h_{11} \\ gap_2 &= (h_{21} \cdot h'_{11} \cdot \operatorname{I}_1) \, \operatorname{mod} \, h_{22} \\ \operatorname{do} \, \operatorname{J}_2 &= \left\lceil \left( L_2^T - gap_2 \right) / h_{22} \right\rceil \cdot h_{22} + gap_2, U_2^T, h_{22} \\ & \cdots \\ gap_n &= \left( \sum_{r=1}^{n-1} h_{nr} \cdot \sum_{d=1}^r h'_{rd} \cdot \operatorname{I}_d \right) \operatorname{mod} \, h_{nn} \\ \operatorname{do} \, \operatorname{J}_n &= \left\lceil \left( L_n^T - gap_n \right) / h_{nn} \right\rceil \cdot h_{nn} + gap_n, U_n^T, h_{nn} \\ \operatorname{loop body} \end{split}$$

enddo

and the transformation of the loop body only requires  $I_i$  ( $1 \le i \le n$ ) (the loop iteration variables in the original loop nest) be replaced by the appropriate linear combination of  $J_i$  ( $1 \le i \le n$ ) (the loop iteration variables for the transformed loop nest); that is:

$$\begin{bmatrix} \mathbf{I}_1 \\ \dots \\ \mathbf{I}_n \end{bmatrix} = T^{-1} \cdot \begin{bmatrix} \mathbf{J}_1 \\ \dots \\ \mathbf{J}_n \end{bmatrix}$$

Figure 4.3 shows the transformed code of the example of Fig. 4.2, the Hermite Normal Form H of the transformation matrix T and its inverse  $H^{-1}$ .

#### (a) Hermite Normal form of T

$$H = \begin{bmatrix} 1 & 0 \\ 2 & 3 \end{bmatrix} \qquad H^{-1} = \frac{1}{3} \cdot \begin{bmatrix} 3 & 0 \\ -2 & 1 \end{bmatrix}$$

#### (b) Transformed loop nest

$$\begin{aligned} & \text{do } \textbf{J}_1 = \textbf{0}, \, \textbf{14} \\ & \text{gap}_2 = \ (2 \cdot \textbf{J}_1) \, \, \text{mod } \, \textbf{3} \\ & \text{do } \textbf{J}_2 = \left[ \left( \, max \! \left( \, 2 \cdot \textbf{J}_1 - \textbf{12}, \left\lceil \frac{\textbf{J}_1}{2} \right\rceil \right) - \text{gap}_2 \right) / 3 \, \right] \cdot 3 + \text{gap}_2, \, min \! \left( \, 2 \cdot \textbf{J}_1, \left\lfloor \, \frac{\textbf{18} + \textbf{J}_1}{2} \right\rfloor \right), \, \textbf{3} \\ & \text{S(} \, (2 \cdot \textbf{J}_1 - \textbf{J}_2) / 3 \, , \, \, (2 \cdot \textbf{J}_2 - \textbf{J}_1) / 3 \, ) \end{aligned}$$

enddo

**Figure 4.3:** (a) Hermite Normal Form H (and its inverse  $H^{-1}$ ) of the transformation matrix T used in Fig. 4.2. (b) Transformed loop nest.

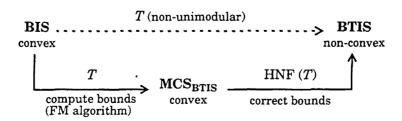

Summarizing, the result of applying a non-unimodular transformation to a convex iteration space is a non-convex space. To obtain the precise bounds of the non-convex transformed space two different steps have to be performed. First, the bounds of the MCS of the transformed space are computed using the Fourier-Motzkin algorithm and, second, these bounds are corrected using the Hermite Normal Form (HNF) of the transformation matrix [111]. Figure 4.4 shows a diagram of the steps performed when a non-unimodular transformation is applied.

In the next subsections, we will show how Simultaneous Multilevel Tiling can be performed using the theory of non-unimodular transformations and we will give an example to illustrate it. As already mentioned, Simultaneous Multilevel Tiling consists of applying first strip-mining to all loops at all levels and, afterwards, performing the loop permutation transformation only once to obtain the desired order of the loops. Let's see how both steps are carried out.

**Figure 4.4:** Steps performed when a non-unimodular transformation T is applied. HNF(T) is the Hermite Normal Form of T.

#### 4.3.2 Strip-mining all Loops at all Levels

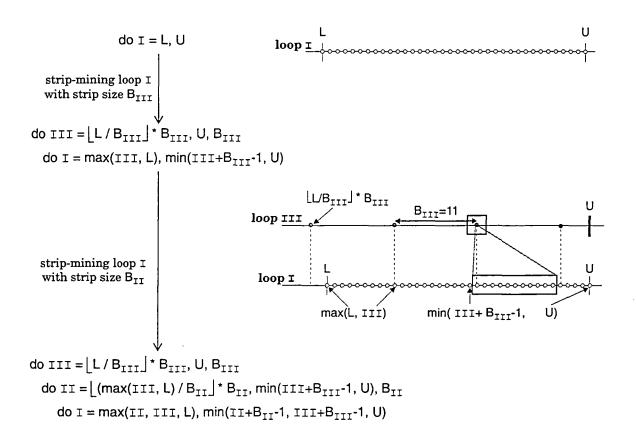

Strip-mining is a loop transformation that divides a set of consecutive points of the iteration space into strips. It decomposes a loop into two loops where the outer loop steps between the strips and the inner loop traverses the points within the strips. The strip-mining transformation [129] is defined by the formula of Figure 4.5, where II is the TI-loop that steps between the strips, I is the EL-loop that traverses the points within the strips,  $B_{II}$  is the strip size and of  $t_{II} \in Z$  ( $0 \le oft_{II} < B_{II}$ ) is an offset that determines the origin of the first strip [129]. Using this formula, the tile boundaries are always parallel to the iteration space axes.

do I = L, U

$$\xrightarrow{\text{strip-mining}}$$

do II =  $\lfloor (L - \text{oft}_{II}) / B_{II} \rfloor^* B_{II} + \text{oft}_{II}, U, B_{II}$  do I = max(II, L), min(II+B<sub>II</sub>-1, U)

Figure 4.5: Formula for strip-mining a loop.

To strip-mine one loop at several levels, strip-mining is applied repeatedly to the inner EL-loop resulting from the previous round of strip-mining, going from the outermost level to the innermost level. In Fig. 4.5 strip-mining would be applied again to loop I in the resulting code. Note that strip-mining is always applied to loops with a step equal to one. Finally, recall that the strip-mining transformation does not modify the loop body of a loop nest.

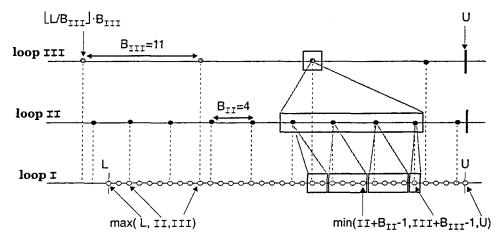

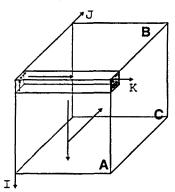

As an example, Figure 4.6 shows how strip-mining is applied twice to loop I; it shows the code of the nested loops and the points traversed by loops III, II and I after strip-mining at each level. The points on each line indicate the values of the loop index variables. The strip sizes at each level are  $B_{III}$ =11 and  $B_{II}$ =4 and, for simplicity, we assume null offsets (off<sub>III</sub>=off<sub>II</sub>=0). The shadowed rectangles indicate the values of a loop index variable for fixed values of outer loop indices. Note that for a fixed value of loop indices III and II, loop I always iterates inside the tiles determined by them, that is III  $\leq$  I  $\leq$  III+B<sub>III</sub> -1 and II  $\leq$  I  $\leq$  III+B<sub>III</sub> -1 always hold. However, for a fixed value of III, loop II can iterate over some points outside the tile determined by III. In particular, III  $\leq$  II does not hold, if B<sub>III</sub> is not multiple of B<sub>II</sub>. Notice also that loop index II can iterate over the same point for different values of III.

#### 4.3.3 Loop Permutation

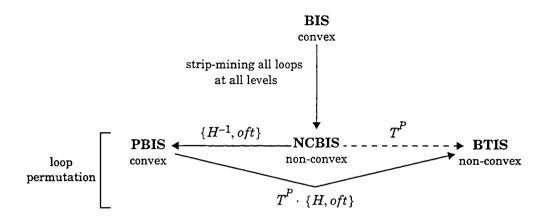

The iteration space defined by the original loop nest is a convex subset of  $\mathbb{Z}^n$ , that we call the Bounded Iteration Space (BIS). After applying strip-mining to all loops at all levels, we obtain a new loop nest that describes a non-convex iteration space. We will refer to this non-convex iteration space as NCBIS (Non-Convex Bounded Iteration Space). At this point, we want to apply to NCBIS a unimodular loop permutation transformation ( $T^P$ ) [121] to obtain the Bounded Transformed Iteration Space (BTIS). The BTIS is the desired multilevel tiled iteration space (see Fig. 4.7).

Figure 4.6: How strip-mining is applied to loop I at two levels. The strip sizes at the outermost and innermost level are  $B_{\text{III}}=11$  and  $B_{\text{II}}=4$ , respectively. We assume a null offset.

Figure 4.7: Diagram of the Simultaneous Multilevel Tiling transformation process.

There has been much work [45][85][87][105] addressing the problem of rewriting in a systematic way a loop nest according to a non-singular transformation. All these works assume that the source iteration space, to which the transformation is applied, is a convex space. In our case, however, the source iteration space (NCBIS) is non-convex and hence, the theory of non-singular transformations is not directly applicable. The NCBIS is non-convex because some of the loops (the TI-loops) have non-unit steps, and therefore, there are holes in the iteration space. In this section, we will describe a method to obtain the transformed iteration space (BTIS) when applying a unimodular loop permutation transformation to the non-convex space NCBIS.

The development of our work is based on the characterizations of the space NCBIS and of a general space obtained after applying a non-unimodular transformation to a convex space [45]. The expressions of the bounds of the loops that traverse both spaces (NCBIS and a general transformed space) are similar. This fact allows us to deduce a transformation  $\{H^{-1}, oft\}$  that transforms NCBIS to a convex space. We will refer to this convex iteration space as PBIS (Previous Bounded Iteration Space). In fact,  $H^{-1}$  is a semi-normalization transformation [129] that makes all loops in PBIS have a step equal to one and oft is an offset. Next, the multilevel tiled iteration space BTIS can be obtained by applying a non-unimodular transformation  $T = T^P \setminus \{H, oft\}$  to PBIS. This transformation performs the loop permutation and undoes the previous semi-normalization applied to NCBIS. Figure 4.7 shows a diagram of the Simultaneous Multilevel Tiling (SMT) transformation process.

In the remainder of this section we will show how the loop bounds of the loop nest that traverses BTIS can be computed in a systematic way and, at the end of this section, we will show that the loop body does not need to be rewritten. For simplicity, from now on, we will use the abbreviations NCBIS, PBIS and BTIS to refer, indistinctly, to the iteration space or to the loop nest that traverses the iteration space.

#### **Loop Bounds Computation**

We start by giving some definitions to characterize the spaces NCBIS and PBIS and we present a lemma that shows how NCBIS can be obtained from the convex space PBIS. Then, we give two corollaries showing how the bounds of the Minimum Convex Space of NCBIS can be computed. Finally, we enounce a theorem that allows us to compute the bounds of BTIS in a systematic way.

In this section, we use a slightly different notation with respect to previous sections. Unless it were necessary for readability, from now on we will not use any more the arrows above the vectors representing loop iteration variables as we have been doing so far.

#### **Definition 1**

Let H and of t be an  $m \times m$  diagonal matrix and a m-dimensional column vector, respectively:

$$H = \begin{bmatrix} \mathsf{B}_1 & \varnothing \\ & \dots \\ \varnothing & \mathsf{B}_m \end{bmatrix} \qquad oft = \begin{bmatrix} \mathsf{oft}_1 \\ \dots \\ \mathsf{oft}_m \end{bmatrix}$$

where of  $t_k \mid B_k \in \mathbb{Z}$  and  $0 \le \text{of } t_k < B_k \mid (1 \le k \le m)$ .

#### **Definition 2**

The m-deep loop nest obtained after the strip-mining phase defines the m-dimensional non-convex space NCBIS and a loop  $\mathbf{I}_k^{NCBIS}$  in NCBIS can be written, in the general case, into the following form:

$$\operatorname{do} \ \operatorname{I}_{k}^{NCBIS} = \left\lfloor \left( \ \operatorname{L}_{k}^{NCBIS} - \operatorname{oft}_{k} \right) / \operatorname{B}_{k} \right\rfloor \cdot \operatorname{B}_{k} + \operatorname{oft}_{k}, \operatorname{U}_{k}^{NCBIS}, \operatorname{B}_{k} \tag{1}$$

where

- $B_k$  is the kth diagonal element of a matrix H,

- of  $t_k$  is the kth element of a vector of t, and

- $\bullet$  L<sub>k</sub><sup>NCBIS</sup> and U<sub>k</sub><sup>NCBIS</sup> have the forms  $max(l_{k,0},l_{k,1},l_{k,2},...)$  and  $min(u_{k,0},u_{k,1},u_{k,2},...)$ , respectively, and  $l_{k,j}$ ,  $u_{k,j}$  are linear functions of the loops iteration variables, that can be expressed as follows:

$$\begin{aligned} l_{k,j} &= f_{k,j}^l \left( \mathbf{I}_1^{NCBIS}, ..., \mathbf{I}_m^{NCBIS} \right) = f_{k,j}^l (\mathbf{I}^{NCBIS}) \\ u_{k,j} &= f_{k,j}^u \left( \mathbf{I}_1^{NCBIS}, ..., \mathbf{I}_m^{NCBIS} \right) = f_{k,j}^u (\mathbf{I}^{NCBIS}) \end{aligned} \text{, where } \mathbf{I}^{NCBIS} = \begin{bmatrix} \mathbf{I}_1^{NCBIS} \\ ... \\ \mathbf{I}_m^{NCBIS} \end{bmatrix}$$

By construction, a loop  $I_k$  with step equal to one  $(B_k = 1)$  always has a null offset (off k = 0).

#### **Definition 3**

A loop  $I_k^{PBIS}$  of the m-deep loop nest that defines the convex iteration space PBIS can be written, in the general case, into the following form:

$$\operatorname{do} \operatorname{I}_{k}^{PBIS} = \left[ \left( \operatorname{L}_{k}^{PBIS} - \operatorname{oft}_{k} \right) / \operatorname{B}_{k} \right], \left[ \left( \operatorname{U}_{k}^{PBIS} - \operatorname{oft}_{k} \right) / \operatorname{B}_{k} \right] \tag{2}$$

where

- $B_k$  is the kth diagonal element of a matrix H,

- oft $_k$  is the kth element of a vector oft, and

- $\mathsf{L}_k^{PBIS}$  and  $\mathsf{U}_k^{PBIS}$  have the forms  $\max{(\tilde{l}_{k,\,0},\tilde{l}_{k,\,1},\tilde{l}_{k,\,2},\ldots)}$  and  $\min{(\tilde{u}_{k,\,0},\tilde{u}_{k,\,1},\tilde{u}_{k,\,2},\ldots)}$ , respectively, and

$$\begin{split} \tilde{l}_{k,j} &= f_{k,j}^{l} (H \cdot \mathbf{I}^{PBIS} + oft) \\ \tilde{u}_{k,j} &= f_{k,j}^{u} (H \cdot \mathbf{I}^{PBIS} + oft) \end{split}, \text{ where } \mathbf{I}^{PBIS} = \begin{bmatrix} \mathbf{I}^{PBIS}_{1} \\ \dots \\ \mathbf{I}^{PBIS}_{m} \end{bmatrix} \end{split}$$

and  $f_{k,j}^l$  and  $f_{k,j}^u$  are the same linear functions as in NCBIS.

From these definitions one important lemma follows.

#### Lemma 1

The non-convex iteration space NCBIS (1) can be obtained from the convex iteration space PBIS (2) using the following transformation:

$$I^{NCBIS} = H \cdot I^{PBIS} + oft$$

#### **Proof**

Let  $A^{PBIS} \cdot I^{PBIS} \leq \beta^{PBIS}$  be the bounds of PBIS specified in matrix form. By applying the transformation ( $I^{PBIS} = H^{-1} \cdot (I^{NCBIS} - oft)$ ), we obtain the following system of linear inequalities:

$$\boldsymbol{A}^{PBIS} \cdot \boldsymbol{H}^{-1} \cdot \boldsymbol{I}^{NCBIS} - \boldsymbol{A}^{PBIS} \cdot \boldsymbol{H}^{-1} \cdot oft \leq \boldsymbol{\beta}^{PBIS}$$

Let's now add two new inequalities to the system that can be assimilated to a new (outermost) loop that only performs one iteration and its value is always one:

$$I_0 \le 1 = \beta_0$$

$$-I_0 \le -1$$

Since  $I_0$  is equal to 1, the new extended system can be written into the following form:

$$\begin{bmatrix} 1 & & & & & \\ & -1 & & & & \\ & -A^{PBIS} \cdot H^{-1} \cdot oft & & & & A^{PBIS} \cdot H^{-1} \end{bmatrix} \cdot \begin{bmatrix} \mathbf{I}_0 \\ NCBIS \end{bmatrix} \leq \begin{bmatrix} \beta_0 \\ -\beta_0 \\ \beta^{PBIS} \end{bmatrix}$$

and this system can also be rewritten as follows:

$$\begin{bmatrix}

1 & 0 \\

-1 & 0 \\

0 & A^{PBIS}

\end{bmatrix} \cdot \begin{bmatrix}

1 & 0 \\

-H^{-1} \cdot oft & H^{-1}

\end{bmatrix} \cdot \begin{bmatrix}

I_{0} \\

I^{NCBIS}

\end{bmatrix} \leq \begin{bmatrix}

\beta_{0} \\

-\beta_{0} \\

\beta^{PBIS}

\end{bmatrix}$$

$$A_{E}^{PBIS} \xrightarrow{H_{E}^{-1}} H_{E}^{-1} \xrightarrow{I_{E}^{NCBIS}} A_{E}^{PBIS}$$

(3)

Let's refer as  $A_E^{PBIS} \cdot H_E^{-1} \cdot \mathbf{I}_E^{NCBIS} \leq \beta_E^{PBIS}$  to the extended system. The matrix transformation  $H_E$  is a non-unimodular lower triangular matrix, therefore  $\mathrm{HNF}(H_E) = H_E$ . Then, using the method proposed in [45] (see Section 4.3.1) to compute the exact bounds of NCBIS, we have that:

(a) The bounds of the MCS of NCBIS are computed by solving the system (3). The two first inequalities give us:

$$I_0 \le \beta_0$$

$$-I_0 \le -\beta_0$$

and the remainder inequalities can be written as follows:

$$\mathbf{A}^{PBIS} \cdot \begin{bmatrix} \mathbf{I}_0 \\ -H^{-1} \cdot oft & H^{-1} \end{bmatrix} \cdot \begin{bmatrix} \mathbf{I}_0 \\ \mathbf{I}^{NCBIS} \end{bmatrix} \leq \beta^{PBIS} \quad \Longrightarrow \quad$$

$$A^{PBIS} \cdot \left[ -H^{-1} \cdot oft \cdot \mathbf{I}_0 + H^{-1} \cdot \mathbf{I}^{NCBIS} \right] \le \beta^{PBIS}$$

(4)

From Definition 3 we have that the jth (lower or upper) bound of loop  $\mathfrak{I}_k^{PBIS}$  represented in the system  $A^{PBIS} \cdot \mathfrak{I}^{PBIS} \leq \beta^{PBIS}$  has the following form:

- if it is a lower bound<sup>8</sup>:  $f_{k,j}^{l}(H \cdot \mathbb{I}^{PBIS} + oft) \mathsf{B}_{k} \cdot \mathbb{I}_{k}^{PBIS} \mathsf{oft}_{k} \mathsf{B}_{k} + 1 \leq 0$

- $\bullet \text{ if it is an upper bound: } -f_{k,j}^u(H \cdot \mathbf{I}^{PBIS} + oft) + \mathbf{B}_k \cdot \mathbf{I}_k^{PBIS} + \mathsf{oft}_k \leq 0$

<sup>8.</sup> The floor function in the lower bound must be converted in a ceiling function in the following way:  $\lfloor a/b \rfloor = \lceil (a-b+1)/b \rceil$

Moreover, the proposed transformation  $\mathbf{I}^{PBIS} = H^{-1} \cdot \left(\mathbf{I}^{NCBIS} - oft\right)$  of Lemma 1 can be rewritten in the extended space as follows, because  $\mathbf{I}_0 = \beta_0 = 1$ :

$$\mathbf{I}^{PBIS} = H^{-1} \cdot \left( \mathbf{I}^{NCBIS} - oft \cdot \mathbf{I}_{0} \right), \text{ that is, } \mathbf{I}_{k}^{PBIS} = \frac{1}{\mathsf{B}_{k}} \cdot \left( \mathbf{I}_{k}^{NCBIS} - oft_{k} \cdot \mathbf{I}_{0} \right) \qquad (1 \le k \le m)$$

Then, it can be deduced after some algebraic manipulations, that the jth (lower or upper) bound along dimension  $\mathbb{I}_{k}^{NCBIS}$  ( $(1 \le k \le m)$ ) of the system (4) has the following form:

- if it is a lower bound:  $\mathbf{I}_{k}^{NCBIS} \ge f_{k,j}^{l} (\mathbf{I}^{NCBIS}) \mathbf{B}_{k} + 1 = l_{k,j} \mathbf{B}_{k} + 1$

- if it is an upper bound:  $I_k^{NCBIS} \le f_{k,j}^u (I^{NCBIS}) = u_{k,j}$

Therefore, the solution to the system (3) is:

$$\begin{split} \mathsf{L}_0^{MCS} &= \mathsf{U}_0^{MCS} = 1 \\ \mathsf{L}_k^{MCS} &= \mathsf{L}_k^{NCBIS} - \mathsf{B}_k + 1 \\ \mathsf{U}_k^{MCS} &= \mathsf{U}_k^{NCBIS} \end{split}$$

where  $\mathsf{L}_k^{MCS}$  and  $\mathsf{U}_k^{MCS}$  ( $0 \le k \le m$ ) are the lower and upper bounds of the MCS of NCBIS along dimension  $\mathsf{I}_k^{NCBIS}$ , respectively.

(b) The HNF of the extended matrix  $H_E$  is used to correct the bounds of the MCS of NCBIS, where:

$$HNF(H_E) = H_E = \begin{bmatrix} 1 & 0 \\ -H^{-1} \cdot oft & H^{-1} \end{bmatrix}^{-1} = \begin{bmatrix} 1 & 0 \\ oft & H \end{bmatrix}$$

Then, the exact loop bounds in NCBIS are:

do  $I_0 = 1, 1$

$$\operatorname{do} \ \operatorname{I}_{k}^{NCBIS} = \left\lceil \frac{\operatorname{L}_{k}^{NCBIS} - \operatorname{B}_{k} + 1 - ((\operatorname{oft}_{k} \cdot \operatorname{I}_{0}) \ \operatorname{mod} \ \operatorname{B}_{k})}{\operatorname{B}_{k}} \right\rceil \cdot \operatorname{B}_{k} + ((\operatorname{oft}_{k} \cdot \operatorname{I}_{0}) \ \operatorname{mod} \ \operatorname{B}_{k}), \operatorname{U}_{k}^{NCBIS}, \operatorname{B}_{k} + ((\operatorname{oft}_{k} \cdot \operatorname{I}_{0}) \ \operatorname{mod} \ \operatorname{B}_{k}), \operatorname{U}_{k}^{NCBIS}, \operatorname{B}_{k} + ((\operatorname{oft}_{k} \cdot \operatorname{I}_{0}) \ \operatorname{mod} \ \operatorname{B}_{k}), \operatorname{U}_{k}^{NCBIS}, \operatorname{B}_{k} + ((\operatorname{oft}_{k} \cdot \operatorname{I}_{0}) \ \operatorname{mod} \ \operatorname{B}_{k}), \operatorname{U}_{k}^{NCBIS}, \operatorname{B}_{k} + ((\operatorname{oft}_{k} \cdot \operatorname{I}_{0}) \ \operatorname{mod} \ \operatorname{B}_{k}), \operatorname{U}_{k}^{NCBIS}, \operatorname{B}_{k} + ((\operatorname{oft}_{k} \cdot \operatorname{I}_{0}) \ \operatorname{mod} \ \operatorname{B}_{k}), \operatorname{U}_{k}^{NCBIS}, \operatorname{B}_{k} + ((\operatorname{oft}_{k} \cdot \operatorname{I}_{0}) \ \operatorname{mod} \ \operatorname{B}_{k}), \operatorname{U}_{k}^{NCBIS}, \operatorname{B}_{k} + ((\operatorname{oft}_{k} \cdot \operatorname{I}_{0}) \ \operatorname{mod} \ \operatorname{B}_{k}), \operatorname{U}_{k}^{NCBIS}, \operatorname{B}_{k} + ((\operatorname{oft}_{k} \cdot \operatorname{I}_{0}) \ \operatorname{Impart}_{k} \cdot \operatorname{Impart}_{k}), \operatorname{U}_{k}^{NCBIS}, \operatorname{B}_{k} + ((\operatorname{oft}_{k} \cdot \operatorname{Impart}_{k}) \ \operatorname{Impart}_{k} \cdot \operatorname{Impart}_{k}), \operatorname{Impart}_{k} \cdot \operatorname{Impart}$$

Now, loop  $\mathbf{I}_0$  can be eliminated and the loop nest can be rewritten into the following form:

$$\operatorname{do} \operatorname{I}_{k}^{NCBIS} = \left| \frac{\mathsf{L}_{k}^{NCBIS} - \operatorname{oft}_{k}}{\mathsf{B}_{k}} \right| \cdot \mathsf{B}_{k} + \operatorname{oft}_{k}, \mathsf{U}_{k}^{NCBIS}, \mathsf{B}_{k} \qquad (1 \le k \le m)$$

bearing in mind that  $I_0 = 1$ , of  $I_k < B_k$  (therefore,  $(\text{oft}_k \cdot I_0) \mod B_k = \text{oft}_k$ ) and  $\left\lceil \frac{a-b+1}{b} \right\rceil = \left\lfloor \frac{a}{b} \right\rfloor$ .

This is the general form of a loop in NCBIS (Definition 2). ■

Let's now see the two corollaries that show how the bounds of the MCS of NCBIS can be computed.

#### Corollary 1

The bounds of the Minimum Convex Space (MCS) of the m-dimensional non-convex space NCBIS can be obtained from the following system of inequalities:

$$A^{NCBIS} \cdot \tau^{NCBIS} < \beta^{NCBIS}$$

where

$$A^{NCBIS} = A^{PBIS} \cdot H^{-1}$$

and  $\beta^{NCBIS} = \beta^{PBIS} + A^{PBIS} \cdot H^{-1} \cdot oft$ .

#### Proof

From Lemma 1 we know that the following system represents the MCS of NCBIS:

$$A^{PBIS} \cdot \left[ -H^{-1} \cdot oft \cdot \mathbf{I}_0 + H^{-1} \cdot \mathbf{I}^{NCBIS} \right] \leq \beta^{PBIS}$$

Substituting  $I_0 = 1$  and rewriting the expression we obtain:

$$A^{PBIS} \cdot H^{-1} \cdot \mathbf{I}^{NCBIS} \leq \beta^{PBIS} + A^{PBIS} \cdot H^{-1} \cdot oft \quad \Rightarrow \quad A^{NCBIS} \cdot \mathbf{I}^{NCBIS} \leq \beta^{NCBIS} \quad \blacksquare$$

#### Corollary 2

The lower and upper bounds of the MCS of NCBIS along dimension  $\mathbb{I}_k^{NCBIS}$  ( $\mathbb{L}_k^{MCS}$  and  $\mathbb{U}_k^{MCS}$ , respectively) can be directly obtained from the loop bounds of NCBIS (Definition 2) as follows:

$$\begin{array}{l} \mathsf{L}_k^{MCS} = \mathsf{L}_k^{NCBIS} - \mathsf{B}_k + 1 \\ \\ \mathsf{U}_k^{MCS} = \mathsf{U}_k^{NCBIS} \end{array} \tag{$1 \leq k \leq m$)}$$

#### **Proof**

See proof of Lemma 1.

Until now, we have proven that NCBIS can be obtained from the convex iteration space PBIS by applying a particular transformation and we have shown how the bounds of the MCS of NCBIS can be directly obtained from the loop bounds of NCBIS. Now we enounce a theorem that allows us to compute the bounds of BTIS in a systematic way.

#### Theorem 1

Let BTIS be the transformed iteration space obtained after applying a unimodular loop permutation transformation  $T^P$  to the m-dimensional space NCBIS. The m-deep loop nest that traverses BTIS has the following form:

$$\operatorname{do} \mathbf{I}_{k}^{BTIS} = \left\lceil \left( \mathbf{L}_{k}^{BTIS} - \operatorname{oft}_{k}^{P} \right) / \mathbf{B}_{k}^{P} \right\rceil \cdot \mathbf{B}_{k}^{P} + \operatorname{oft}_{k}^{P}, \mathbf{U}_{k}^{BTIS}, \mathbf{B}_{k}^{P} \tag{5}$$

where

•  $\mathsf{L}_k^{BTIS}$  and  $\mathsf{U}_k^{BTIS}$   $(1 \le k \le m)$  are obtained by solving the following system using the Fourier-Motzkin algorithm:

$$A^{NCBIS} \cdot \left(T^{P}\right)^{-1} \cdot \mathbf{I}^{BTIS} \leq \beta^{NCBIS} \text{ , where } \mathbf{I}^{BTIS} = \begin{bmatrix} \mathbf{I}_{1}^{BTIS} \\ \dots \\ \mathbf{I}_{m}^{BTIS} \end{bmatrix}$$

- of  $t_k^P$  is the kth elements of a vector  $of t_k^P = T^P \cdot of t$ ,

- and  $B_k^P$  is the kth diagonal element of a matrix  $H^P = T^P \cdot H \cdot (T^P)^{-1}$ .

#### Proof

From Lemma 1 we have that NCBIS can be obtained from the convex iteration space PBIS  $A^{PBIS} \cdot \mathbf{I}^{PBIS} \leq \beta^{PBIS}$  using the transformation  $\mathbf{I}^{NCBIS} = H \cdot \mathbf{I}^{PBIS} + oft$ .

Let's now extend PBIS in one dimension  $(I_0)$  that represents a new (outermost) loop that only performs one iteration and its value is always one  $(\beta_0 = 1)$ . The new extended system can be written in matrix form into the following manner:

$$\begin{bmatrix} 1 & & & & \\ -1 & & & \\ \hline 0 & A^{PBIS} & \end{bmatrix} \cdot \begin{bmatrix} \mathbf{I}_{0} \\ P^{BIS} \end{bmatrix} \leq \begin{bmatrix} \beta_{0} \\ -\beta_{0} \\ \beta^{PBIS} \end{bmatrix}$$

$$\longleftrightarrow A_{E}^{PBIS} \longleftrightarrow \mathbf{I}_{E}^{PBIS} \longleftrightarrow \beta_{E}^{PBIS}$$

As shown in proof of Lemma 1, the transformation matrix that transforms the extended PBIS into the extended NCBIS is:

$$H_E = \begin{bmatrix} 1 & 0 \\ oft & H \end{bmatrix}$$

Then, the matrix transformation that transforms the extended PBIS into an extended BTIS is  $\mathbb{I}_E^{BTIS} = T_E^P \cdot H_E \cdot \mathbb{I}_E^{PBIS}$ , where:

$$T_E^P \cdot H_E = \begin{bmatrix} 1 & 0 \\ 0 & T^P \end{bmatrix} \cdot \begin{bmatrix} 1 & 0 \\ oft & H \end{bmatrix} \text{ , and } \mathbf{I}_E^{BTIS} = \begin{bmatrix} \mathbf{I}_0 \\ \mathbf{I}^{BTIS} \end{bmatrix}$$

By applying this transformation to the extended PBIS the following system is obtained:

$$A_E^{PBIS} \cdot H_E^{-1} \cdot \left(T_E^P\right)^{-1} \cdot \mathbf{I}_E^{BTIS} \le \beta_E^{PBIS} \tag{6}$$

To compute the exact bounds of the extended BTIS, we use the method proposed in [45]: first the bounds of the MCS are computed and, second, the bounds are corrected using the Hermite Normal Form of  $T_E^P \cdot H_E$ .

(a) The bounds of the MCS of the extended BTIS are computed by solving system (6). The two first inequalities give us:

$I_0 \le \beta_0$   $-I_0 \le -\beta_0$

and the remainder inequalities can be written as follows:

$$A^{PBIS} \cdot \begin{bmatrix} -H^{-1} \cdot oft & (T^P \cdot H)^{-1} \end{bmatrix} \cdot \begin{bmatrix} \mathbb{I}_0 \\ \mathbb{I}^{BTIS} \end{bmatrix} \leq \beta^{PBIS} \implies$$

$$A^{PBIS} \cdot \left[ -H^{-1} \cdot oft \cdot \mathbb{I}_0 + (T^P \cdot H)^{-1} \cdot \mathbb{I}^{NCBIS} \right] \le \beta^{PBIS}$$

(7)

To rewrite this expression in terms of NCBIS, we use Corollary 1. From Corollary 1 we have that  $A^{PBIS} = A^{NCBIS} \cdot H$  and  $\beta^{PBIS} = \beta^{NCBIS} - A^{PBIS} \cdot H^{-1} \cdot oft$ , therefore, substituting in (7) we have that the bounds of the MCS of BTIS are obtained from the following system using the Fourier-Motzkin algorithm:

$$A^{NCBIS} \cdot H \cdot (T^P \cdot H)^{-1} \le \beta^{NCBIS} \implies A^{NCBIS} \cdot (T^P)^{-1} \le \beta^{NCBIS}$$

(b) The HNF of  $T_E^P \cdot H_E$  is used to correct the bounds of the MCS of the BTIS. Since  $H_E$  is a lower triangular matrix,  $HNF\Big(T_E^P \cdot H_E\Big) = T_E^P \cdot H_E \cdot \Big(T_E^P\Big)^{-1}$ , that is:

$$HNF\left(T_{E}^{P}\cdot H_{E}\right) = \begin{bmatrix} 1 & 0 \\ 0 & T^{P} \end{bmatrix} \cdot \begin{bmatrix} 1 & 0 \\ oft & H \end{bmatrix} \cdot \begin{bmatrix} 1 & 0 \\ 0 & \left(T^{P}\right)^{-1} \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ T^{P}\cdot oft & T^{P}\cdot H\cdot \left(T^{P}\right)^{-1} \end{bmatrix}, \text{ then } T^{P}\cdot H\cdot \left(T^{P}\right)^{-1} = \begin{bmatrix} 1 & 0 \\ T^{P}\cdot oft & T^{P}\cdot H\cdot \left(T^{P}\right)^{-1} \end{bmatrix}$$

$$\mathit{HNF}\Big(T_E^P \cdot H_E\Big) = \begin{bmatrix} 1 & 0 \\ \mathit{oft}^P & H^P \end{bmatrix}, \text{ where } \mathit{oft}^P = \mathit{T}^P \cdot \mathit{oft} \text{ and } \mathit{H}^P = \mathit{T}^P \cdot \mathit{H} \cdot \Big(\mathit{T}^P\Big)^{-1}.$$

Then, the exact loop bounds in BTIS are:

where  $\mathsf{L}_k^{BTIS}$  and  $\mathsf{U}_k^{BTIS}$   $(1 \le k \le m)$  are the bounds of the MCS of BTIS along dimension  $\mathsf{I}_k^{BTIS}$ ,  $\mathsf{oft}_k^P$  is the kth element of vector  $\mathsf{oft}^P$  and  $\mathsf{B}_k^P$  is the kth diagonal element of  $H^P$ .

Now, loop Io can be eliminated and the loop nest can be rewritten into the following form,

$$\operatorname{do} \operatorname{I}_{k}^{BTIS} = \left[ \frac{\operatorname{L}_{k}^{BTIS} - \operatorname{oft}_{k}^{P}}{\operatorname{B}_{k}^{P}} \right] \cdot \operatorname{B}_{k}^{P} + \operatorname{oft}_{k}^{P}, \operatorname{U}_{k}^{BTIS}, \operatorname{B}_{k}^{P} \qquad (1 \leq k \leq m)$$

bearing in mind that  $I_0 = 1$  and  $\operatorname{oft}_k^P < \operatorname{B}_k^P$  (therefore,  $\left(\operatorname{oft}_k^P \cdot I_0\right) \operatorname{mod} \operatorname{B}_k^P = \operatorname{oft}_k^P$ ).

#### Rewriting the Loop Body

The loop body of the original iteration space (BIS) does not need to be rewritten after the Simultaneous Multilevel Tiling transformation because (1) the strip-mining phase does not modify the loop body and (2) although the loop permutation phase does, we use in the transformed code (BTIS) the same names for the loop iteration variables as in the strip-mined code (NCBIS), thus avoiding a rewrite of the loop body.

Let  $\mathbf{I}^{NCBIS}$  and  $\mathbf{I}^{BTIS}$  be the loop iteration variables of NCBIS and BTIS, respectively. The transformation of the loop body after applying the loop permutation transformation  $T^P$  to NCBIS, only requires  $\mathbf{I}_k^{NCBIS}$   $(1 \le k \le m)$  be replaced by the appropriate linear combination of  $\mathbf{I}_k^{BTIS}$   $(1 \le k \le m)$ ; that is:

$$\begin{bmatrix} \mathbf{I}_{1}^{NCBIS} \\ \dots \\ \mathbf{I}_{m}^{NCBIS} \end{bmatrix} = \left(T^{P}\right)^{-1} \cdot \begin{bmatrix} \mathbf{I}_{1}^{BTIS} \\ \dots \\ \mathbf{I}_{m}^{BTIS} \end{bmatrix}$$

Since  $T^P$  is the identity matrix with rows permuted, each row of  $T^P$  has one unit element and zeros elsewhere. Thus, we can name the loop iteration variables in BTIS as in NCBIS according to the permutation, that is  $\mathbf{I}^{BTIS} = T^P \cdot \mathbf{I}^{NCBIS}$ . This way, the loop body does not need to be modified.

#### 4.3.4 SMT Summary

Summarizing the previous sections, in order to transform a n-deep loop nest (BIS) into a m-deep multilevel tiled code (BTIS), the following steps have to be performed:

**Step 1:** Apply strip-mining to all desired loops in BIS at all desired levels, obtaining a *m*-deep loop nest (NCBIS).

Step 2: Compute matrix H, vector oft and the bounds of the MCS of NCBIS directly from the bounds of NCBIS. Recall from Corollary 2 that  $\mathsf{L}_k^{MCS}$  and  $\mathsf{U}_k^{MCS}$   $(1 \le k \le m)$  (the lower and upper bounds of the MCS along dimension  $\mathsf{I}_k^{NCBIS}$ , respectively) can be directly obtained from the bounds of NCBIS as follows:

$$\begin{split} \mathsf{L}_{k}^{MCS} &= \mathsf{L}_{k}^{NCBIS} - \mathsf{B}_{k} + 1 \\ \mathsf{U}_{k}^{MCS} &= \mathsf{U}_{k}^{NCBIS} \end{split}$$

The MCS of NCBIS can be written in matrix form as  $A^{NCBIS} \cdot I^{NCBIS} \le \beta^{NCBIS}$ .

Step 3: Compute the bounds of the MCS of the BTIS. They are extracted from the matrix inequality  $A^{NCBIS} \cdot \left(T^P\right)^{-1} \cdot \mathbf{I}^{BTIS} \leq \beta^{NCBIS}$ , using the Fourier-Motzkin algorithm (Theorem 1).  $T^P$  is the unimodular loop permutation transformation.

**Step 4:** Correct the bounds of the MCS of the BTIS using the vector  $oft^P$  ( $oft^P = T^P \cdot oft$ ) and the matrix  $H^P$  ( $H^P = T^P \cdot H \cdot (T^P)^{-1}$ ). At this point we have obtained the exact bounds of the BTIS.

#### 4.3.5 SMT Example

To exemplify the transformation process we will use the code shown in Fig. 4.8a and we assume that tiling has to be performed at two levels. Suppose that, at the innermost level, dimensions I and J have to be tiled and, at the outermost level, only dimension I has to be tiled. After strip-mining all loops at all levels, using all offsets equal to 1, we obtain the code shown in Fig. 4.8b (the NCBIS). The length of the loop index identifiers (III-II-I) refers to the level of the tiles that they are traversing. Suppose that the desired loop order in the transformed code is III-JJ-II-J-I, from outermost to innermost.

Figures 4.8c to 4.8h show the loop permutation process. First, we compute matrix H, vector oft (Fig. 4.8c) and the bounds of the MCS of NCBIS (Fig. 4.8d) directly from the bounds of the NCBIS (Fig. 4.8b). Second, we compute the bounds of the MCS of BTIS (Fig. 4.8f), using the FM algorithm. These bounds are extracted from the matrix inequality  $A^{NCBIS} \cdot \left(T^P\right)^{-1} \cdot \mathbf{I}^{BTIS} \leq \beta^{NCBIS}$ , where  $A^{NCBIS} \cdot \mathbf{I}^{NCBIS} \leq \beta^{NCBIS}$  are the bounds of the MCS of NCBIS (Fig. 4.8d) and  $T^P$  is the unimodular loop permutation transformation (Fig. 4.8e). Finally, we correct the bounds of the MCS of BTIS (Fig. 4.8h) as explained in Section 4.3.1 (page 132), using  $H^P$  and  $O(t^P)$  (Fig. 4.8g).

#### Step 1: Strip-mining phase

# (a) BIS do I = 1, N do J = I, N loop body enddo strip-mining phase

#### (b) NCBIS

do III =1, N,

$$B_{III}$$

do II =  $\lfloor \max(III-1, 0)/B_{II} \rfloor^* B_{II}+1$ ,  $\min(III+B_{III}-1, N)$ ,  $B_{II}$

do I =  $\max(II, III, 1)$ ,  $\min(II+B_{II}-1, III+B_{III}-1, N)$

do  $JJ = \lfloor I-1/B_{JJ} \rfloor^* B_{JJ}+1$ , N,  $B_{JJ}$

do  $J = \max(I, JJ)$ ,  $\min(N, JJ+B_{JJ}-1)$

loop body

enddo

Step 2: Compute H, oft and MCS of NCBIS

(c) Matrix H and vector oft

$$H = \begin{bmatrix} \mathsf{B}_{\mathtt{III}} & & & & \\ & \mathsf{B}_{\mathtt{II}} & & & \\ & & 1 & & \\ 0 & & & \mathsf{B}_{\mathtt{JJ}} & & & \\ \end{bmatrix} \quad oft = \begin{bmatrix} 1 \\ 1 \\ 0 \\ 1 \\ 0 \end{bmatrix}$$

#### (d) MCS of NCBIS

$$\begin{aligned} 2\text{-}B_{\text{III}} &\leq \text{III} \leq \text{N} \\ \text{max}(\text{III-}B_{\text{II}}\text{+}1, 2\text{-}B_{\text{II}}) \leq \text{II} \leq \text{min}(\text{III+}B_{\text{III}}\text{-}1, \text{N}) \\ \text{max}(\text{II}, \text{III}, 1) &\leq \text{I} \leq \text{min}(\text{II+}B_{\text{II}}\text{-}1, \text{III+}B_{\text{III}}\text{-}1, \text{N}) \\ &\qquad \qquad \text{I-}B_{\text{JJ}}\text{+}1 \leq \text{JJ} \leq \text{N} \\ \text{max}(\text{I}, \text{JJ}) &\leq \text{J} \leq \text{min}(\text{N}, \text{JJ+}B_{\text{JJ}}\text{-}1) \end{aligned}$$

Step 3: Compute MCS of BTIS using  $T^P$

(e) Matrix TP

$$T^{P} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 & 0 \end{bmatrix}$$

#### (f) MCS of BTIS

$$(2 - B_{III}) \leq III \leq N$$

$$\max(III, 1) - B_{JJ} + 1 \leq JJ \leq N$$

$$\max(III, 1) - B_{II} + 1 \leq II \leq \min(III + B_{III} - 1, JJ + B_{JJ} - 1, N)$$

$$\max(III, II, JJ, 1) \leq J \leq \min(JJ + B_{JJ} - 1, N)$$

$$\max(III, II, 1) \leq I \leq \min(III + B_{III} - 1, II + B_{II} - 1, JJ + B_{JJ} - 1, J, N)$$

#### Step 4: Correct the bounds using oft<sup>P</sup> and matrix $H^P$

#### (h) Exact bounds of BTIS

(g) Matrix  $H^P$  and vector  $oft^P$

$$H^{P} = \begin{bmatrix} B_{III} & & & & & \\ & B_{JJ} & & & & \\ & & B_{II} & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & &$$

do III = 1, N,

$$B_{III}$$

do JJ =  $\lfloor (max(III-1, 0)/B_{JJ})^*B_{JJ}+1$ , N,  $B_{JJ}$

do II =  $\lfloor max(III-1,0)/B_{II} \rfloor^*B_{II}+1$ ,

$min(III+B_{III}-1,JJ+B_{JJ}-1,N)$ ,  $B_{II}$

do J =  $max(III, II, JJ, 1)$ ,  $min(JJ+B_{JJ}-1, N)$

do I =  $max(III, II, 1)$ ,

$min(III+B_{III}-1, II+B_{II}-1, JJ+B_{JJ}-1, J, N)$

loop body

Figure 4.8: (a) Example of loop nest (BIS). (b) Loop nest after applying strip-mining to loop I at two levels and to J at one level (NCBIS). (c) Matrix H and vector oft, obtained from NCBIS. (d) Minimum Convex Space of NCBIS, directly obtained from (b). (e) Loop permutation matrix  $T^P$  used in the example. (f) Minimum Convex Space of BTIS, obtained using the FM algorithm. (g) Matrix  $H^P$  and vector oft used to correct the bounds of the MCS of BTIS. (h) Exact loop bounds in the BTIS.

#### 4.4 EFFICIENT IMPLEMENTATION OF SMT

In the previous section we have shown how multilevel tiling can be implemented to deal with all levels simultaneously. Of all the steps required to implement our multilevel tiling technique, the most expensive one is the loop permutation transformation (step 3) or, more precisely, the step that computes the bounds of the MCS of the BTIS using the Fourier-Motzkin algorithm. Recall from Section 4.2.2 that the complexity of the FM algorithm depends doubly exponentially on the number of loops involved in the permutation.

In this section we propose an efficient implementation of SMT that allows us to demonstrate (later in Section 4.5) that the whole SMT process has a much lower complexity than traditional techniques. The idea behind our SMT implementation consists in reducing the number of simple bounds<sup>9</sup> examined in each iteration of the FM algorithm by representing with a single loop a set of loops that are related by the strip-mining transformation. Moreover, besides having a much lower complexity, our implementation also generates fewer redundant bounds. We will show this fact later in Section 4.6.

The remainder of this section is organized as follows: First, we present a theorem that holds in the SMT context and allows us to establish the complexity of the SMT implementation. Second, we show how the number of simple bounds examined in each iteration of the FM can be reduced. Third, we summarize the steps of the efficient implementation of SMT and give some implementation details and, finally, we present the SMT algorithm and illustrate how it works with an example.

#### 4.4.1 Computing the Bounds of TI-loops

As stated in Section 4.2.2, the Fourier-Motzkin algorithm computes the exact loop bounds in the transformed space from innermost to outermost. Each iteration of FM performs two steps. In the second step, each of the lower simple bounds of the loop being solved is compared with each of the upper simple bounds. These comparisons generate inequalities that might become new simple bounds of the yet-to-be-processed loops and, in the worst case, the number of new simple bounds added grows quadratically in each iteration [129].

In a multilevel tiled code, the inner loops are always the loops that traverse the points within the tiles (the EL-loops) and the outer loops are the loops that step between tiles (the TI-loops). Thus, in our SMT algorithm, the bounds of the EL-loops are always computed before the bounds of the TI-loops. The following theorem holds when computing the loop bounds in the transformed space.

<sup>9.</sup> Recall that the loop bounds are max or min compositions of affine functions of the surrounding loop iteration variables and that we refer to each affine function as a *simple bound*.

#### Theorem 2

In SMT, the second step of the FM algorithm does not need to be performed when the loop being solved is a TI-loop.

#### Proof

In Appendix D, we demonstrate that, when computing the bounds of a TI-loop, all new simple bounds generated by the second step of the FM algorithm are redundant. Therefore, the second step of the FM algorithm does not need to be performed when the loop being solved is a TI-loop. ■

This theorem is very important because it allows us to demonstrate that the number of simple bounds does not increase quadratically when computing the bounds of TI-loops.

#### 4.4.2 Examining fewer Simple Bounds

To compute the bounds of a certain loop, the FM algorithm examines, besides its own simple bounds, the simple bounds of the loops that are between its original position (before moving) and its final position (after moving). We note that it is not necessary to examine the bounds of other outer loops because they cannot have simple bounds that are affine functions of the loop being solved. In the example of Fig. 4.8, to compute the bounds of the innermost loop (loop I) in Fig. 4.8f, the FM algorithm examines the simple bounds of loops I, JJ and J in Fig. 4.8d. Note that the examined loops can be either *contiguous* TI-loops associated to the same EL-loop or *contiguous* TI -loops followed by their associated EL-loop.

In our implementation of SMT, we represent with a single loop (called C-loop; *Cluster loop*) all the contiguous TI-loops associated to the same EL-loop that must be examined by the FM algorithm. A C-loop traverses the same iteration space as the loops it is representing but uses a fewer number of simple bounds. Then, the idea of our implementation consists in stripping<sup>10</sup> the TI and EL-loops of the final code from their associated C-loops as late as possible, that is, just before their bounds have to be computed. Initially, all the loops in the original code are C-loops.

For example, assume that after strip-mining all loops of a loop nest I-J-K at all desired levels, we obtain the loop nest III-I-JJ-J-KKK-KK-K. The length of the loop index identifiers (KKK-KK-K) refers to the level of the tiles that they are traversing. Suppose that we want loop I to be in the innermost position in the final code. When computing its new bounds, the FM algorithm needs to examine all simple bounds of loops I, JJ, J, KKK, KK and K. By contrast, in the efficient implementation, we start with the loops in the original code I-J-K. These three loops are C-loops because they represent contiguous associated TI and EL-loops of the final code. Just before computing the bounds of EL-loop I

<sup>10.</sup>In this context, "to strip" means extracting the innermost TI (or EL)-loop from a C-loop.

in the final code, it is stripped from its associated C-loop, obtaining the loops II-I-J-K (loop II is now the new C-loop). Now, to compute the bounds of EL-loop I, the FM algorithm only examines the bounds of the loops I, J and K.

To implement this "stripping" process, the efficient SMT algorithm has to be able to strip from a C-loop the EL-loop and its associated TI-loops, one by one, from the innermost to the outermost level. Note that this order is just the reverse order of what strip-mining does. Thus, we need a backward transformation of strip-mining, that we will refer to as *strip-clustering*.

#### Strip-clustering

We define *strip-clustering* as a loop transformation that clusters a set of strips together. It decomposes a C-loop into two loops where the outer loop steps between clusters of inner strips and the inner loop steps between the initial points of the inner strips. The outer loop is a new C-loop and the inner loop is the TI or EL-loop being stripped. In strip-clustering, the boundaries of the tiles are parallel to the iteration space axes as in the strip-mining transformation.

The strip-clustering transformation applied to a C-loop with a step equal to one is defined by the expressions shown in Fig. 4.9, where II is the new C-loop, I is the EL-loop being stripped,  $B_{II}$  is the strip size of the new C-loop and  $Oft_{II} \in Z$  ( $0 \le Oft_{II} < B_{II}$ ) is an offset that determines the origin of the first strip. Note that these expressions are exactly the same expressions as used in strip-mining.

do I = L, U

$$\xrightarrow{\text{strip-clustering}}$$

do II =  $\lfloor (L - \text{oft}_{II}) / B_{II} \rfloor^* B_{II} + \text{oft}_{II}, U, B_{II}$  do I = max(II, L), min(II+B<sub>II</sub>-1, U)

Figure 4.9: Formula for strip-clustering a C-loop with a step equal to one.

The strip-clustering transformation applied to a C-loop with a step different from one is defined by the expressions in Fig. 4.10, where III is the new C-loop, II is the TI-loop being stripped,  $B_{III}$  is the strip size of the new C-loop,  $B_{II}$  is the strip size of the TI-loop ( $B_{III} >> B_{II}$ ) and oft<sub>II</sub>, oft<sub>III</sub>  $\in Z$  ( $0 \le$  oft<sub>III</sub>  $< B_{III}$ ) are the offsets of each strip.

$$do \ II = \left\lfloor \left( L - oft_{II} \right) / B_{II} \right\rfloor^* B_{II} + oft_{II}, \ U, \ B_{II}$$

$$do \ I = max(II, L), \ min(II + B_{II} - 1, U)$$

$$Strip-clustering \ loop \ II$$

$$do \ III = \left\lfloor \left( L - oft_{III} \right) / B_{III} \right\rfloor^* B_{III} + oft_{III}, \ U, \ B_{III}$$

$$do \ II = \left\lfloor \left( max(III, L) - oft_{II} \right) / B_{II} \right\rfloor^* B_{II} + oft_{II}, \ min(U, \ III + B_{III} - 1), \ B_{II}$$

$$do \ II = max(III, II, L), \ min(III + B_{III} - 1, \ II + B_{II} - 1, U)$$

Figure 4.10: Formula for strip-clustering a C-loop with a step different from one.

Two different phases can be distinguished when strip-clustering is applied to a C-loop with a step different from one:

- Creating phase: This phase consists in creating the new C-loop and the TI-loop being stripped. The bounds of the C and TI-loops are computed directly using the expressions of Fig. 4.10.

- Broadcasting phase: This phase consists in modifying the simple bounds of all earlier stripped TI and EL-loops (generated by strip-clusterings applied previously). In the general case, the TI-loop II being stripped (see Fig. 4.10) can iterate over some points outside the tiles determined by the new C-loop III (that is, III  $\leq$  II and II+B<sub>II</sub> -1  $\leq$  III+B<sub>III</sub>-1 does not hold in the general case). Therefore, two new simple bounds (the lower simple bound III and the upper simple bound III+B<sub>III</sub>-1) have to be added to the bounds of all previous stripped TI and EL-loops (loop I in Fig. 4.10). Note that adding these simple bounds is equivalent to substituting iteration variable II by max(III, II) in the lower bound and by min(II+B<sub>II</sub>-1, III+B<sub>III</sub>-1)-B<sub>II</sub>+1 in the upper bound of all previous stripped TI and EL-loops.

Note also that when strip-clustering is applied to a C-loop with a step equal to one (Fig. 4.9) only the *creating phase* is performed since there are no inner TI or EL-loops previously stripped.

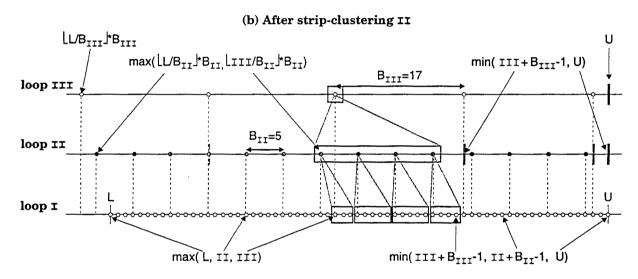

Figure 4.11 shows graphically how the bounds of previously stripped TI and EL-loops have to be modified in the *broadcasting phase*. Figure 4.11a shows how the iteration space is traversed before applying the strip-clustering transformation to a C-loop II with a step different from one and Fig. 4.11b shows the iteration space after applying the transformation. The points on each line indicate the values of the loop index variable and the shadowed rectangles indicate the values of a loop index variable for fixed values of outer loop indices. The strip sizes at each level are B<sub>III</sub>=17 and B<sub>II</sub>=5 and, for simplicity, we assume null offsets (oft<sub>III</sub>=oft<sub>II</sub>=0).

#### Computing the Minimum Convex Space after Strip-Clustering

Finally, we want to clarify that the FM algorithm is executed using the bounds of the MCS of the NCBIS that are directly obtained from the NCBIS. Then, the new bounds obtained after the execution of FM are the bounds of the MCS of the BTIS, that must be corrected using the vector  $oft^P$  and the matrix  $H^P$  to obtain the exact bounds of the BTIS.

Recall from Definition 2 (Section 4.3.3) that a loop  $\mathbf{I}_k^{NCBIS}$  in NCBIS can be written, in the general case, into the following form:

$$\text{do } \mathbf{I}_{k}^{NCBIS} = \left\lfloor \left( \left. \mathbf{L}_{k}^{NCBIS} - \mathbf{oft}_{k} \right) \middle/ \mathbf{B}_{k} \right\rfloor \cdot \mathbf{B}_{k} + \mathbf{oft}_{k}, \mathbf{U}_{k}^{NCBIS}, \mathbf{B}_{k} \right\rfloor$$

###

Figure 4.11: (a) Iteration space before strip-clustering a C-loop II with a step different from one. (b) Iteration space after strip-clustering a C-loop II with a step different from one.

and recall from Corollary 2 that the bounds of the MCS of NCBIS along dimension  $\mathbf{I}_k^{NCBIS}$  can be directly obtained from the bounds of NCBIS as follows:

$$\begin{aligned} \mathsf{L}_{k}^{MCS} &= \mathsf{L}_{k}^{NCBIS} - \mathsf{B}_{k} + 1 \\ \mathsf{U}_{k}^{MCS} &= \mathsf{U}_{k}^{NCBIS} \end{aligned}$$

Therefore, in our implementation of SMT, we will directly work with the bounds of the MCS of the NCBIS. This means that when we apply strip-clustering to a loop, we do not directly use the bounds obtained using the expressions in Figures 4.9 and 4.10. Instead, we use the bounds of the MCS.

#### 4.4.3 Steps of the Efficient SMT Implementation

Our implementation of SMT will generate the EL and TI loops of the final multilevel tiled code, one by one, from the innermost to the outermost one, by integrating the strip-clustering transformation with the loop bounds computation.

Firstly, the loops of the original code are the initial C-loops. In each iteration, the SMT algorithm performs two different actions:

- First, it applies the strip-clustering transformation to a C-loop, generating the new C-loop and the TI or EL-loop whose bounds are going to be computed.

- Second, the exact bounds of this just stripped TI or EL-loop are computed performing one iteration of the FM algorithm. If the just stripped loop is an EL-loop both steps of the FM algorithm are performed and if it is a TI-loop, only the first step is performed (Theorem 2).

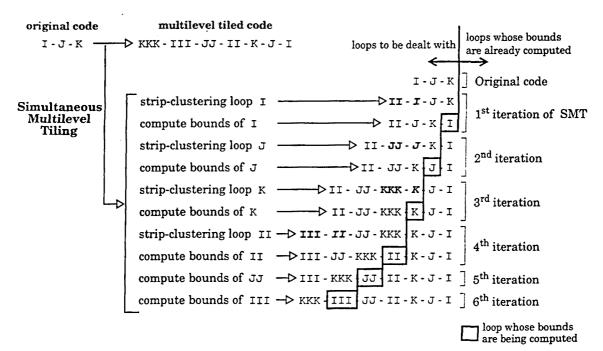

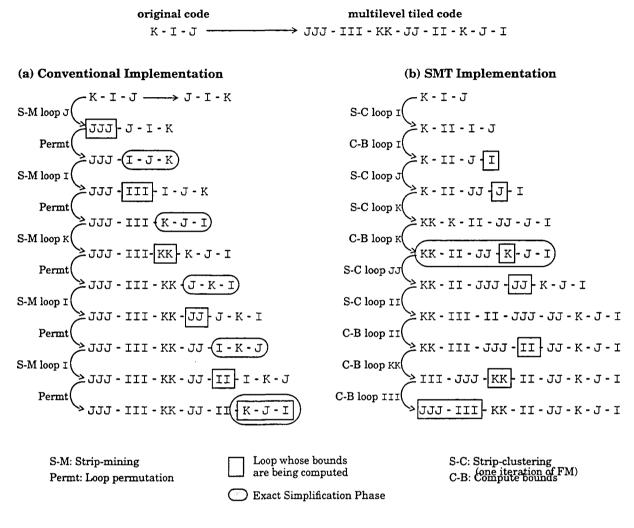

As an example, suppose that we have a 3-deep loop nest (I-J-K) and we want to obtain the multilevel tiled code (KKK-III-JJ-II-K-J-I). Figure 4.12 shows the order in which strip-clustering and the computation of the bounds are performed by our implementation of SMT. The loop list written in the rows labelled "strip-clustering" indicates which C-loop (in bold) and which TI or EL-loop (in bold+oblique) appear after strip-clustering. In rows labelled "compute bounds", we indicate that the TI or EL-loop just stripped is moved to the innermost position and that its bounds are being solved performing one iteration of FM.

Figure 4.12: Example of how the implementation of SMT works.

In the three first iterations of SMT only the *creating phase* of strip-clustering is performed, because the C-loops have steps equal to one. In the fourth iteration, strip-clustering is applied to a C-loop that has a step different from one (loop II), and therefore, both the *creating and the broadcasting phases* are performed.

In the broadcasting phase we have to take into account that there could be other loops between the just stripped TI-loop (II) and its associated EL-loop (I). These loops can have simple bounds that are affine functions of the just stripped TI-loop and, therefore, their bounds must also be modified in the broadcasting phase. In Fig. 4.12, 4<sup>th</sup> iteration of SMT, the bounds of loops JJ, KKK, K, J and I must be modified.

#### Theorem 3

Let III and II be the loop index variables of a C-loop and the just stripped TI-loop and let  $B_{\text{III}}$  and  $B_{\text{II}}$  be the strip sizes of III and II, respectively. The bounds of the loops between the just stripped TI-loop II and its associated EL-loop (including the EL-loop) must be modified in the broadcasting phase in the following manner: iteration variable II has to be substituted by  $\max(\text{III}, \text{II})$  if it appears in a lower (upper) simple bound and the coefficient that multiplies II is positive (negative) and by  $\min(\text{II}+B_{\text{II}}-1,\text{III}+B_{\text{III}}-1)-B_{\text{II}}+1$  if it appears in an upper (lower) simple bound and the coefficient is positive (negative).

#### Proof

Lets consider the following loop nest:

do I = L, U

do J =

$$\alpha_1 \cdot I + \theta_1$$

,  $\alpha_2 \cdot I + \theta_2$

enddo

where  $\alpha_1, \alpha_2, \theta_1, \theta_2$ , L and U are integer constants or program parameters (variables unchanged within the loops). Let assume that  $\alpha_1, \alpha_2 > 0$  and  $\alpha_1 \le \alpha_2$ .

Let's perform multilevel tiling using our efficient implementation of SMT to achieve the tiled code III-II-J-I (from outermost to innermost). First, strip-clustering is applied to loop I, obtaining the following code:

$$\begin{aligned} \text{do II} &= \lfloor (\text{L-oft}_{\text{II}}) / \text{B}_{\text{II}} \rfloor^* \text{B}_{\text{II}} + \text{oft}_{\text{II}}, \text{U}, \text{B}_{\text{II}} \\ \text{do I} &= \text{max}(\text{II}, \text{L}), \text{min}(\text{II} + \text{B}_{\text{II}} - 1, \text{U}) \\ \text{do J} &= \alpha_1 \cdot \text{I} + \theta_1, \alpha_2 \cdot \text{I} + \theta_2 \end{aligned} \tag{1}$$

enddo