# UNIVERSITAT POLITÈCNICA DE CATALUNYA Departament d'Enginyeria Electrònica

Campus Nord - Edif. C4, c/ Jordi Girona, 1-3, 08034 Barcelona, SPAIN

# Fabrication, Characterisation and Modelling of Nanocrystalline Silicon Thin-Film Transistors Obtained by Hot-Wire Chemical Vapour Deposition

Thesis presented for the qualification of PhD by

**Dosi Dosev**

Directors:

Dr. Josep Pallarès

Dr. Joaquim Puigdollers

**Tutor:**

Dr. Ramón Alcubilla

Barcelona 2003

### **Acknowledgements**

Today's research involves the efforts of specialists with different background and different points of view. This work would be impossible to accomplish without the collaboration of my colleagues from various universities and research centres. Hereby, I would like to acknowledge their fruitful collaboration.

En primer lugar quiero agradecer a mis directores de tesis J. Puigdollers y J. Pallares por la confianza que me han dado. He obtenido los primeros resultados experimentales gracias a J. Puijdollers quien me ha introducido en el mundo de los TFTs y ha hecho posible realizar toda la parte de fabricación de esta tesis. Por otra parte, doy mis gracias a J. Pallares cuya dirección ha sido tan importante para el desarrollo general de la tesis, así como para el trabajo de caracterización y modelado en concreto.

Quiero agradecer a R. Alcubilla por haberme aceptado en su grupo y por las buenas condiciones de trabajo de cuales he disfrutado en el DEE, Universitat Politécnica de Catalunya. Además, sus consejos de padre siempre han sido de gran valor para mí.

Doy mis gracias a X. Correig, por haber tenido la oportunidad de ser uno de los primeros becarios del DEEEA, Universitat Rovira i Virgili. Para mí han sido muy importantes sus palabras de coraje y de apoyo moral.

Agradezco a L.F. Marsal por las ideas originales en la caracterización de los TFTs. Gracias a esto han sido obtenidos los resultados relacionados con SCLC.

Gracias a A. Orpella por ayudarme en mis primeros pasos en la Sala Blanca. Muchas veces me he apoyado a su experiencia en las técnicas de fabricación.

Agradezco a los compañeros del Departamento de Física Aplicada y Optica, Universidad de Barcelona y especialmente a J. Andreu por haber depositado las capas de silicio nanocristalino. Sin su colaboración sería imposible fabricar las muestras experimentales.

Quiero expresar mis agradecimientos a B. Iñíguez quien me ha guiado en el trabajo teórico. Su gran experiencia ha sido clave para el desarrollo del modelo presentado en esta tesis.

I would like to express my gratitude to T. Ytterdal from the Norwegian University of Science and Technology for the excellent work environment and for being great supervisor and friend. Our fruitful discussions played a key role for the fast progress and the final success of the modelling work. Thanks to all my Norwegian friends – Jukka, Snorre, Johnny, Thomas, Per Gunnar for make me feel like at home.

Quiero agradecer a todos los becarios de URV y sobre todo a Mariana, Trifon, Radu y Gisela, por haber compartido las penas y las alegrías del doctorado.

Марианке и Трифани, благодаря ви че бяхме като едно семейство, споделяйки добро и лошо през всички тези години.

Agradezco a Miguel Angel por ser mi mejor amigo español. Gracias por haber estado para lo bueno y para lo malo.

I greatly acknowledge the Universitat Rovira i Virgili for the scholarship that I received all these years. This work would be impossible to accomplish without this support.

I must express my big gratitude to the Universitat Politècnica de Catalunya for the knowledge that I received in the PhD courses and for the additional financial support.

Special thanks to the Generalitat de Catalunya that supported my stay in NTNU, Trondheim, Norway.

I would like to acknowledge specially my professors from the Faculty of Physics, Sofia University "St. Kliment Ohridski" for the background that helps me a lot to do science.

Посвещавам този труд на моето семейство с благодарност за живота, възпитанието и образованието, които са ми дали. В памет на дядо Жечо. Посвещавам на Мики, заради обичта която ми дарява във всеки момент и за това, че винаги е била до мен, за да ме "побутне" в правилната посока, когато трябва. Не бих успял без нейната подкрепа.

### This work has been funded by:

Research scholarship from the *Departamento de Ingeniería Electrónica, Eléctrica y Automática (DEEEA) Universitat Rovira i Virgili (URV)*

Universitat Politècnica de Catalunya (UPC)

Consejo Interinstitucional de Ciencia y Tecnología (CICYT) Nº TIC 96-1058-C02-02 and Nº TIC99-0842-C03-03

Departament d'Universitats, Recerca i Societat de la Informació (DURSI), Generalitat de Catalunya.

## **Table of contents**

| 1. Introduction                                                         | . 1 |

|-------------------------------------------------------------------------|-----|

| 1.1. Fabrication of thin-film transistors                               | 4   |

| 1.1.1. TFT structures                                                   | 5   |

| 1.1.2. Techniques and materials for TFT's channel                       |     |

| 1.2. Electrical characteristics of thin-film transistors                | 10  |

| 1.2.1. Transfer characteristics                                         |     |

| 1.2.2. Output characteristics                                           |     |

| 1.2.3. Stability of the thin-film transistors                           |     |

| 1.3. Physics of thin-film transistors                                   |     |

| 1.4. Theoretical models for TFTs                                        |     |

| 1.5. Objectives                                                         |     |

| 2. Fabrication of nc-Si:H TFTs                                          |     |

| 2.1. Hot-Wire Chemical Vapour Deposition Technique.                     | 22  |

| 2.1.1. Description of the HVCVD                                         |     |

| 2.2. Fabrication steps                                                  | 26  |

| 2.2.1. Simplified sample                                                |     |

| 2.2.2. Complete sample                                                  |     |

| 2.3. Process parameters                                                 |     |

| 3. Electrical characterisation of the nc-Si:H TFTs                      |     |

| 3.1. Basic characterization                                             | 44  |

| 3.1.1. Transfer characteristics                                         |     |

| 3.1.2. Output characteristics                                           |     |

| 3.1.3. Saturation regime - threshold voltage and field-effect mobility. |     |

| 3.2. Advanced electrical characterization                               |     |

| 3.2.1. Activation energy measurements                                   |     |

| 3.2.2. Evaluation of the density of states                              |     |

| 4. Stability of the nc-Si:H TFTs                                        |     |

| 4.1. Threshold voltage behaviour under prolonged positive gate bias str |     |

|                                                                         |     |

| 4.2. Device characteristics under high positive and negative gate b     |     |

| stress                                                                  | 76  |

### Introduction

| 4.3. Influence of the positive and negative bias stress on the a    | activation |

|---------------------------------------------------------------------|------------|

| energy and on the density of states                                 | 78         |

| 4.3.1. Discussion                                                   | 83         |

| 4.3.2. Influence of the gate bias stress on the bulk defect states. | 88         |

| 5. Modelling of nc-Si:H TFTs                                        | 91         |

| 5.1. Analytical Device Model                                        | 92         |

| 5.1.1. Field – Effect Mobility in nc-Si:H and μc-Si:H               | 94         |

| 5.1.2. Drain Current Equations.                                     | 96         |

| 5.2. Numerical simulations of nc-Si:H performed by Atlas            | 103        |

| 6. Summary and conclusions                                          | 109        |

| Appendix                                                            | 115        |

| A1. Schematic structure of the HWCVD reactor                        | 116        |

| A2. Scanning electron microscopy (SEM) image of the deposited       | film. 117  |

| A3. X – ray diffraction (XRD) spectrum of the nc-Si:H film dep      | osited by  |

| HWCVD                                                               | 118        |

| A4. Complete set of equations of DC Spice model for nc-Si:H and     | d μc-Si:H  |

| TFTs                                                                | 119        |

| A5. List of abbreviations                                           | 122        |

| References                                                          | 1          |

| Publications related to this thesis                                 | 135        |

### 1. Introduction

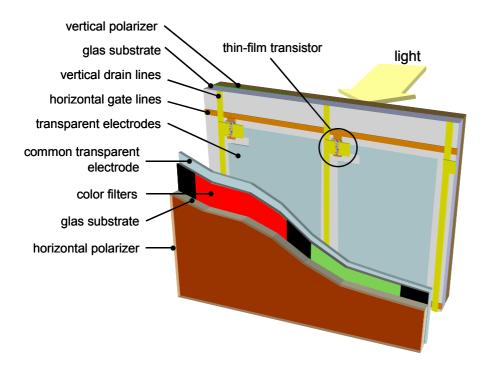

Large-area electronics involves active matrix liquid crystal displays (AMLCD) and image lectors [1]. These devices usually require transparent substrates with area of  $30\times60$  cm or larger. In Fig.1.1 is presented the pixel structure of colour AMLCD. It consists of two glass panels with liquid crystal substance injected between them. There is a fluorescent light source behind the back panel. First, the light passes through a vertical polarizer and

Figure 1.1. Structure of pixel in colour AMLCD

then enters in the liquid crystal substance through transparent electrode. Then the light passes through the second glass plate that has a transparent electrode, common for all the pixels, and after that through colour filter. The coloured light can be seen outside. On the back panel there are horizontal and vertical data lines that form two-dimensional address of each pixel. Thin-film transistors (TFTs) are field-effect transistors, used as switching elements between these addressing lines [2, 3].

The role of the TFT is to control the bias between the transparent electrode on the back plate and the common electrode on the second plate –

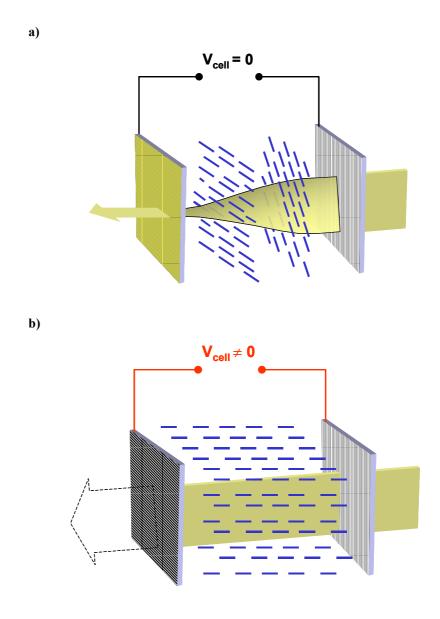

**Figure 1.2.** Liquid crystal cell operation; **a)** No voltage applied on the cell; **b)** With voltage applied on the cell

this voltage is applied over the liquid crystal cell. The vertical address lines are connected to the drains and the horizontal lines are connected to the gates of the transistors. When high voltages are applied simultaneously on the drain and on the gate, the TFT is in "ON" state and the drain voltage is applied to the liquid crystal cell. If low voltage is applied on either the drain or the gate line, the TFT is in "OFF" state and no voltage is applied on the liquid crystal cell.

Fig.1.2 describes the operation of the most commonly used twisted nematic liquid crystal cell [3]. When no voltage is applied on the cell (Fig.1.2.a), the liquid crystal molecules are oriented according to the orientations of the two polarizers, which are rotated at 90 degrees each to other. The entering light is polarized by the first polarizer, and then the light's polarization is rotated to 90 degrees by the liquid crystal molecules. This permits the light to pass through the second polarizer. In this manner, the cell is transparent for the passing light.

On the other hand, when voltage is applied on the liquid crystal cell, the liquid crystal molecules are oriented along the electric field (Fig.1.2.b). As the light does not change its polarization, it cannot pass through the second polarizer. Thus, when electric field is applied on the cell, the liquid crystal cell becomes no transparent for the light.

### 1.1. Fabrication of thin-film transistors

The role of the thin-film transistors as switching elements determines the required qualities of these devices. From fabrication point of view, TFTs must be compatible with the large-area glasses and with plastics from technological point of view. These materials usually suffer damages when they are submitted under high temperatures. On the other hand, the technology based on crystalline silicon uses temperatures in the range of 600-1100°C that are too high for glasses and plastics. Over more, silicon wafers have limited sizes and are non-transparent. This makes the

conventional silicon technology based on crystalline wafers to be incompatible with the large-area transparent substrates.

### 1.1.1. TFT structures

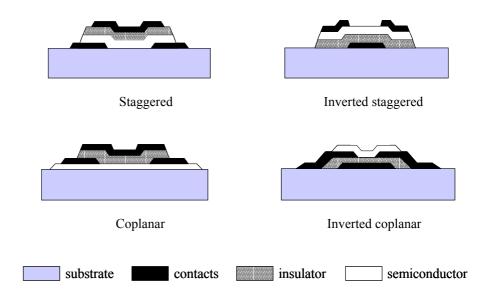

Usually the TFTs are fabricated by consecutive deposition of the gate, drain and source electrodes, the gate insulator and the semiconductor channel material. The deposition order determines the structure of the thin-film transistors [4]. The four basic structures of planar TFTs are shown in Fig.1.3. Basically, the TFTs can be *staggered* or *coplanar*.

In the staggered structures, the drain and source contacts are situated on one side of the semiconductor and the gate electrode is placed on the opposite side.

The coplanar structures have the three electrodes on the same side of

Figure 1.3. Basic thin-film transistors configurations

the semiconductor.

In the *inverted* (staggered or coplanar) structures, the gate electrode is the first layer deposited on the substrate. The type of the used structure influences the device electrical characteristics. They are strongly dependent on the quality of the top surface and the interface between the semiconductor and the gate insulator [4-8]. Passivating layers have been incorporated [9] and a variety of alternative structures have been proposed in order to improve the characteristics of the TFTs [10].

### 1.1.2. Techniques and materials for TFT's channel

As it was mentioned above, the conventional silicon technology based on crystalline silicon wafers is incompatible with the large-area electronics because of the high processing temperatures and the limited sizes of the wafers. This was the reason for the development of new techniques that could permit the silicon to be obtained by deposition over large surfaces at low temperature.

Deposition of silicon from silane (SiH<sub>4</sub>) gas is the origin of a variety of so called Chemical Vapour Deposition (CVD) techniques. LeComber et al. first proposed amorphous silicon films for device applications [11]. It was demonstrated that amorphous hydrogenated silicon (a-Si:H) could be obtained by glow discharge decomposition of SiH<sub>4</sub> and could be used for fabrication of transistors over large surfaces.

Plasma Enhanced Chemical Vapour Deposition (PECVD) is the most commonly used method to obtain amorphous silicon over large areas at low deposition temperatures (below 450°C) [1, 12-14]. Low deposition temperature makes possible the use of inexpensive substrates. The obtained material is amorphous silicon alloy with incorporated hydrogen atoms – hydrogenated amorphous silicon (a-Si:H).

Amorphous silicon is a material with disordered atomic structure that contains a lot of unsaturated (dangling) bonds. Defect states in the forbidden energy gap (the band gap) of the a-Si:H correspond to these dangling bonds. The hydrogen atoms tie up part of the dangling bonds and

help to decrease the density of defect states in the energy gap. This makes the hydrogenated amorphous silicon to have much better properties than other amorphous materials [11]. Nevertheless, a-Si:H has low values of *electron mobility*. The electron mobility  $\mu_n$  is a statistical parameter that characterizes the average value of the electron velocity  $\langle v \rangle$  due to applied electric field E ( $\langle v \rangle = \mu_n E$ ). Because of low electron mobility, devices based on a-Si:H are much slower then devices based on crystalline silicon. This limits a-Si:H material to pixel switch application. On the other hand, driver circuits, such as shift registers, multiplexers and amplifiers, require faster performance. These circuits are currently external to the flat panel array and require costly packaging to assemble [15].

Polycrystalline silicon (poly-Si) has an electron mobility that is several orders of magnitude larger than that of a-Si:H, typically  $\approx\!100$  cm²/Vs. This allows poly-Si to be applicable to the peripheral circuits. It consists of crystalline grains and amorphous-like grain boundaries. Hydrogen atoms passivate big part of the dangling bonds in the grain boundaries. The density of states in poly-Si is much lower than in a-Si:H and this determines the better electronic characteristics of poly-Si TFTs when compared to a-Si:H TFTs.

A variety of methods have been employed to obtain poly-Si material including direct deposition of poly-Si and different techniques for crystallization of deposited a-Si:H, such as Solid-Phase Crystallization (SPC) [16], Rapid Thermal Annealing (RTA) [17, 18], and laser crystallization [19, 20]. In the annealing techniques, the atoms in a-Si:H change their order and crystallize into new polycrystalline structure. The main disadvantage of the crystallization techniques is that high temperatures are required (near 600°C [15]). As a consequence, expensive substrates must be used for the fabrication of poly-Si TFTs. Another possibility to obtain poly-Si from a-Si:H is by metal-induced crystallization but its major disadvantage is the contamination of the silicon and the long processing times [21, 22].

Newly proposed approach is the direct deposition of silicon films with polycrystalline structure. This could be performed by layer-by-layer

deposition using PECVD [23]. The main drawback of this method is the low deposition rate of about 0.1 nm/s.

Very-high-frequency PECVD (vhf PECVD) or vhf Glow Discharge (vhf GD) is other improved PECVD method, which allows silicon films with grain sizes up to 20 nm to be obtained at high deposition rates [24, 25]. Nevertheless, deposition over large areas is an obstacle for the vhf PECVD technique.

High deposition rates and films with polycrystalline structure at the same time can be achieved by Hot-Wire Chemical Vapour Deposition (HWCVD), also known as Catalytic Chemical Vapour Deposition (cat-CVD) [26-31]. In this technique, silane molecule (SiH<sub>4</sub>) is cracked into silicon, hydrogen atoms and radicals like SiH, SiH<sub>2</sub> and SiH<sub>3</sub> by means of filament heated to 1600-1800°C. Silicon hydrogenated film with polycrystalline structure grows on the substrate surface from the gas phase. Hot-Wire CVD is much more successful in producing polycrystalline films than PECVD, because the hot filament is much more effective source of atomic hydrogen than the glow discharge [32]. Atomic hydrogen plays a key role for the growing of ordered polycrystalline network. It is not necessary to heat the substrate in excess in HWCVD. This permits inexpensive substrates to be used for the device fabrication. In addition, the HWCVD technique is expected to be easily scaleable to large areas [33].

The structure of the obtained materials varies from hydrogenated amorphous to polycrystalline with different grain size depending on the employed deposition technique and the corresponding deposition regime. Different authors give different names to the obtained materials according to their structures. For example, the classification of the thin silicon materials given by Schropp et al. [32] is presented in Table 1.1.

**Table 1.1.** Definitions for various morphologies of thin-film silicon

materials, reprinted from [32].

| Identification                        | Abbreviation | Phases                                    | Feature size        |

|---------------------------------------|--------------|-------------------------------------------|---------------------|

| Hydrogenated amorphous silicon        | a-Si:H       | Single phase amorphous                    | None                |

| Hydrogenated microcrystalline silicon | μc-Si:H      | Two-phase<br>amorphous and<br>crystalline | < 20 nm<br>crystals |

| Hydrogenated polycrystalline silicon  | poly-Si:H    | Single phase<br>with grain<br>boundaries  | Up to 100 nm        |

In the last 4-5 years, new terms were introduced for more precise description of the thin-silicon materials. In 1999, Bergmann [34] proposed more detailed classification of the polycrystalline silicon films according to their grain size (see Table 1.2). Usually the poly-Si is not called "hydrogenated", perhaps because of the relatively low hydrogen content in large-grained silicon films. Hydrogenated polymorphous silicon (pm-Si:H) is another new term that refers to material with isolated crystalline particles embedded in amorphous silicon [35-37].

**Table 1.2.** Classification of thin-silicon materials by their grain size

according to Bergmann [34].

| Identification                              | Abbreviation     | Grain size  |

|---------------------------------------------|------------------|-------------|

| nanocrystalline silicon                     | nc-Si            | ~ 10 nm     |

| microcrystalline or polycrystalline silicon | μc-Si<br>poly-Si | ~ 0.1100 µm |

| large-grained polycrystalline silicon       | poly-Si          | ~ 0.1100 mm |

All of the above mentioned techniques and materials were employed in producing TFTs. Plasma Enhanced CVD is the most commonly used in industry, while the majority of the other techniques are still object of research. Hot-wire (or cat-) CVD is one of the most promising techniques because of the high deposition rate of nc-Si:H and  $\mu$ c-Si:H at low substrate temperature [38].

# 1.2. Electrical characteristics of thin-film transistors

### 1.2.1. Transfer characteristics

For good image contrast in the flat screens, both states of the liquid crystal cell (transparent and no-transparent) must be clearly defined in order to assure close to 100% passing light in "transparent" state and close to 0% passing light in "no transparent" state. Once incorporated in the active matrix, TFTs must assure this big difference between both states of the liquid crystal cell and also fast transition between them.

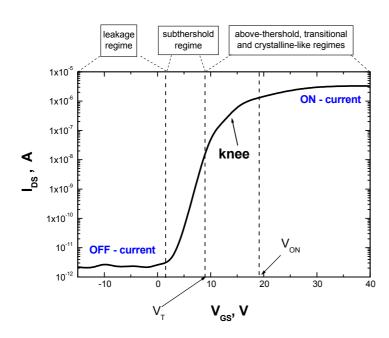

In Fig.1.4 is presented a typical transfer characteristic of n-channel

Figure 1.4. Typical transfer characteristic of n-channel a-Si:H TFT<sub>S</sub>.

TFTs with a-Si:H active layer. It shows the drain-source current ( $I_{DS}$ ) dependence on the gate voltage ( $V_{GS}$ ) at constant low drain – source voltage ( $V_{DS}$ ). Positive gate voltage provokes accumulation of electrons in the channel material near the gate insulator. Consequently, the sheet conductance increases and this leads to increasing of the drain-source current. On the other hand, negative gate voltage reduces the electron concentration near the gate insulator and provokes decreasing of the drain-source current. High  $I_{DSon}/I_{DSoff}$  (on/off) ratio is desirable in order to obtain good "transparent" and "no transparent" states of the liquid crystal cell. The on/off ratio is about 6 orders of magnitude in the conventionally used a-Si:H TFTs [2, 3]. Low value of the OFF current is easily achieved in a-Si:H TFTs because of the typically low conductivity of a-Si:H.

Limiting parameter for the ON current values is the electron mobility in the channel material. The mobility values in a-Si:H are much lower (< 1cm/Vs) than in crystalline silicon because of the high defect concentration in a-Si:H (about 10<sup>15</sup> cm<sup>-3</sup>) [1, 13].

Other important TFT parameter is the *threshold voltage*  $V_T$ , defined as the gate-source voltage at which conduction electrons begin to appear in the channel. Low threshold voltage is needed to assure working regime at reasonable voltage ranges. In the transfer characteristic, the threshold voltage can be determined at the beginning of the "knee" transition to "ON" current (see Fig.1.4) [39]. Nearly constant ON current is achieved at the end of the knee, where is defined the *ON voltage*  $V_{ON}$  [40]. In contrast to the conventional MOSFETs,  $V_T$  differs from  $V_{ON}$  in a-Si:H and poly-Si TFTs due to the elevated density of states.

The subthreshold slope of the transfer characteristics should be high enough in order to assure fast transition between ON and OFF states of the transistor. It is strongly dependent on the density of defect states in the channel material [41, 42].

Low value of the  $I_{DSoff}$  is necessary for high on/off ratio of the transfer characteristics. Nevertheless, accumulation of holes near the gate may occur at high negative gate voltages and this could provoke an increasing of the  $I_{DSoff}$ . One possible solution of this problem is to introduce n+ doped layers into the drain and source contacts. The hole current will be eliminated by recombination in the n+ doped zones. In the same time, the n+

zones will also improve the ON current avoiding possible Schottky barrier between the drain and source metal contacts and the silicon channel material.

As polycrystalline silicon has lower density of states than a-Si:H, the TFTs made by poly-Si usually show much higher field-effect mobility, higher levels of the I<sub>DSon</sub> and higher subthreshold slope.

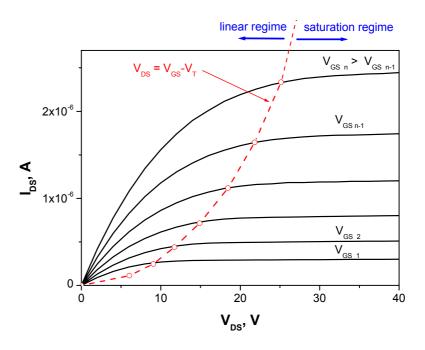

### 1.2.2. Output characteristics

The typical TFT *output* characteristics are shown in Fig.1.5. They represent the dependence of the drain-source current ( $I_{DS}$ ) on the drain-source voltage ( $V_{DS}$ ) at different gate voltages ( $V_{GS}$ ). The drain-source current increases linearly at low drain-source voltages (*linear regime*) and saturates at high drain-source voltages (*saturation regime*). The saturation values of  $I_{DS}$  depend on the applied gate voltage. When low gate voltage is applied, the thickness of the induced channel is small and the current saturates at low values. On the other hand, thicker channel is induced at high gate voltages and the saturation current is higher. Well-separated output characteristics are an indication of good ohmic drain and source contacts. The transistor enters in *saturation regime* when  $V_{DS} > V_{SAT}$ , where  $V_{SAT} = V_{GS} - V_{T}$ . In Fig.1.5, the points corresponding to  $V_{DS} = V_{SAT}$  are connected with dashed line described by the following equation:

$$I_{DS} = \frac{W}{L} \mu_{fet} C_{ox} \frac{1}{2} (V_{GS} - V_T)^2$$

(1.1)

where W and L are the width and the length of the transistor channel,  $\mu_{fet}$  is the field-effect electron mobility and  $C_{ox}$  is the gate insulator capacitance. The threshold voltage and the field effect mobility can be determined from measurements of the saturation current, plotting the square root of the measured  $I_{DS}$  vs.  $V_{GS}$  in saturation (at  $V_{DS} \ge V_{GS}$ - $V_T$ ).

Figure 1.5. Typical output characteristics of n-channel a-Si:H TFT<sub>S</sub>.

For the poly-Si TFTs, one possible undesirable effect is the injection of hot electrons from the drain electrode at high drain-source voltages. This is so-called Kink effect that occurs when some electrons acquire high enough energy to provoke electron-hole generation. This could lead to an avalanche increasing of the electron current, which provokes degradation of the device [43-46].

### 1.2.3. Stability of the thin-film transistors

One of the disadvantages of the amorphous silicon films is that they suffer degradation when submitted under high prolonged electrical biases or illumination (Staeber-Wronski effect [47]). As a consequence, the electrical characteristics of the TFTs ( $V_T$ ,  $\mu_{fet}$ , and subthreshold slope) change and this damages the overall device performance.

One of the possible effects due to electrical stress is the breaking of weak silicon-silicon bonds [48]. As a consequence, new unsaturated dangling bonds appear in the material. These new defects act as traps for electrons. The total density of states increases and this changes the electronic properties of the material. Usually, thermal or bias annealing is necessary in order to recover the initial device performance [1, 48]. The defect state creation in TFTs is possible under both positive and negative gate biases [10]. The consequence of the defect-state creation is an increasing of the threshold voltage under both positive and negative bias stresses.

Other possible effect due to electrical stress is the charge trapping in the gate insulator and/or in the interface between the gate insulator and the channel material [3, 10]. When charge trapping takes place, the threshold voltage is shifted towards higher values under positive bias stress and towards lower values under negative bias stress [9, 48].

Amorphous silicon is highly disordered material. Degradation in a-Si:H occurs at much lower energies than in crystalline silicon. This is why poor stability is a serious problem in a-Si:H TFTs. In contrast, poly-Si is expected to be much more stable than a-Si:H because of its higher long-range order. Thus, the aim of many researchers is to obtain TFTs based on poly-Si:H with largest possible grain size at the lowest possible temperature [1].

### 1.3. Physics of thin-film transistors

The conduction mechanisms in TFTs are determined by the physical properties of the channel material.

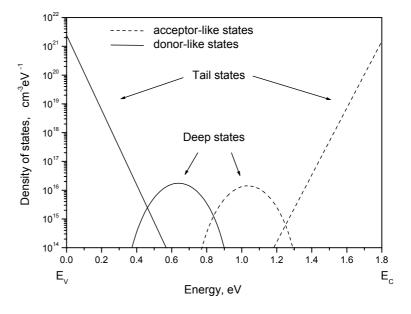

Hydrogenated amorphous silicon has an energy gap of about 1.8 eV. Its electronic properties depend on the density of states (DOS) in the bandgap. In a-Si:H TFTs, the elevated DOS is responsible for the threshold voltage value, the field effect mobility and the Fermi level position [1].

In Fig.1.6 is shown the simplified distribution of DOS in a-Si:H. It consists of two exponential *band tails* and two Gussian distributions of *deep states* [48]. Tail states are the result of the differences between the bond

**Figure 1.6.** Simplified distribution of the density of states for intrinsic amorphous silicon

lengths and bond angles in the a-Si:H. Deep states correspond to the unsaturated (dangling) bonds [13, 49].

The states in the upper half of the energy gap behave as *acceptor-like states*. They are neutral when are empty and negatively charged when are filled. The states in the bottom half of the energy gap behave as *donor-like states*. They are positively charged when are empty and neutral when are filled [48, 50]. When a-Si:H is incorporated in TFTs, the density of states can be determined by field effect measurements. Nevertheless, the DOS shape obtained by field effect measurements includes not only the intrinsic states of a-Si:H but also the states corresponding to dangling bonds at the interface a-Si:H/insulator [1, 4, 10].

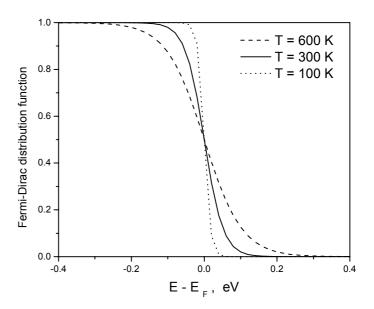

In intrinsic a-Si:H, the Fermi level  $E_F$  is situated at about 0.6 eV from  $E_C$  which is slightly higher than the middle of the forbidden energy gap [50]. According to the semiconductors physics, the occupancy of the states in the bandgap is given by the Fermi – Dirac function:

$$f_n = \frac{1}{1 + \exp\left(\frac{E - E_F}{k_B T}\right)} \tag{1.2}$$

Here  $f_n$  is the probability state with an energy E to be occupied by an electron;  $k_B$  is the Boltzmann constant and T is the absolute temperature. In Fig.1.7 is plotted the Fermi-Dirac function for different temperatures. The probability for state occupancy is 50% for the Fermi level. The solid line corresponds to the room temperature and shows that the probability for state occupancy is about 30-40% for energy  $E=E_F+k_BT$  ( $k_BT\approx 0.026$  eV at room temperature). Therefore electrons will appear in the conduction band when  $E_F$  is situated at about 0.026 eV from  $E_C$ .

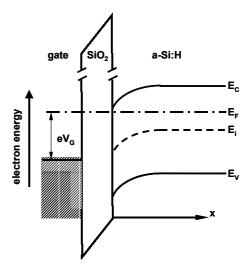

By applying positive voltage to the gate electrode, electrons are induced in the amorphous silicon near the gate insulator/a-Si:H interface. These electrons fill the available deep localized states upward  $E_{\text{F}}$ . The bands at the silicon/gate insulator interface bend down as it is shown in Fig.1.8. The Fermi level shifts up towards  $E_{\text{C}}$  and the sheet conductivity near the interface increases.

**Figure 1.7.** Fermi – Dirac distribution function for different temperatures

**Figure 1.8.** Potential diagram of metal gate, silicon dioxide, and a-Si:H cross section under positive gate voltage applied on the gate.

If small drain—source voltage is applied, the drain current increases exponentially with the gate voltage and the rate of increase is inversely proportional to the density of the deep states. With a further increase in the gate voltage, more states are filled and the Fermi level moves closer to the conduction band. This is the *subthreshold* (also called below-threshold) regime (Fig.1.4) [4, 10, 50].

Tail states density increases exponentially with the energy. There are much more states per short energy interval close to the conduction band than in the midgap. Thus, once the Fermi level enters in the tail states, most of the charge is induced into states above  $E_{\rm F}$ . The shift of the Fermi level with the gate voltage is significantly smaller than in the below threshold voltage. Only small part of the induced charge goes into the conduction band. This is the *above threshold* regime.

When the tail states near the a-Si:H/insulator interface are almost completely filled, the Fermi level touches the bottom of the conduction band and the mobile charge increases with the gate voltage. Shur [50] defines this as *transitional regime*.

Crystalline-like regime is achieved when most of the induced charge goes into the conduction band at higher gate voltages. In this regime the field effect mobility gets close to the band mobility and the operation of the a-Si:H TFT becomes similar to the crystalline field-effect transistor. In a-Si:H TFTs crystalline-like regime is achieved at gate voltages about 50-100 V [50]. This values are too high for practical applications. Usually the on-state of a-Si:H TFTs is in above threshold regime at gate voltages about 20-40 V. In this voltage range, the field effect mobility does not achieve the band mobility values and has typical values about 0.5 - 1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [51, 52]. This low value is the main disadvantage of a-Si:H and is due to the elevated density of states. This drawback of a-Si:H can be avoided using polycrystalline hydrogenated silicon poly-Si:H. It has electron mobility of 30-100 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [51, 53] and good stability under bias stress and illumination.

The physics of polycrystalline silicon is also strongly related to the density of defect states in the grain boundaries. Important difference between the poly-Si:H and a-Si:H TFTs is that the defects in poly-Si are concentrated mainly in the grain boundaries while in a-Si:H material they are

approximately uniformly distributed in the bulk. That is why the overall DOS in poly-Si:H is much lower than in a-Si:H. On the other hand, in poly-Si, the smaller is the grain size, the higher is the grain boundaries concentration and higher is the density of states. Therefore, the physical properties of poly-Si:H vary according to the grain size. Smaller grain size determines properties similar to those of a-Si:H, while large grain size determines properties closer to crystalline silicon [54-56].

### 1.4. Theoretical models for TFTs

Both amorphous and polycrystalline silicon TFTs are used for practical purposes. For their implementation in circuit design, Spice models were created, based on the physical properties of a-Si:H and poly-Si:H TFTs, respectively [39, 51, 57]. These models were implemented in commercial software for circuit design and simulation such as Aim Spice [58], Eldo [59] and Star-HSpice [60].

Density of states is the main model parameter determining the characteristics of a-Si:H TFTs. Leakage, subthreshold and above-threshold regimes are predicted by the a-Si:H model [39, 51]. Weak function of the gate voltage describes the field effect mobility:

$$\mu_{fet} = \mu_n \left( \frac{V_{GTe}}{V_{AA}} \right)^{\gamma} \tag{1.3}$$

where  $\mu_n$  is the electron mobility in the conduction band,  $V_{GTe}$  is the effective value of  $V_{GT}=V_{GS}-V_T$ ,  $V_{AA}$  (with typical value of  $3.7\cdot10^5$ ) is the characteristic voltage for  $\mu_{fet}$  and  $\gamma$  (with typical value of 0.3) is a power law mobility parameter.

In the model of poly-Si:H TFTs, Kink regime and corresponding parameters are also taken into account in addition to the leakage, subthreshold and above-threshold regimes. As the density of states in poly-Si is much lower than in a-Si:H, this parameter is not directly included in the

poly-Si TFT model. Unlike  $\mu_{fet}$  from the a-Si:H TFT model, the function describing the field effect mobility in poly-Si TFT model, increases rapidly at low gate voltages until band mobility value is achieved.

Both models include equations that describe temperature dependences. Parasitic capacitances are also taken into account for dynamic regimes. Model corrections were developed to consider short-channel effects in small size TFTs [61, 62].

### 1.5. Objectives

The objectives of this thesis are:

- To employ photolithography techniques in order to fabricate thin –

film transistors based on silicon hydrogenated film, directly

deposited by hot-wire chemical vapour deposition (HWCVD) at

high deposition rate and low substrate temperature.

- 2. To perform detailed electrical characterisation of the fabricated thin —film transistors. To measure the output and the transfer characteristics. To determine the threshold voltage and the field effect mobility. To characterize the activation energy and density of states by means of thermally activated current measurements.

- 3. To evaluate the stability of the deposited film and fabricated devices under electrical stress. To study the threshold voltage shift, the activation energy and the density of states behaviour under prolonged gate bias stress.

- 4. To carry out theoretical analysis of the transistor's electrical characteristics. To develop spice model for the fabricated transistors in order to make possible their use in circuit design and simulation.

### 2. Fabrication of nc-Si:H TFTs

In this chapter is described, step by step, the fabrication process of the thin film transistors, made by hot-wire chemical vapour deposition (HWCVD) of thin silicon film on oxidised silicon wafer. Firstly, the HWCVD set-up and the deposition process parameters are explained. Secondly, the structural characteristics of the deposited film are commented. Finally, the photolithography steps and the parameters employed are described.

# 2.1. Hot-Wire Chemical Vapour Deposition Technique.

Hot-Wire Chemical Vapour Deposition (HWCVD), also known as Catalytic Chemical Vapour Deposition (cat-CVD) has been studied as a possibility to obtain polycrystalline hydrogenated silicon films with a small grain size at low temperature and high rate of deposition [27-31, 63, 64]. This makes the HWCVD attractive for the fabrication of high-quality thin-film transistors over inexpensive glass substrates.

#### 2.1.1. Description of the HVCVD

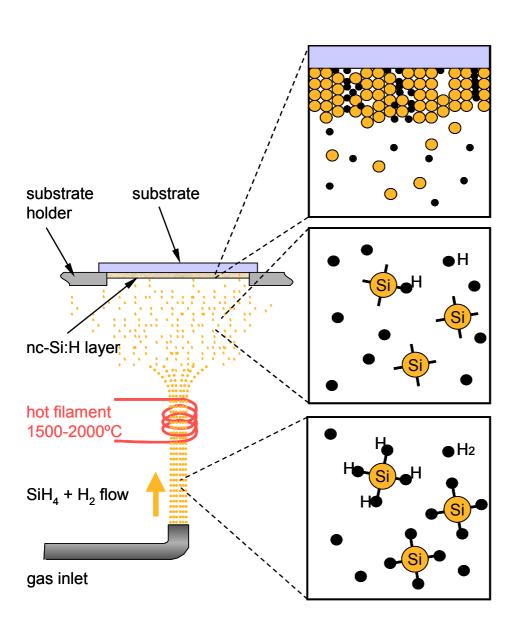

The HWCVD technique consists in the dissociation of a gas mixture containing silane by means of metallic filament (usually W or Ta) resistively heated up to  $1500-2000^{\circ}$ C. Such elevated temperature, combined with low pressures of  $10^{-3}$  to  $10^{-1}$  mbar, leads to cracking of the gas molecules and deposition of silicon film. A variety of silane (SiH<sub>4</sub>) dissociation reactions are possible, depending on the filament temperature and other technological conditions. The main possible decomposition reactions are [31]:

$$SiH_{4} \xrightarrow{T > 1500^{\circ}C, \\ P = 10^{-3} - 10^{-1} \text{ mbar}} SiH_{3} + H$$

$$T > 1500^{\circ}C, \\ P = 10^{-3} - 10^{-1} \text{ mbar}$$

$$SiH_{4} \xrightarrow{T > 1500^{\circ}C, \\ P = 10^{-3} - 10^{-1} \text{ mbar}} SiH_{2} + 2H$$

$$SiH_{4} \xrightarrow{SiH_{4} + 2H} SiH_{2} + 2H$$

Some secondary reactions are also possible depending on the conditions [32]:

$$Si + SiH_4$$

$\longrightarrow$   $SiH_2 + H_4$

$H + SiH_4$   $\longrightarrow$   $SiH_3 + H_2$

The SiH<sub>3</sub> radicals are said to be the most important for the growing of microstructures [32]. The concentration of atomic hydrogen plays a role in creating these radicals as well as in balancing the hydrogenation and etching of the growing surface. Hydrogen atoms etch silicon from disordered or strained bonding states, leading to a transition from an amorphous network to microcrystalline network. The reason why HWCVD is much more successful in producing polycrystalline films without any amorphous tissue than PECVD is the fact that the hot filament is a much more effective source for atomic hydrogen than a glow discharge is [32]. Over more, in contrast to PECVD no ion bombardment of the substrate is present during HWCVD. TFTs therefore profit from the absence of the interface damage due to the ion impact [33].

An additional advantage of HWCVD is that it permits to obtain n doped or p doped materials by adding phosphine (PH<sub>3</sub>) or diborane (B<sub>2</sub>H<sub>6</sub>), respectively, to the gas mixture.

In Fig.2.1 is illustrated the HWCVD deposition process. The gas mixture SiH<sub>4</sub>/H<sub>2</sub> enters in the vacuum chamber from gas inlet that is situated on the bottom side of the chamber. The substrate is situated on the topside of the chamber and is oriented downwards. Independent heater controls the substrate's temperature. The hot filament is situated between the gas inlet and the substrate. The above-mentioned dissociation reactions take place when the gas mixture passes through the filament. The resulting radicals form thin silicon hydrogenated film on the substrate surface. The structural properties of the deposited film depend on the following main deposition parameters [31]:

Figure 2.1. Description of Hot-Wire Chemical Vapour Deposition process

- filament temperature (T<sub>f</sub>) it determines the nature of the dissociation products and the composition of the gas-phase during the film growth;

- substrate temperature (T<sub>s</sub>) it determines the dynamics of the film growth and influences the crystallinity of the deposited film;

- filament to substrate distance (d<sub>s-f</sub>) it influences the nucleation, the growth rate, and hot-wire to the substrate heating;

- process pressure (P) it determines the free path of the different dissociation products and their mobility onto the growing layer, thus it influences the gas phase composition and the deposition rate;

- hydrogen dilution the amount of hydrogen added to the mixture of hydrogen and silane determines the partial pressure of both gases and is crucial for the properties of the deposited film.

- filament material the influence of the filament material on the growing layer structure was communicated recently [65].

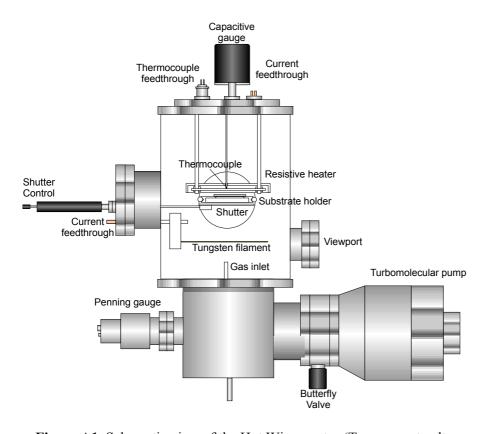

One of the main objectives of this work is to prove the feasibility of the HWCVD process for the fabrication of high quality thin–film transistors at low process temperature of the substrate. We used oxidized silicon wafer as a substrate in order to simplify our study and to avoid possible problems due to gate insulator quality, substrate properties, etc. Gate silicon dioxide layer was grown thermally under industrial conditions and was used as a gate insulator. Over the gate SiO<sub>2</sub> was deposited thin silicon hydrogenated using the HWCVD reactor, of the Department of Applied Physics and Optics at University of Barcelona. Picture of the reactor is shown in Fig.2.2. The schematic structure and detailed description of the HWCVD reactor, according to D. Peiró [31], is shown in Appendix A1. Chromium layer was evaporated over the deposited film and drain and source contacts were formed by means of standard photolithography techniques. Crystalline silicon wafer was used as a gate contact of the transistors.

**Figure 2.2.** Picture of the Hot-wire CVD chamber, situated in the Department of Applied Physics and Optics, Universitat de Barcelona

Following this procedure, series of samples were fabricated in order to adjust the process parameters and to obtain TFTs with the best possible electrical characteristics. The initially obtained devices showed poor electrical characteristics due to very low values of the active layer conductivity. Nevertheless, TFTs with good electrical characteristics were obtained after optimisation of the HWCVD deposition parameters. The performed electrical measurements provided useful feedback information that helped the deposition process to be optimised. In this thesis is presented the fabrication process of the devices with the best performance.

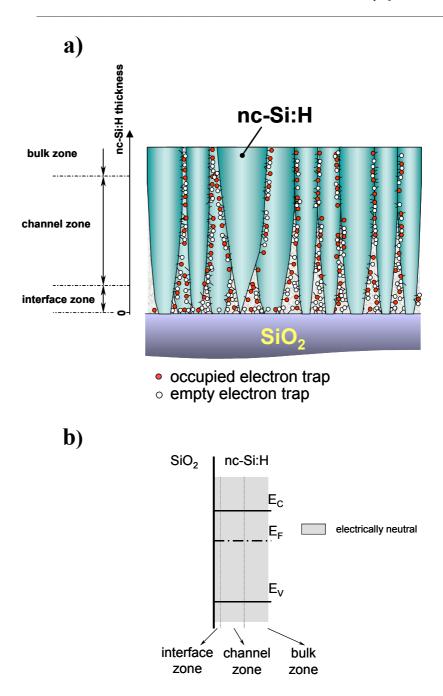

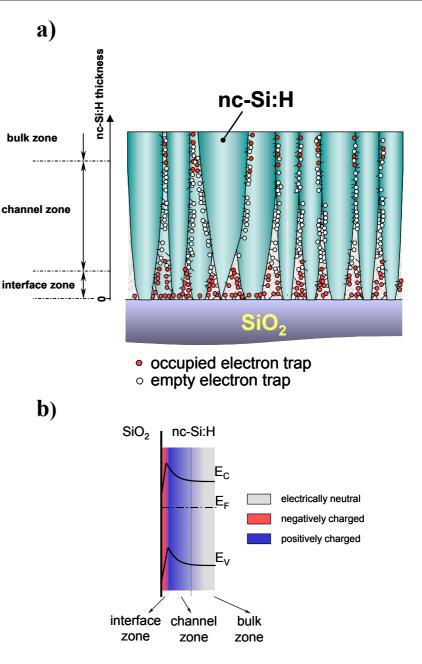

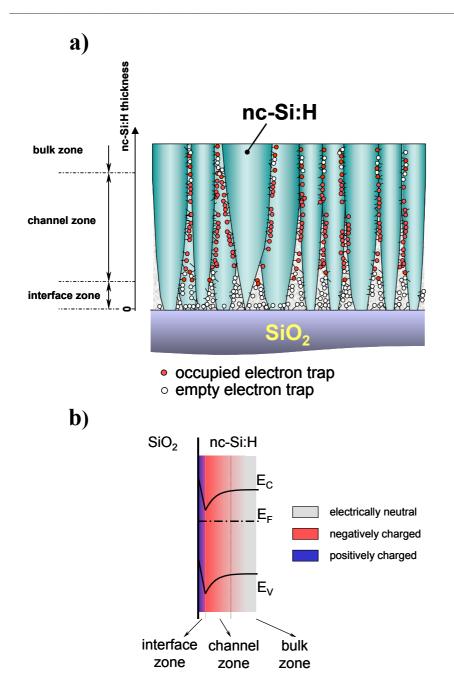

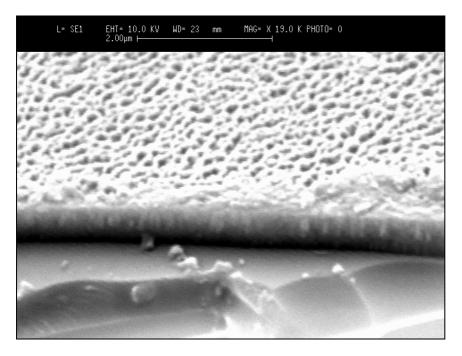

The thickness of the deposited layer was determined by scanning electron microscopy (SEM). It was 220-250 nm. The SEM image of the layer is presented in Appendix A2. It can be easily noted that the layer has polycrystalline columnar structure. Usually, the crystalline grains that form

the layer have width of about 7-8 to 20 nm, determined by high-resolution transmission microscopy (HRTEM) [31]. That is why this material was called nanocrystalline hydrogenated silicon (nc-Si:H). A common property of the layers grown by HWCVD with participation of W (tungsten) hot filament is that the column width is smaller and layer structure is highly disordered near the interface with the SiO<sub>2</sub> [66]. At certain distance from the interface, the columns become wider.

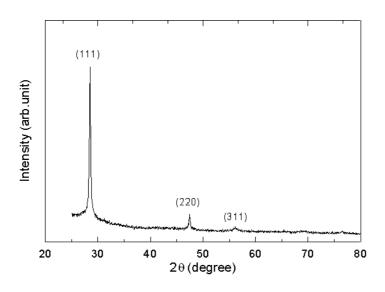

The layer was also characterised by X-ray diffraction (XRD). In Appendix A3 can be seen the main crystalline silicon diffraction peaks of the XRD spectrum. The relative intensities of the (111), (220) and (311) peaks do not coincide with those obtained for powder c-Si, which indicates that crystalline grains are not randomly oriented in the layer. The crystalline grains in the layer have preferential orientation (111). Some presence of orientation (220) is also observed. This is a typical XRD spectrum for layers deposited in this reactor [31].

# 2.2. Fabrication steps

The thin-film transistors were fabricated in the clean room facility of the Department of Electronics Engineering, UPC. N-type (100) silicon wafer with a resistivity of 1-10  $\Omega$ ·cm was used as a substrate for the TFTs. Firstly, we thermally grew thick silicon dioxide. Secondly, windows were opened in the silicon dioxide and thin high-quality gate oxide was grown in the windows. This thin SiO<sub>2</sub> was grown at the "Centro Nacional de Microelectrónica" (CNM), Bellaterra. After that, thin nc-Si:H film and metal layer were consecutively deposited over all the wafer surface. Finally, the thin-film transistors were formed by photolithography techniques. Next, the details about the fabrication steps are described.

# 2.2.1. Simplified sample

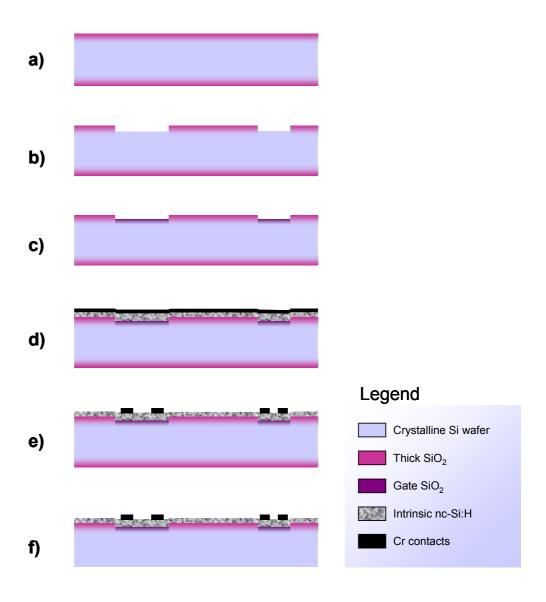

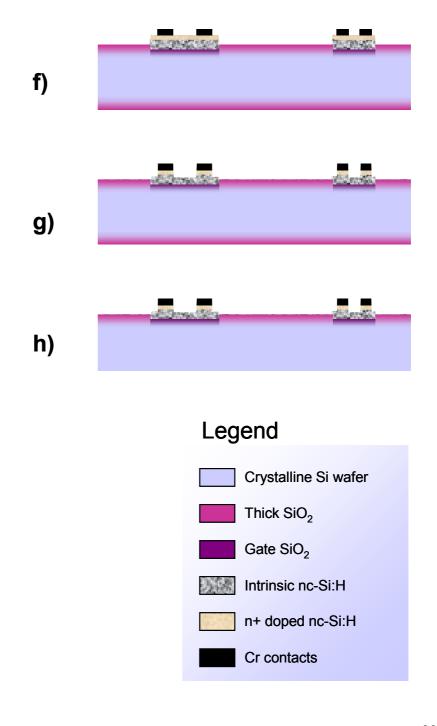

The first sample that showed good transistor characteristics was obtained performing the following fabrication steps (depicted in Fig.2.3):

- 1. Silicon wafer oxidation (Fig.2.3.a)

- 2. Silicon dioxide photolithography (Fig.2.3.b)

- 3. Gate SiO<sub>2</sub> growth (Fig.2.3.c)

- 4. Intrinsic nanocrystalline hydrogenated silicon (nc-Si:H) film deposition

- 5. Deposition of Cr layer by means of evaporation (Fig.2.3.d)

- 6. Formation of the drain and source contacts (Fig.2.3.e)

- 7. Bottom SiO<sub>2</sub> etching (Fig.2.3.f)

The process parameters of each fabrication step are described in Section 2.3 of this chapter.

# - Sample properties.

The resulting TFT structure was inverted staggered. The crystalline Si wafer was a common gate for all the transistors. The intrinsic nc-Si:H layer was also common for all the TFTs on the wafer. Therefore, the transistors were not electrically isolated from each other. The drain and the source contacts were directly deposited over the nc-Si:H layer. This fabrication process contains minimum amount of steps and permits to obtain the necessary information about the basic properties of the nc-Si:H TFTs. The devices based on this structure permitted the initial electrical characterisation of the TFTs. The obtained electrical characteristics are commented in Chapter 3.

**Figure 2.3.** Fabrication process of nc-Si:H TFTs with simplified structure.

- a) silicon wafer oxidation; b) gate patterning; c) gate SiO<sub>2</sub> growth;

- d) nc-Si:H layers growth and metallization; e) metal contacts formation;

- f) bottom SiO<sub>2</sub> etching and final device aspect.

The main disadvantage of this simplified structure is that the transistors are not separated electrically from each other. This makes impossible to study the behaviour of each device independently. In addition, the direct deposition of the Cr layer on the intrinsic nc-Si:H does not guarantee good ohmic contacts at the drain and the source.

# 2.2.2. Complete sample

The inconveniences of the simplified sample were avoided introducing an additional photolithography step. Thus, n+ doped nc-Si:H layer was incorporated in order to improve the drain and source contacts.

# - Fabrication steps.

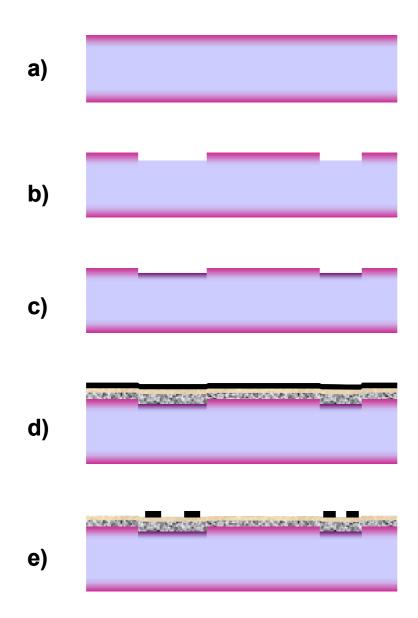

The complete fabrication process consists in the following steps (see Fig.2.4):

- 1. Silicon wafer oxidation (Fig.2.4.a)

- 2. Silicon dioxide photolithography (Fig.2.4.b)

- 3. Gate SiO<sub>2</sub> growth (Fig.2.4.c)

- 4. Intrinsic nanocrystalline hydrogenated silicon (nc-Si:H) film deposition

- 5. n+ doped layer growth

- 6. Deposition of Cr layer by means of evaporation (Fig.2.4.d)

- 7. Formation of the drain and source contacts (Fig.2.4.e)

- 8. Thin-film transistors separation (Fig.2.4.f)

- 9. Dry etching of the surface n+ doped layer (Fig.2.4.g)

- 10. Bottom SiO<sub>2</sub> etching (Fig.2.4.h)

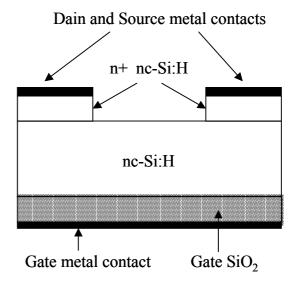

# - Sample properties

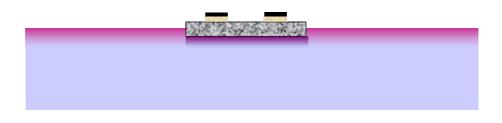

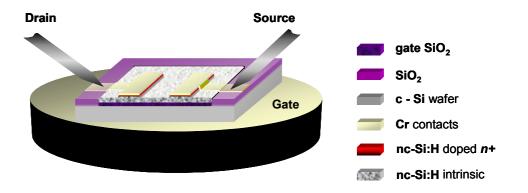

The final structure of the devices is shown in Fig.2.4.h. They have bottom - gated, inverted – staggered structure The specific conductivity of the crystalline wafer is orders of magnitude higher than the conductivities of SiO<sub>2</sub> and nc-Si:H. That is why, we used the bottom surface of the silicon wafer as a common gate contact for all the TFTs on the wafer. The channel, the drain and source contacts of each transistor on the wafer are electrically isolated from the other transistors. This structure permits to study the electrical characteristics and the stability of the transistors independently from each other.

**Figure 2.4.** Fabrication process of nc-Si:H TFTs for the complete device with incorporated n+ doped layers at the drain and source contacts. a) silicon wafer oxidation; b) gate patterning; c) gate SiO<sub>2</sub> growth; d) nc-Si:H layers growth and metallization; e) metal contacts formation; f) transistors separation; g) n+ layer etching; h) final device aspect.

# 2.3. Process parameters

#### - Silicon wafer oxidation

As a substrate it was used n-type silicon wafer with orientation (100) and specific resistance of 1-10  $\Omega$ .cm. The wafer was thermally oxidised in furnace under the following conditions:

15 min in presence of O<sub>2</sub> at 1100°C 60 min in presence of O<sub>2</sub> + H<sub>2</sub> gas mixture at 1100°C 15 min in presence of O<sub>2</sub> at 1100°C

Under these conditions the following chemical reaction takes place on the silicon wafer surface:

$$Si + O_2 \rightarrow SiO_2$$

As a result, silicon dioxide layer with thickness of approximately 500 nm was grown on both sides of the wafer.

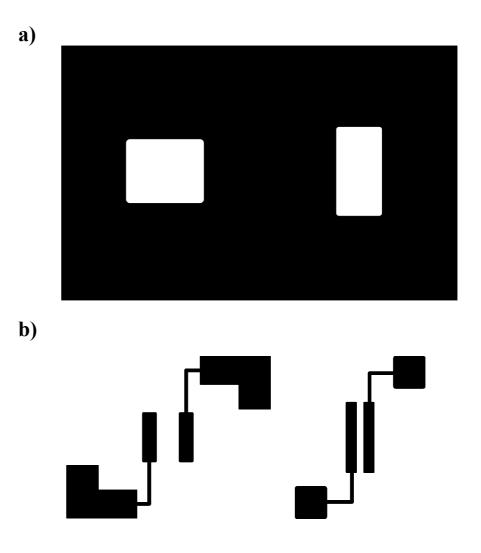

### - Silicon dioxide photolithography

Using standard photolithography technique windows were opened in the thermally grown silicon dioxide. A fragment of the employed mask is presented in Fig.2.5.a. The dark area was protected by positive photoresist, while the bright areas were left unprotected. The purpose of this patterning was to define separated transistors on the wafer. The unprotected  $SiO_2$  layer was chemically etched using 48% dilution of HF + NH<sub>4</sub>F mixture (HF:NH<sub>4</sub>F = 1:9). The etching rate was approximately 1 nm/s. Finally the photoresist was removed chemically from the wafer surface.

**Figure 2.5.** Fragments of the employed masks in the photolithography processes during the fabrication of the nc-Si:H thin-film transistors. a) gate insulator definition mask. b) drain and source contacts definition mask

## - Gate SiO<sub>2</sub> growth

High –quality SiO<sub>2</sub> layer was thermally grown in the opened windows, as a gate insulator of the devices. The SiO<sub>2</sub> layer was grown under industrial conditions at *Centro Nacional de Microelectronica* (CNM) CSIC, Bellaterra in order to avoid possible problems due to gate insulator quality. The gate oxide parameters were:

- thickness: 220-250 nm

- relative dielectric permittivity:  $\varepsilon_r = 3.9$

### - Intrinsic nanocrystalline hydrogenated silicon (nc-Si:H) film deposition

An intrinsic nc-Si:H film was deposited onto the wafer surface in the HWCVD reactor (see Appendix A1), using the following deposition parameters:

Pressure:  $P = (3.8 \pm 0.1) \cdot 10^{-2} \text{ mbar}$

Substrate temperature:  $T_s = 125$ °C

Silane/hydrogen flow ratio:  $SiH_4/H_2 = 4/76$  sccm

Substrate – filament distance:  $d_{s-f} = 5 \text{ cm}$ Filament temperature:  $T_f = 1700 ^{\circ}\text{C}$ Deposition rate  $0.8 \pm 0.1 \text{ nm/s}$

The obtained film had thickness of about 220-250 nm and the structural characteristics described in Appendix A2 and A3.

### - n+ doped layer growth

After growing the intrinsic nc-Si:H film, phosphine gas (PH<sub>3</sub>) was added to the gas mixture in order to obtain n+ doped nc-Si:H layer. The process

Fabrication of nc-Si:H TFTs

parameters were kept as in the intrinsic layer deposition excepting the gases flow ratio, which in this step was adjusted as follows:

Phosphine/Silane/hydrogen flow ratio:  $PH_3 / SiH_4 / H_2 = 0.3 / 4 / 76$  sccm

The thickness of the n+ doped layer was 50 nm approximately.

- Deposition of Cr layer by means of evaporation

Thin chromium (Cr) layer was evaporated over the nc-Si:H layer in order to create drain and source contacts. The thickness of the Cr layer was 50 nm approximately.

- Drain and source contacts formation

The drain and source contacts on the structure surface were formed by standard photolithography techniques. The pattern of the used mask is shown in Fig.2.5.b. The chromium surface corresponding to the dark area was protected by means of positive photoresist. The unprotected part of the Cr layer was etched chemically using HCl acid, under the following conditions:

Dilution of HCl /  $H_2O = 1/10$

Temperature: 50°C

T' 200

Time: 300 s

- Thin-film transistors separation

Negative photoresist with thickness of 1  $\mu$ m was deposited over the wafer surface and was patterned using the mask from Fig.2.5.a. The photoresist covered the wafer surface corresponding to the bright areas of the mask, while the surface corresponding to the dark area was unprotected. The unprotected nc-Si:H material was etched by means of dry etching in

37

"Plasmalab" PECVD chamber. Thus, the transistors on the wafer were isolated electrically.

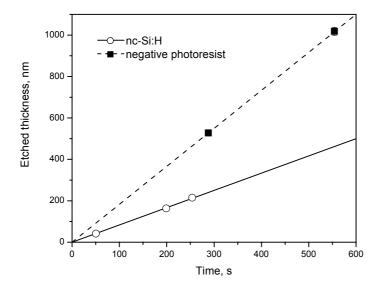

We studied the etching rate (etched thickness per second) of the dry etching for negative photoresist and for nc-Si:H. In Fig.2.6 is presented the experimentally found progress of the etched thickness of both materials using the following etching parameters:

Gas mixture:  $92\% CF_4 + 8\% O_2$

Pressure: 350 mTorr Temperature: 100°C RF power: 200W Time: 300 s

In the dry etching process, the etching rate is inversely proportional

**Figure 2.6.** Experimentally found dry etching rate for nc-Si:H and for negative photoresist layers under the following conditions: temperature 100°C, pressure 350 mTorr, rf power 200 W.

on the conductivity of the etched material. For this reason the less conductive photoresist is etched faster than the nc-Si:H layer. Etching rate of about 1 nm/s for the nc-Si:H and etching rate of about 2 nm/s for the photoresist were estimated from Fig.2.6.

The negative photoresist is etched about two times faster than nc-Si:H. On the other hand, the photoresist (1  $\mu$ m) was 3-4 times thicker than the nc-Si:H layer (250-300 nm). Thus, etching process during 600 s assured complete removing of the unprotected nc-Si:H layer whereas the photoresist was not etched completely. Afterwards, the remaining photoresist layer was removed chemically by standard chemical etching process.

# - Dry etching of the surface n+ doped layer.

Once the negative photoresist was removed, second dry etching process was performed on the entire wafer surface under the same process parameters, as in the previous step except the time. The aim of this etching process was to remove the n+ doped nc-Si:H layer between the drain and source contacts. There is no need of protecting photoresist during this process, as the metal layer is not affected by the plasma etching, i.e. the metal contacts serve as a mask in this case. However, it must be taken into account that thin metal contacts could be damaged if submitted to prolonged plasma etching.

The thickness of the n+ nc-Si:H layer to be etched in this case was about 50 nm. The wafer was submitted to dry etching during 60 s assuming the same etching rate of 1 nm/s for n+ doped nc-Si:H as for intrinsic nc-Si:H. This etching time assured complete removing of the n+ doped layer and 5 to 10 nm thick layer of the intrinsic nc-Si:H. No damage of the metal contacts was noted. The channel thickness of the thin-film transistors can be controlled varying the time of this etching step. Thickness of about 200 nm was adjusted for the devices. It is important to notice that the etching time is the most important parameter in this step, as the thickness to be etched is very small.

39

# - Bottom SiO<sub>2</sub> etching

The final step was the removing of the thermally grown  $SiO_2$  layer on the bottom side of the wafer. The topside of the wafer was previously protected by positive photoresist. We used the same etching process as in the initial  $SiO_2$  photolithography. Finally, the photoresist was removed chemically from the wafer.

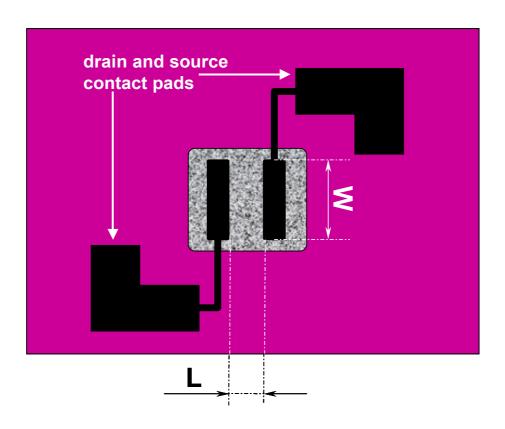

In summary, we used two masks for the photolithography processes – one to define the gates and channels of the TFTs and another one for the metal contacts formation. These masks contained a large variety of planar geometries with channel lengths (L) between 10 and 55  $\mu$ m and widths (W) between 22 and 220  $\mu$ m. Transistors with aspect ratios (W/L) from 2.1 to 22.0 were formed on the wafer. The cross-section and the top-view of the final device with L = 55  $\mu$ m and W = 137  $\mu$ m are presented in Fig.2.7.

Figure 2.7. Cross-section and top view of nc-Si:H thin-film transistor

# 3. Electrical characterisation of the nc-Si:H TFTs

In this chapter the electrical characteristics of the fabricated nc-Si:H TFTs are described. Representative results for the simplified sample and for the finally obtained complete device are shown and discussed.

Initially the transfer ( $I_{DS}$  vs.  $V_{GS}$ ) and the output ( $I_{DS}$  vs.  $V_{DS}$ ) characteristics are analysed. The relation between the basic transistor characteristics and the physical properties of the transistor structure are also

explained. The transfer characteristics allow the evaluation of the channel material properties and the influence of the geometry on the transistor operation. The output characteristics are used to evaluate the contact zones quality.

Furthermore, the behaviour of the devices in saturation regime is presented. Electrical measurements of the saturation drain-source current permit the field-effect mobility and the threshold voltage to be calculated.

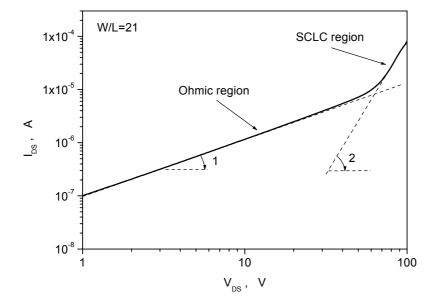

Finally, the measurements the thermally activated currents and the space-charge limited current are used as tools for the analysis of the Fermi level position and the density of defect states in nc-Si:H [67, 68].

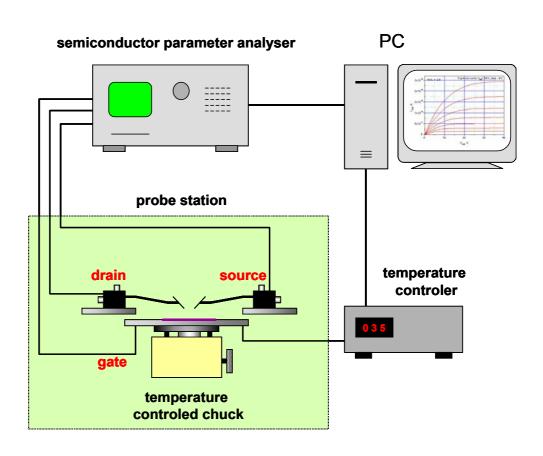

The measurements presented in this chapter were performed using HP4145B Semiconductor Parameter Analyser, Karl Suss PM5 probe station with temperature controlled chuck and MMR Technologies K20 temperature controller. The experimental set-up is presented in Fig.3.1.

The initial electrical characterization of the TFTs was realised in the Characterization Laboratory of DEE, UPC, Barcelona including measurements of transfer and output characteristics, threshold voltage, field-effect mobility and activation energy. Later, the measurements were repeated in the Laboratory for Electrical Characterisation, DEEEA, URV, Tarragona, and completed with measurements of SCLC currents and analysis of the density of defect states.

# 3.1. Basic characterization

The performance of the nc-Si:H TFTs may be characterized by several parameters such as on/off ratio, field-effect mobility  $\mu_{fet}$ , and threshold voltage  $V_T$ . In general, the  $\mu_{fet}$  value of non-crystalline silicon TFTs is much lower than that of a crystalline silicon MOS transistor. Therefore, the aspect ratio W/L of the devices must be large in order to obtain reasonable levels of the drain-source current (in the range of 1  $\mu$ A). Low value of  $V_T$  (several volts) is necessary in order to assure the TFTs compatibility with conventional CMOS ICs.

**Figure 3.1.** Experimental set-up for electrical characterisation of the TFTs.

# 3.1.1. Transfer characteristics

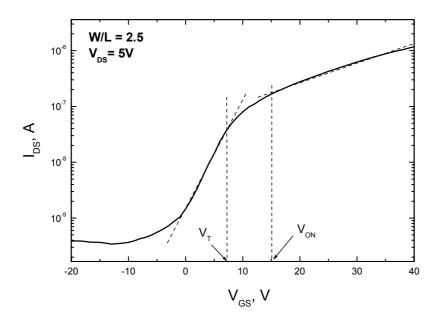

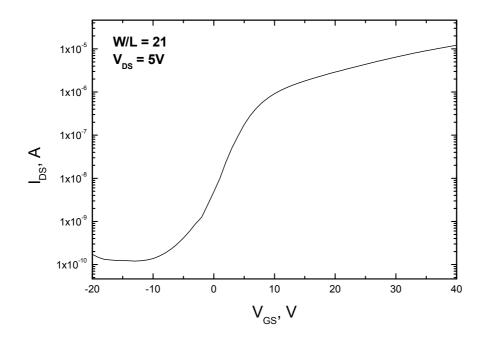

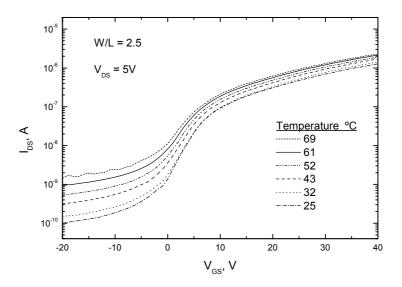

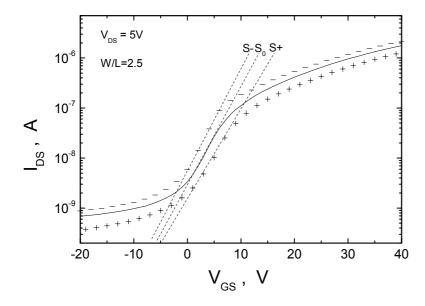

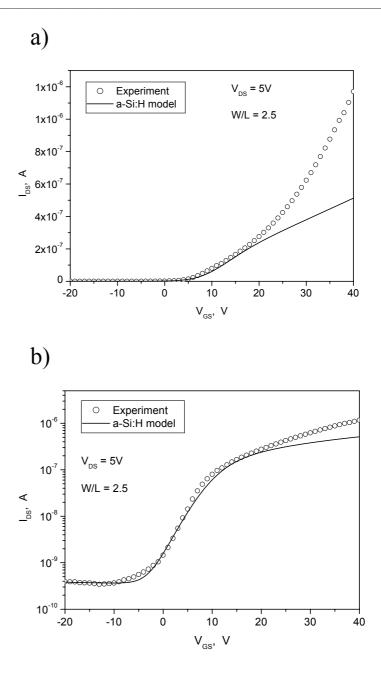

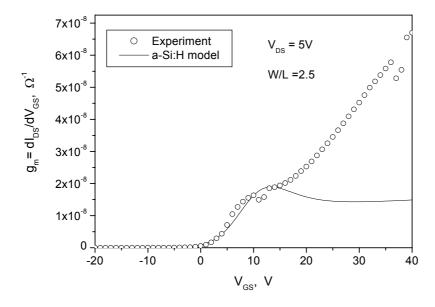

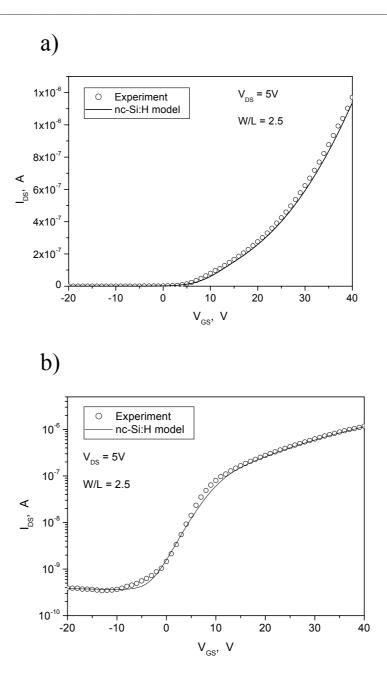

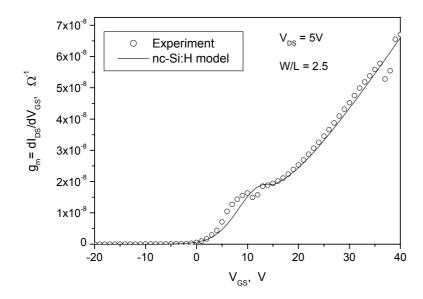

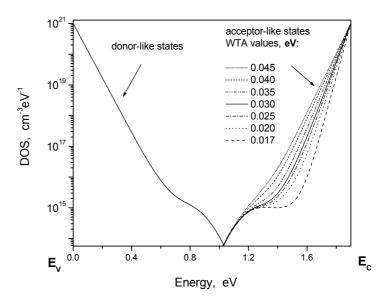

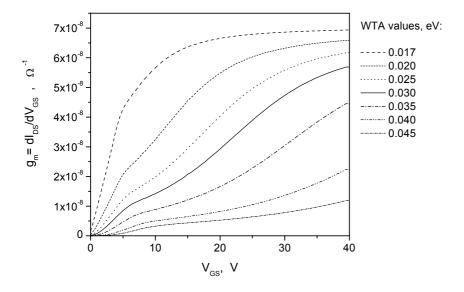

The measured transfer characteristic of nc-Si:H TFT with length L=55  $\mu m$  and width W=137  $\mu m$  (aspect ratio W/L=2.5) is presented in Fig.3.2. Between the drain and source contacts is applied voltage  $V_{DS}$  of 5 V at which the drain-source current  $I_{DS}$  is linear in  $V_{DS}$ . The gate-source voltage  $V_{GS}$  varies from –20 V to +40 V.

When  $V_{GS}$  increases from 0 towards positive values, electrons are accumulated near the gate – channel interface. This leads to an exponential increasing of the drain-source current  $I_{DS}$  that corresponds to the subthreshold regime. This exponential shape continues until  $V_{GS}$  about 7-8  $V_{GS}$  between 8 and 15  $V_{GS}$ , it can be observed the knee shape of the

**Figure 3.2.** Transfer characteristic (solid line) of nc-Si:H TFT with n+contact layer, aspect ratio W/L = 2.5, measured at room temperature. Eye guidelines (dashed lines) are plotted for better clarity.

transfer characteristic. The current increasing becomes slower than exponential and an on-current  $I_{DSon}$  of about 1  $\mu A$  is reached for  $V_{GS}$  above 35 V.

In Fig.3.2 can be seen that there is a difference between the threshold voltage  $V_T$  and the ON voltage  $V_{ON}$ . Similar effect was reported for a-Si:H and poly-Si TFTs [39, 40] as commented in Section 1.2. The knee region of transition from exponential to linear increasing of  $I_{DS}$  is much more gradual than in crystalline transistors due to the bandgap states, and  $V_{ON} > V_T$ .

From the transfer characteristic,  $V_T$  can be estimated at the beginning of the knee corresponding in this case to a  $V_{GS}$  value of about 8 V. On the other hand,  $V_{ON}$  is at the end of the knee – at  $V_{GS}$  about 13-15 V.

One can note that the increasing of the drain-source current is not purely linear for  $V_{GS}$  higher than  $V_{ON}$ , although it is expected a linear increasing for a-Si:H TFTs. Detailed analysis of this effect can be found in Chapter 5.

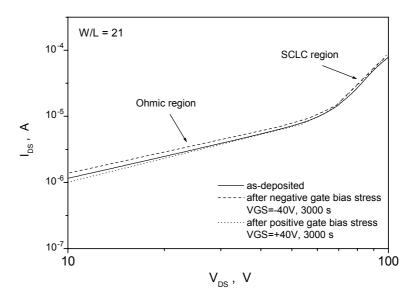

### - Discussion

When negative  $V_{GS}$  is applied, the concentration of the electrons near the gate decreases. The drain-source current declines down to 0.3 nA at  $V_{GS}$  = -12 V (Fig.3.2). Nearly constant off-current  $I_{DSoff}$  of 0.3-0.4 nA is reached at further negative increasing of  $V_{GS}$ . The on/off ratio for  $I_{DSon}$  at  $V_{GS}$ =20 V and  $I_{DSoff}$  at  $V_{GS}$ =-15 V gets to 3 orders of magnitude. At  $V_{GS}$  = 35-40 V the ratio  $I_{DSon}/I_{DSoff}$  is almost 4 orders of magnitude. These values are lower than the on/off ratio typical for a-Si:H TFTs (about 6 orders of magnitude). We believe that this can be attributed to relatively high levels of  $I_{DSoff}$  due to the higher conductivity of the nc-Si:H with respect to a-Si:H. In our case the dark conductivity  $\sigma_{dark}$  of the nc-Si:H is about  $10^{-6} \ \Omega^{-1} \text{cm}^{-1}$  that is several orders of magnitude higher than the typical  $\sigma_{dark}$  for undoped a-Si:H ( $\sigma_{dark} \approx 10^{-11} \ \Omega^{-1} \text{cm}^{-1}$  [1]).

**Figure 3.3.** Transfer characteristic of nc-Si:H TFT, with n+ contact layer, with aspect ratio W/L = 21, measured at room temperature.

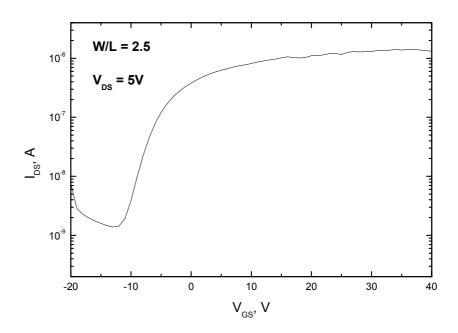

# - Influence of the aspect ratio W/L

With the aim to study the effect of the aspect ratio W/L on the transfer characteristics, measurements of transistors with W/L values between 2.5 and 22 were performed. In Fig.3.3 is presented the transfer characteristic of nc-Si:H TFT with channel width W=220  $\mu$ m and length L=10  $\mu$ m (W/L = 22). It can be observed that  $I_{DSon}$  of about 10  $\mu$ A is achieved at  $V_{GS}$  = 35 V.

The off–current is about 0.1-0.2 nA for  $V_{GS}$ =-15 V that is approximately the same value as in the transfer characteristics for W/L=2.5 in Fig.3.2. The  $I_{DSon}/I_{DSoff}$  ratio increases about one order of magnitude for W/L=22 with respect to W/L=2.5 due to the increasing of  $I_{DSon}$ . Therefore, in

**Figure 3.4.** Transfer characteristic of nc-Si:H TFT with simplified structure (without n+ doped layer), aspect ratio W/L=2.5, measured at room temperature.

our case the device geometry can be used to optimise the electrical characteristics of the TFTs.

### - Influence of the n+ doped contact layer

It should be mentioned the importance of the n+ doped contact layers incorporated in the drain and source contacts of the complete device.

In Fig.3.4 is presented the transfer characteristic of TFT with simplified structure (without n+ doped layer). The minimal off-current is about 20 nA and is achieved at  $V_{GS}$ = -13 V. At further increasing of the gate voltage towards negative values, holes are accumulated near the gate insulator and as a result the off-current  $I_{DSoff}$  begins to increase. This effect

leads to a dramatic decreasing of the on/off ratio. On the contrary, when n+ layers are incorporated in the drain and source contacts, they block the hole-assisted current and avoid the increasing of I<sub>DSoff</sub>.

### - Subthreshold slope

The exponential transition between the ON and OFF states in nc-Si:H TFTs can be used to determine the density of states. The inverse of the subthreshold slope of the transfer characteristics, defined as:

$$S = \frac{dV_{GS}}{d\log(I_{DS})} \tag{3.1}$$

can give information about the density of states (DOS) in the bulk of the channel material (*bulk states*) and at the interface between the channel material and the gate insulator (*interface states*) [41, 69]. The subthreshold slope could be affected also by states corresponding to defects at the channel surface (*surface states*). It is found that the surface states can have the same effect on the subthreshold slope as the interface states [41].

Assuming that the densities of deep bulk states  $N_{bs}$  and interface states  $N_{ss}$  are independent on the energy, the subthreshold slope is linked to  $N_{bs}$  and  $N_{ss}$  by the following equation [41]:

$$S = \frac{k_B T}{q \cdot \log_{10}(e)} \left[ 1 + \frac{q x_i}{\varepsilon_i} \cdot \left( \sqrt{\varepsilon_s N_{bs}} + q N_{ss} \right) \right]$$

(3.2)

where  $\varepsilon_i = 3.9 \cdot \varepsilon_0$  and  $\varepsilon_s = 11.8 \cdot \varepsilon_0$  are dielectric constants of the insulator and semiconductor, respectively ( $\varepsilon_s$  was chosen as in a-Si:H [50]),  $x_i = 220$  nm is the insulator thickness, q is the absolute value of the electron charge,  $k_B$  is the Boltzmann constant, and T = 298 K is the absolute temperature.

Eq. (3.1) does not permit the  $N_{bs}$  and  $N_{ss}$  to be determined separately but it can be used to set their upper limits  $(N_{bs})_{max}$  and  $(N_{ss})_{max}$  by assuming

$N_{ss}$ =0 and  $N_{bs}$ =0, respectively. From the transfer characteristic on Fig.3.2 we determined  $(N_{bs})_{max} = 3.6 \cdot 10^{18}$  cm<sup>-3</sup>eV<sup>-1</sup> and  $(N_{ss})_{max} = 4.9 \cdot 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>. These values are typical for highly disordered materials like a-Si:H. They indicate that the amorphous–like grain boundaries in the nc-Si:H material and defect states near the nc-Si:H/SiO<sub>2</sub> interface are responsible for the performance of the TFT in the subthreshold region.

From the subthreshold slope of the simplified TFTs without n+contact layer (Fig.3.4), we determined  $(N_{bs})_{max}$ = 1.6·10<sup>18</sup> cm<sup>-3</sup>eV<sup>-1</sup> and  $(N_{ss})_{max}$ = 3.2·10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup>. These values of the density of states are lower when compared to the samples with incorporated n+ layer.

One possible reason for this difference is the creation of surface states during the dry etching process involved in the fabrication of the complete device (with n+ contact layer). Such an effect was extensively discussed in the literature [70-72]. Usually, problems due to surface defects are solved by deposition of silicon nitride as a passivating layer on the channel surface [73].

Other possible reason for the differences in the DOS could be the lower density of the bulk states in the nc-Si:H of the simplified sample with respect to the nc-Si:H of the complete sample. In other words, this mean nc-Si:H with different properties in both cases. The origin of such difference would be in the HWCVD deposition process. Nevertheless, we do not dispose of enough evidences supporting this explanation.

The uncertainty in the interpretation of the subthreshold slope arises from the fact that as a method for evaluation of DOS it does not allow separated extraction of the bulk states from the interface and/or surface states. It gives only a rough evaluation of the maximal possible values of the DOS. Therefore, more detailed analysis of the density of states based on other measurement techniques was performed in Section 3.2.

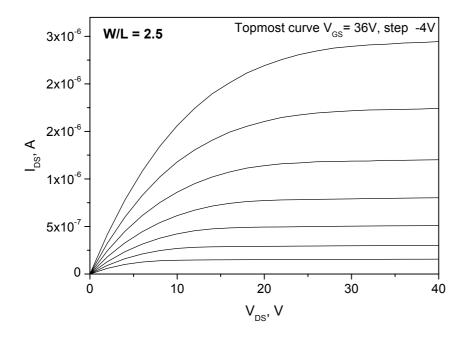

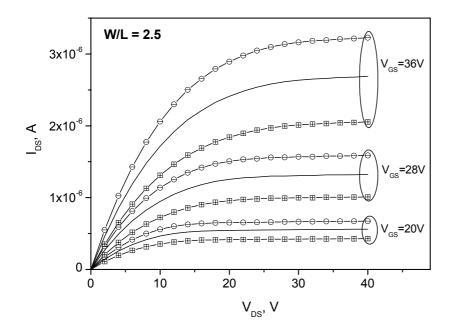

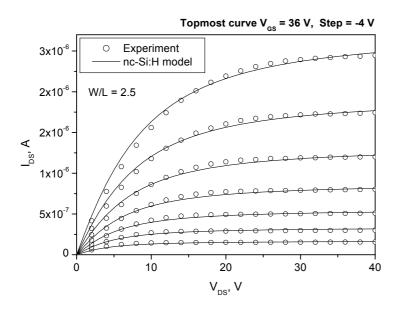

# 3.1.2. Output characteristics

In Fig.3.5 are presented the output characteristics of the nc-Si:H TFT with W/L=2.5. We applied drain-source voltage  $V_{DS}$  from 0 to 40 V and gate – source voltages  $V_{GS}$  from 12 to 36 V (higher than the threshold voltage) with a step of 4 V. At positive gate voltage above  $V_T$ , electrons are induced near the gate insulator and conduction channel is created close to the nc-Si:H/SiO<sub>2</sub> interface. The application of drain-source voltage provokes linear increasing of  $I_{DS}$  at low  $V_{DS}$ , followed by saturation at high  $V_{DS}$ . The saturation values of  $I_{DS}$  depend on the thickness of the induced channel. At small gate voltages, the channel thickness is small and the saturation values of  $I_{DS}$  are low, whereas at high gate voltages the channel thickness is large

**Figure 3.5.** Output characteristics of nc-Si:H TFT with n+ contact layer, with W/L=2.5, measured at room temperature.

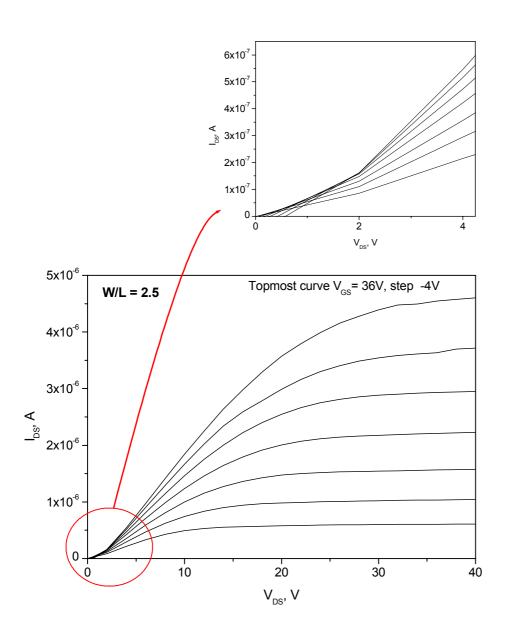

and the saturation values of  $I_{DS}$  are higher. Thus, for instance,  $I_{DS}$  increases linearly up to  $1.4\cdot10^{-7}$  A for  $V_{GS}$ =12 V and  $V_{DS}$  below 6-7 V. For higher  $V_{DS}$ ,  $I_{DS}$  stays at nearly constant level of  $(1.4\text{-}1.5)\cdot10^{-7}$  A. For  $V_{GS}$ =36 V,  $I_{DS}$  increases until  $2.5\cdot10^{-6}$  A for  $V_{DS}$  below 25 V. For higher  $V_{DS}$ ,  $I_{DS}$  saturates at  $(2.6\text{-}2.6)\cdot10^{-6}$  A. In Fig.3.5 can be clearly distinguished the linear and the saturation regimes for each curve. Good saturation for each gate voltage is observed. We should notice that there is not current crowding at small values of  $V_{DS}$  revealing the absence of contact resistance at the drain and source contacts. The incorporated n+ layers contribute to the formation of good ohmic contacts at the drain and source.

An illustration of the role of the n+ layers is given in Fig.3.6 where are presented the output characteristics of the TFTs with simplified structure (without n+ layer). We can clearly note that the curves corresponding to different gate voltages are crowded at low drain-source voltages. This indicates that relatively high resistive contacts are present in the drain and source areas. This negative effect confirms the importance of the n+ doped contact layers.

We do not observe Kink effect (undesirable increasing of  $I_{DS}$  at high drain-source voltages [51]) in the output characteristics in Fig.3.5. This indicates that there is not electron injection at the drain and source contacts. Kink effect is present in poly-Si TFTs but is not typical for a-Si:H TFTs [39]. The absence of Kink effect in the nc-Si:H TFTs makes their behaviour more similar to a-Si:H TFTs than to poly-Si TFTs.

**Figure 3.6.** Output characteristics of nc-Si:H TFT with simplified structure (without n+ contact layer), W/L=2.5.

# 3.1.3. Saturation regime - threshold voltage and field-effect mobility

In a-Si:H and poly-Si TFTs, the threshold voltage and the field-effect mobility are experimentally determined from measurements of the saturation drain-source current using the same saturation condition as in conventional MOSFETs. According to the theory of the MOSFETs, the transistor enters in saturation regime when  $V_{DS}$  is grater than  $V_{SAT} = V_{GS}$ - $V_{T}$  [51]. This condition is accomplished when  $V_{DS} = V_{GS}$ . The following equations for the drain-source current are valid in saturation regime:

$$I_{DS} = \frac{W}{L} \mu_{fet} C_{ox} \frac{1}{2} (V_{GS} - V_T)^2$$

(3.3)

$$C_{ox} = \varepsilon_0 \varepsilon_i \cdot \frac{t_{ox} \cdot W}{L} \tag{3.4}$$

where  $\mu_{fet}$  is the field effect mobility,  $C_{ox}$  is the gate oxide capacitance,  $\varepsilon_0$  is the vacuum permittivity,  $\varepsilon_i$ =3.9 is the gate oxide relative dielectric permittivity,  $t_{ox}$  = 220 nm is the gate oxide thickness, W=125  $\mu$ m is the channel width and L=50  $\mu$ m is the channel length.

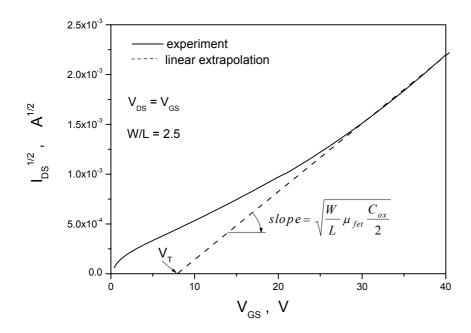

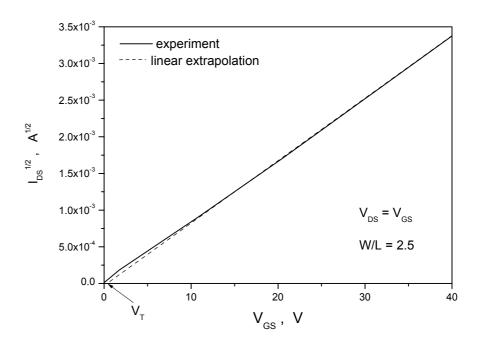

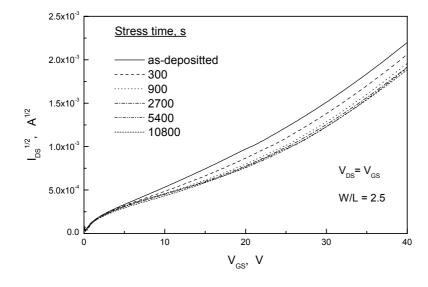

Using these equations one can determine experimentally  $\mu_{fet}$  and  $V_T$  from the plot of the square root of  $I_{DS}$  measured at  $V_{GS} = V_{DS}$  (Fig.3.7). Linear regression is plotted for  $V_{GS}$  from 30 to 40 V (the upper part of the curve). From the intercept with the horizontal axis,  $V_T$  about 8 V was determined that is in agreement with the value determined from the transfer characteristic. From the slope of the linear regression,  $\mu_{fet} = 0.45 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  was calculated. The threshold voltage is higher and the field-effect mobility is lower when compared to the TFTs without n+ layer (Fig.3.8). It has threshold voltage of about 0.1 V and field effect mobility of 0.70 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. These values are in agreement with the lower density of states that was calculated for this sample from its subthreshold slope (Section 3.1.1). As it

**Figure 3.7.** Square root of  $I_{DS}$  in saturation regime (at  $V_{DS}=V_{GS}$ ) for transistor with n+ contact layers.

was mentioned, these differences between the samples could be due to interface or surface states as well as due to bulk states.

In summary, the basic characteristics (ON current values, field-effect mobility, subthreshold slope and threshold voltage) of the nc-Si:H TFTs presented in this thesis are very similar to those of a-Si:H TFTs. This behaviour can be attributed to the amorphous-like zones between the crystalline grains in the nc-Si:H material. Elevated density of defect states in these zones is responsible for the relatively low value of  $\mu_{fet}$  that has typical values for a-Si:H material. Detailed analysis of the density of defect states is performed in Section 3.2.2. On the other hand, the measured OFF current shows higher values when compared with a-Si:H TFTs because of the higher conductivity of the nc-Si:H layer. The incorporation of n+ doped layer in the drain and source contact zones leads to a significant improvement of the

**Figure 3.8.** Square root of  $I_{DS}$  in saturation regime ( $V_{GS}=V_{DS}$ ) of transistor with simplified structure (without n+ contact layer).

basic TFTs characteristics such as low OFF current level, high on/off ratio. In addition, the n+ layer improves the drain and source ohmic contacts and assures output characteristics without current crowding. On the other hand, an increasing of the threshold voltage and slight decreasing of the field effect mobility was observed in the samples with n+ layer. However, the aim of this work is not to improve the device characteristics but it is to study the physical mechanisms that are responsible for the device behaviour.

# 3.2. Advanced electrical characterization

# 3.2.1. Activation energy measurements

When gate voltage is applied in field effect structures, positive gate voltages provoke accumulation of electrons near the gate/channel interface. The induced electrons fill the available states above the Fermi level and, as a consequence, it is shifted towards higher energy (towards the conduction band  $E_C$ ). Negative gate voltages provoke emission of electrons from the states below the Fermi level and consecutive Fermi level shift towards lower energy levels (towards the valence band  $E_V$ ).

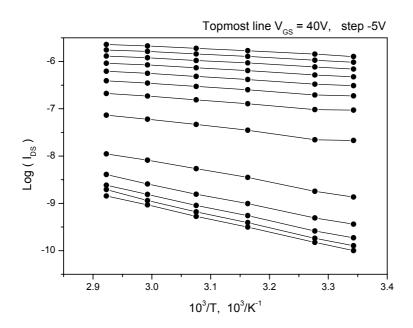

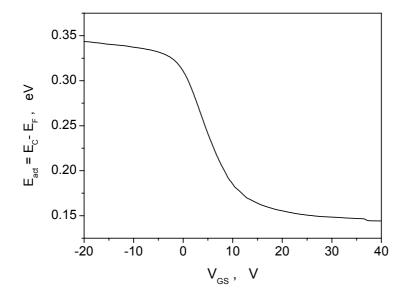

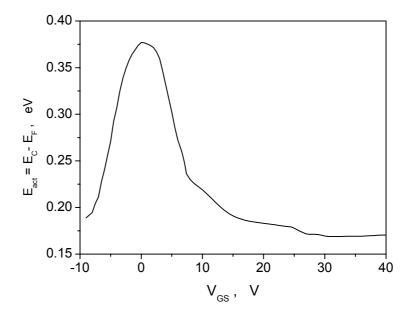

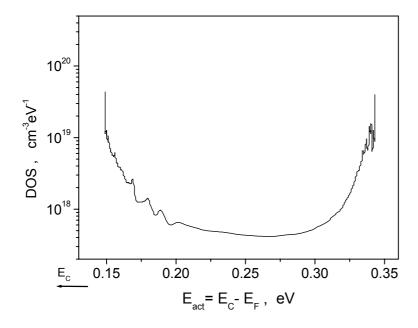

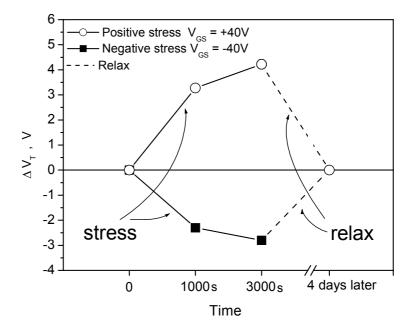

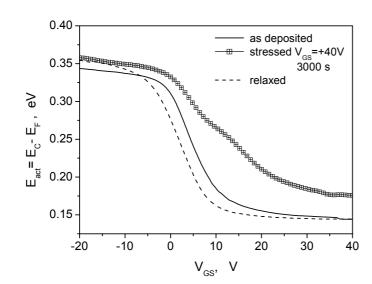

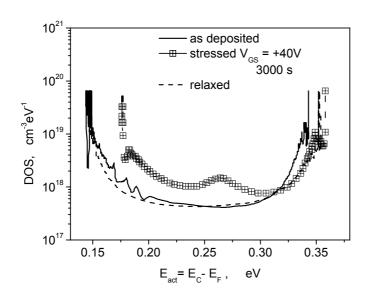

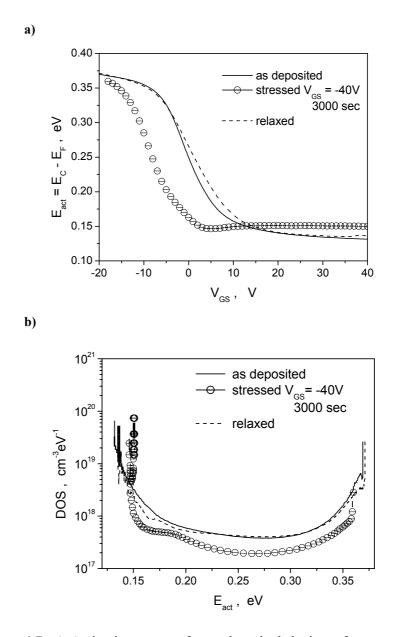

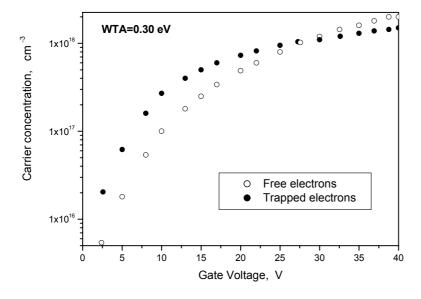

The n-channel TFTs enter in ON state when Fermi level  $E_F$  is close enough to the conduction band  $E_C$  and conduction electrons are induced in the channel. The rate at which  $E_F$  moves towards the conduction band (in n-channel devices) depends on the density of states located in the band gap and on the distribution of tail states close to the conduction band. Detailed knowledge of the Fermi level shift allows the electronic properties of the material to be studied. For small values of  $V_{GS}$ , the Fermi level is located in deep states. Increasing  $V_{GS}$  leads to a shift of the Fermi level towards the conduction band, and the tail band states become important.