ADVERTIMENT. L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús establertes per la següent llicència Creative Commons: http://cat.creativecommons.org/?page\_id=184

**ADVERTENCIA.** El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons: http://es.creativecommons.org/blog/licencias/

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: https://creativecommons.org/licenses/?lang=en

Design, fabrication and characterization of semiconductor radiation sensors for future high energy physics experiments

## UNIVERSITAT AUTÒNOMA DE BARCELONA Departament de Enginyeria Electrònica

# INSTITUTO DE MICROELECTRÓNICA DE BARCELONA - CENTRO NACIONAL DE MICROELECTRÓNICA (IMB - CNM)

### Design, fabrication and characterization of semiconductor radiation sensors for future high energy physics experiments

Memoria presentada para optar al título de Doctor ene Ingeniería Electrónica y Telecomunicación

Autor: Víctor Hugo Benítez Casma

Director de Tesis: Miguel Ullán Comes

Tutor de Tesis: David Jiménez Jiménez

#### **CERTIFICAN:**

que la memoria "Design, fabrication and characterization of semiconductor radiation sensors for future high energy physics experiments" que presenta Víctor Hugo Benítez Casma para optar al grado de Doctor en Ingeniería Electrónica y Telecomunicación se ha realizado bajo su dirección en el Instituto de Microelectrónica de Barcelona del Consejo Superior de Investigaciones Científicas y tutoría en el Departamento de Ingeniería Electrónica de la Universidad Autónoma de Barcelona.

Barcelona, septiembre de 2018.

Víctor Hugo Benítez Casma Miguel Ullán Comes

David Jiménez Jiménez

PhD Thesis

# Design, fabrication and characterization of semiconductor radiation sensors for future high energy physics experiments

Author: Víctor Hugo Benítez Casma

#### Director:

Dr. Miguel Ullán Comes Instituto de Microelectrónica de Barcelona - Centro Nacional de Microelectrónica (IMB-CNM)

#### Tutor:

Dr. David Jiménez Jiménez Universitat Autònoma de Barcelona (UAB)

PhD program in Electronic and Telecommunication Engineering

Department of Electronic Engineering - Engineering Faculty

September 2018

#### Acknowledgements

First, I would like to thank Miguel Ullan for the opportunity to work in the Radiation Detectors group at IMB-CNM Barcelona, the almost unlimited patience and continue support through this work and its publication has been decisive to complete this work. Thanks to all the members of the Radiation Detectors group, for all the constructive and interesting discussions and research experience exchange.

Thanks to the colleagues at IMB-CNM in Barcelona for their support inside and outside the cleanroom, in particular to David Quirion for all the time spend together in the cleanroom and his patience to share his knowledge about semiconductor fabrication. Many thanks to the colleagues in the Physics Institute at Freiburg University for their time and friendly welcome, in particular to Ulrich Parzefall and Susanne Kuehn for the opportunity to work in the research group during four months. Thanks also to the colleagues at the Valencia University, in particular to Carlos Lacasta and Urmila Soldevilla for their work. I would also like to thank all the colleagues and friends in Barcelona for those wonderful moments and experiences during five years.

Thanks to all the staff at Santa Cruz Institute of Particle Physics in California, in particular to Vitaliy Fadeyev and Harmut Sadrozinski, for the opportunity to work in the group and their constant feedback. Thanks also to Zach for all the support with the measurements and all the students in the laboratory for their work. Many thanks to Ingrid, Dennis, Pia and all the friends met during those three months in Santa Cruz.

Moltes gràcies al personal del IMB-CNM. Gracies al Sergi per l'ajuda amb la taula semiautomàtica de mesures, a la Marta pel forn i les neteges d'oblea, a la Roser per deixar-me el microscopi a sala blanca per fer fotos, a tots i totes, per permeteu-me veure i explicar-me com s'oxida, seca, implanta, decapa, metal·litza i curta una oblea de silici. Moltes gràcies els meus companys de màster i grup de recerca Marta, Sergi i Mar, m'alegro molt bé haver-nos trobat en dues etapes distintes i comuns a les nostres vides. Gràcies als companys Xavi, Jordi i Anna per als primers consells a l'arribar a la UAB. També gràcies a Larissa, Irune, Mirana i tots els companys a les classes de català pels primers mesos a Barcelona i l'amistat que encara tenim, als companys de pis a Cerdanyola del Vallès i tots a tot arreu de Catalunya per les experiències viscudes.

Danke schön an den Kollegen in der Physikalischen Institutes der Universität Freiburg. Vielen Dank noch mal Ulrich und Susanne, für die Unterstützung und Freundschaft von dem ersten bis letzten Tag in Freiburg. Grazie Mile Riccardo für deine Zeit mit den Messungen und deine Freundschaft. Danke schön Ines für deine Hilfe, um die Geräte drin und außer dem Reinraum zu nutzen. Danke sehr Juan Pablo, Chris, Besnik, Manfredi für die Unterhaltungen, Mittagessen und Freundschaft. Danke sehr Pedro, Stef, und alle die Freunde, die meine vier Monate in Freiburg eine sehr entspannend und schöne Erfahrung gemacht haben. Danke auch an den neuen Kollegen und Freunde in Bonn, die über dieses Dokument gefragt haben und neugierig sind. Danke euch für die letzte drei Jahren.

Gracias de nuevo a Miguel por la paciencia y apoyo durante todos estos años. Celeste, David, Virginia, Carlos, Roberto y todos los compañeros de trabajo y amigos a la vez, gracias por las charlas y las experiencias vividas dentro y fuera del CNM. Gracias también Andrés, Jorge, Manuela, Alicia, Elkin, Ismael, Arantxa, Jean Carlos y todos amigos en Barcelona, con quienes compartimos comidas, cervezas, excursiones y buenos momentos.

Muchas gracias a mi familia, a quienes dedico esta publicación. Gracias a mi padre Hugo y a mi madre Rosa por el cariño y apoyo permanente durante mi vida y estudios en Perú. Muchas gracias a mi hermana Celinda por el cariño y la confianza constante y por la oportunidad de salir de mi país para seguir mi primer master, sin esa oportunidad, no hubiese sido posible todo esto. Gracias a mis hermanos Patricia y Omar por el cariño y apoyo a lo largo de mi vida. Gracias a mis sobrinos Amy, Caleb, Rosa y Caterina, por ser la alegría de la familia.

Gracias a Laura, por comprender cuando tuve que quedarme en el laboratorio hasta tarde, cuando viajaba a Barcelona para hacer medidas mientras estábamos en Alemania, por estar a mi lado dando ánimos cuando parecía que no terminaba esta tesis, por todos los años juntos.

#### Summary

| Acknowledgements                            |    |

|---------------------------------------------|----|

| Summary                                     | ii |

| Introduction                                | vi |

| Framework: High-energy physics experiment   | 1  |

| 1.1 The LHC and the ATLAS experiment        | 1  |

| 1.1.1 ATLAS                                 | 3  |

| 1.1.2 The Inner Detector                    |    |

| 1.2 The ATLAS Upgrade                       | 6  |

| 1.2.1 The End-cap Upgrade                   | 8  |

| 1.3 The RD50 Collaboration                  | 10 |

| Radiation detectors                         | 13 |

| 2.1 Radiation and units                     | 13 |

| 2.2 Radiation types and sources             | 14 |

| 2.2.1 Natural sources                       | 15 |

| 2.2.2 Artificial sources                    | 16 |

| 2.3 Interaction of radiation with matter    | 18 |

| 2.3.1 lonizing radiation                    | 18 |

| 2.3.2 Detector physics                      | 20 |

| 2.4 Semiconductor radiation detectors       | 21 |

| 2.4.1 Principles of semiconductor detectors | 21 |

| 2.4.2 Detector limits: Radiation damage     | 28 |

| 2.4.3 Systems                               | 31 |

| 2.4.4 Silicon radiation sensor types        | 34 |

| Silicon strip detectors                     | 43 |

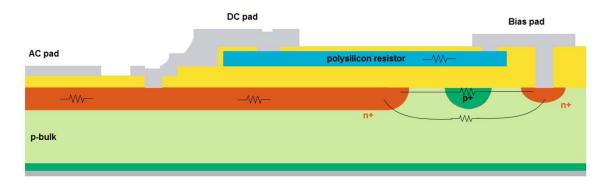

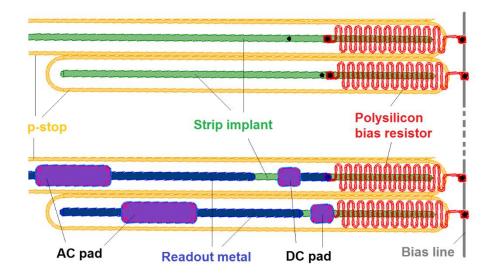

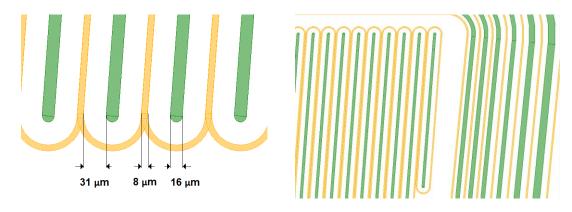

| 3.1 Strip detector characteristics          | 45 |

| 3.1.1 Strip implant                         | 46 |

| 3.1.2 Strip isolation                       | 46 |

| 3.1.3 AC coupling                           | 46 |

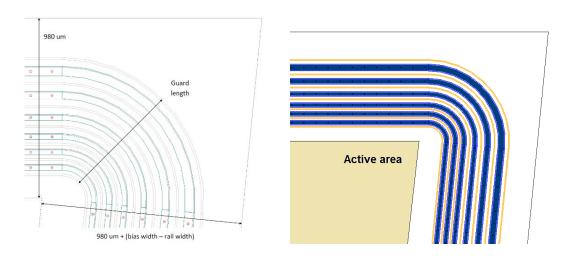

| 3.1.4 Bias rings                            | 48 |

| 3.1.5 Guard rings                           | 49 |

| 3.2 Microelectronic fabrication             | 40 |

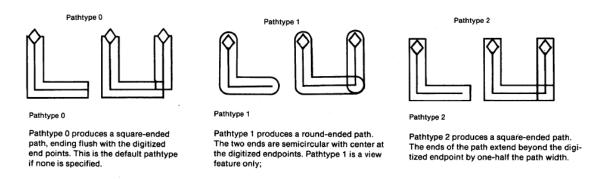

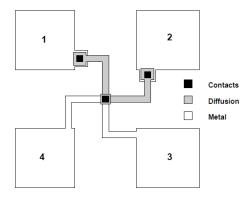

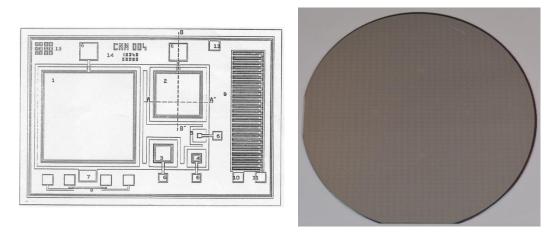

| 3.2.1 Layout design                                  | 50       |

|------------------------------------------------------|----------|

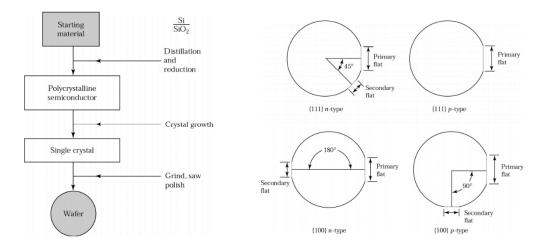

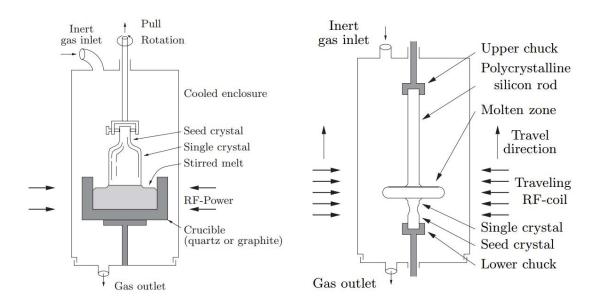

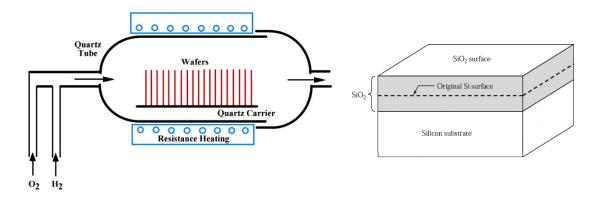

| 3.2.2 Basic Microelectronic fabrication processes    | 52       |

| 3.3 Electrical characteristics                       | 62       |

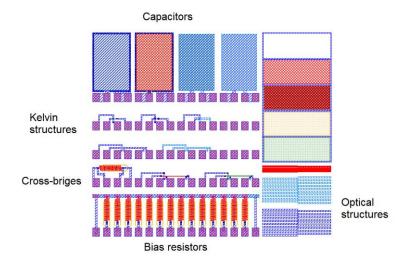

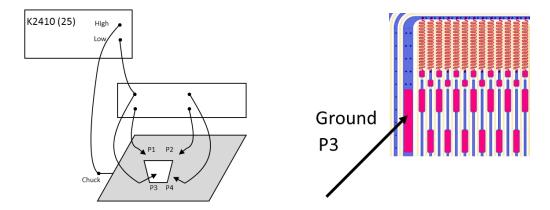

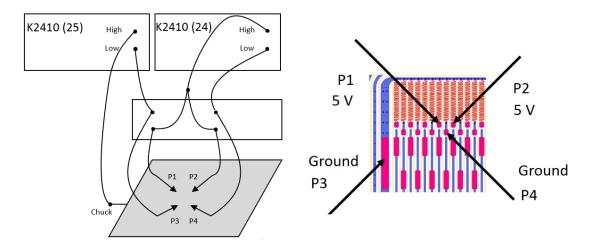

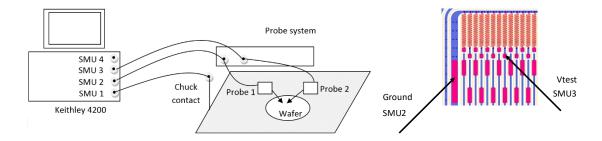

| 3.3.1 Experimental equipment                         | 62       |

| 3.3.2 Technological parameters                       | 65       |

| 3.3.3 Device parameters and characteristics          | 67       |

| Prototypes for the ATLAS experiment Upgrade          | 77       |

| 4.1 End-cap Upgrade sensors                          | 77       |

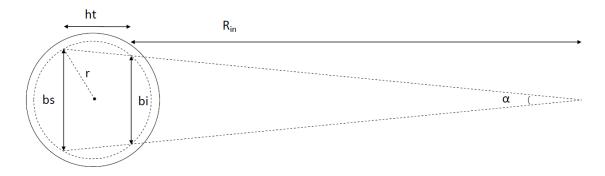

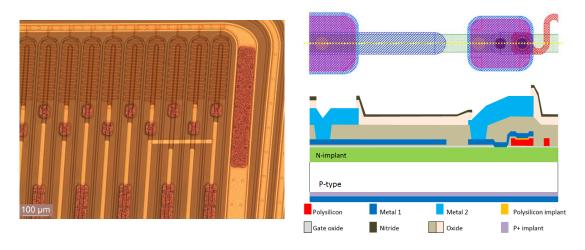

| 4.2 The Petalet prototype                            | 82       |

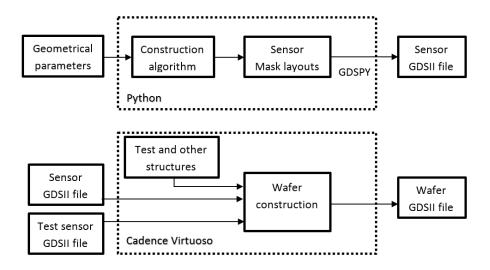

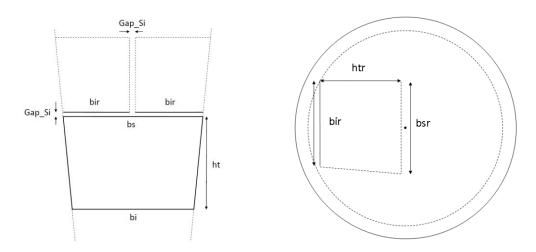

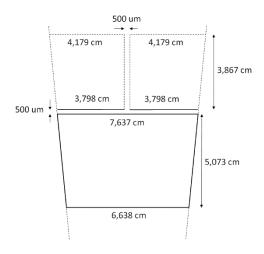

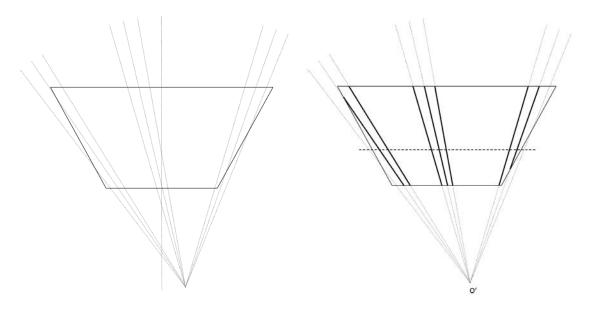

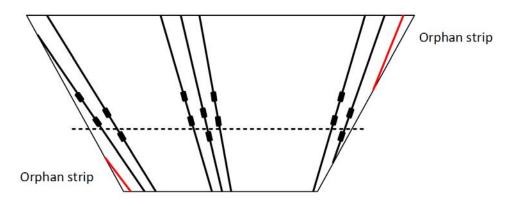

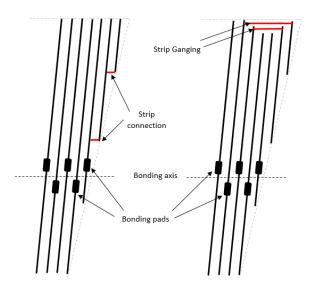

| 4.3 Layout construction                              | 86       |

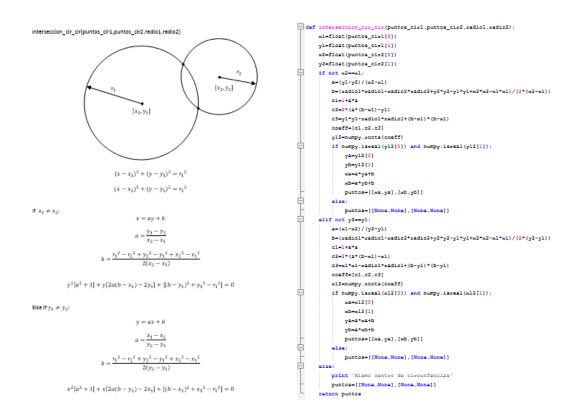

| 4.3.1 Software                                       | 86       |

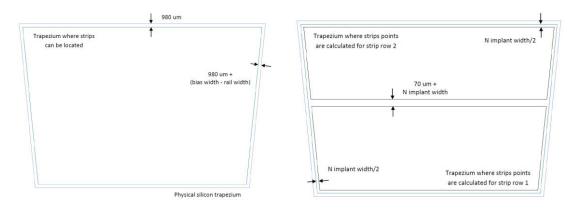

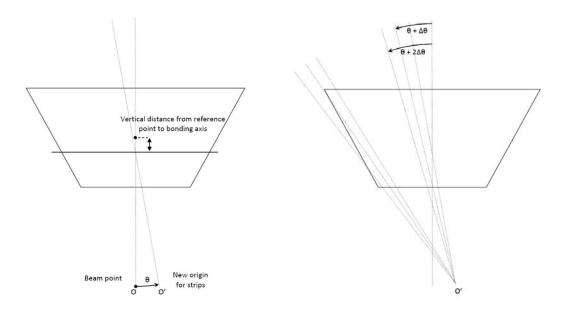

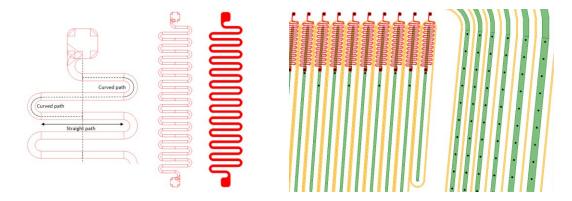

| 4.3.2 Construction algorithm                         | 87       |

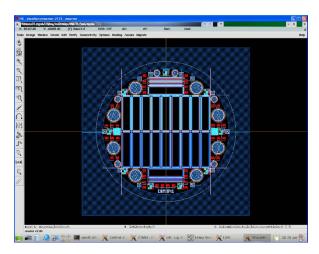

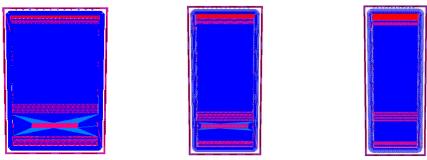

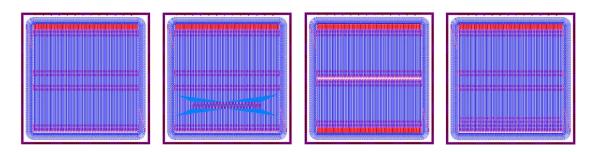

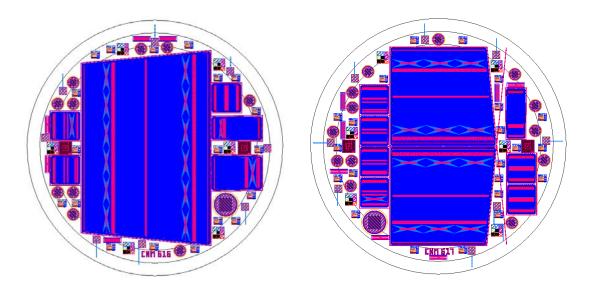

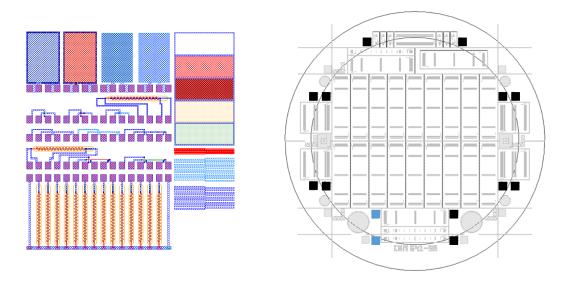

| 4.3.3 Mask layouts                                   | 103      |

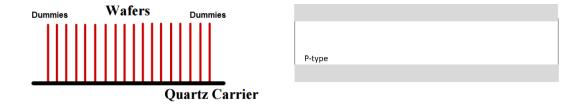

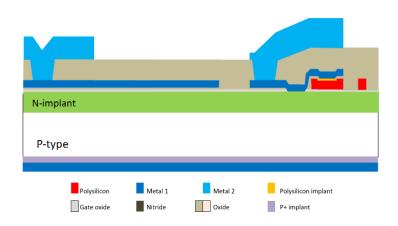

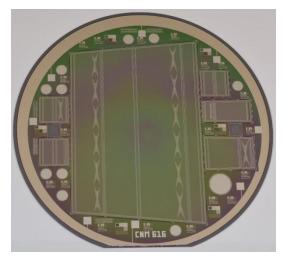

| 4.4 Strip Sensor Fabrication Steps                   | 106      |

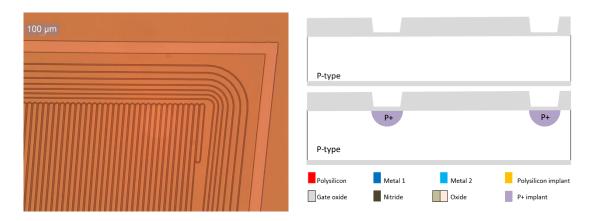

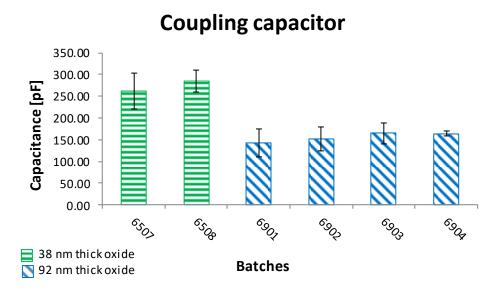

| 4.4.1 Thermal oxidations                             | 107      |

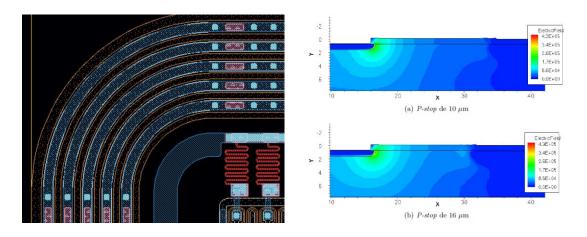

| 4.4.2 P-stops                                        | 107      |

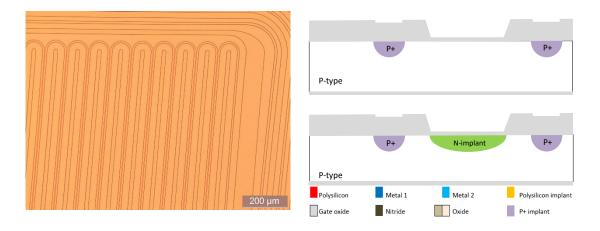

| 4.4.3 Strip implants, coupling oxide and backside im | plant108 |

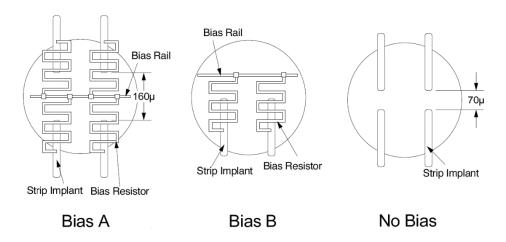

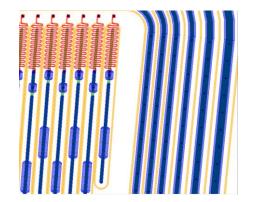

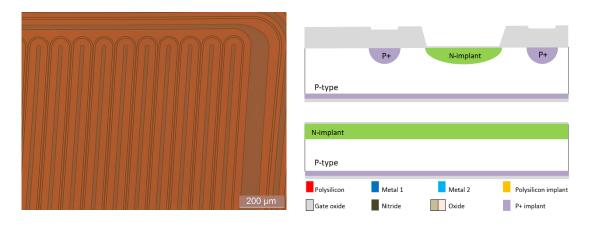

| 4.4.4 Bias resistors                                 | 110      |

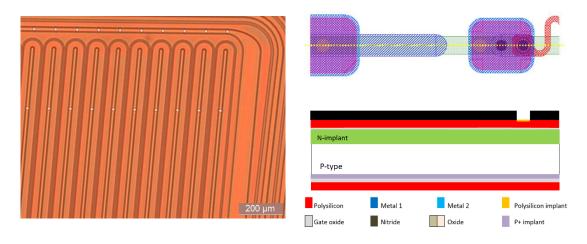

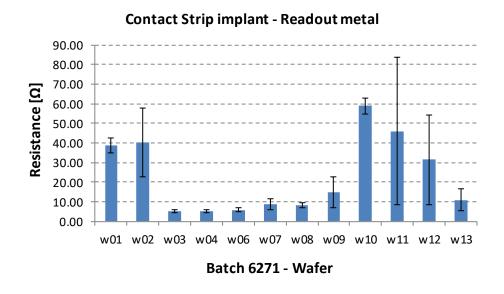

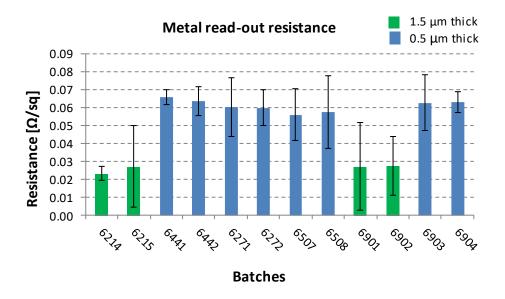

| 4.4.5 Readout metal                                  | 112      |

| 4.4.6 Second metal layer                             | 114      |

| 4.4.7 Backside metal                                 | 116      |

| 4.4.8 Passivation                                    | 117      |

| 4.4.9 Dicing                                         | 118      |

| Low Resistance sensors                               | 121      |

| 5.1 Sensor protection                                | 121      |

| 5.1.1 Effect of beam loses                           | 121      |

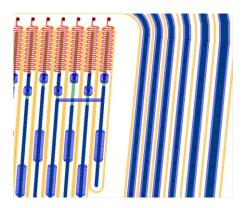

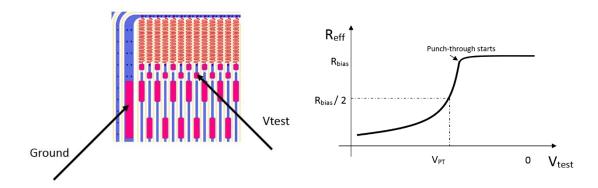

| 5.1.2 Punch-Through protection                       | 122      |

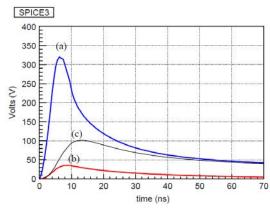

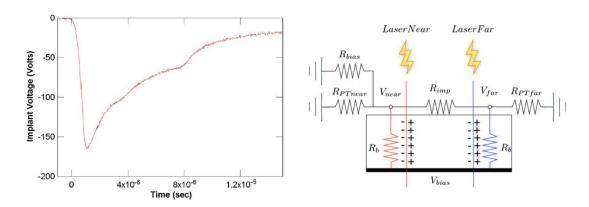

| 5.1.3 Laser scan experiments                         | 126      |

| 5.2 LowR sensors                                     | 127      |

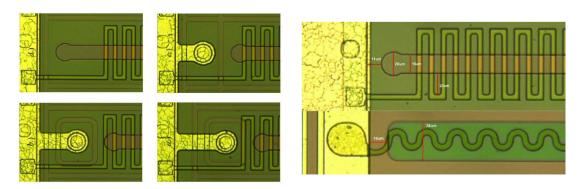

| 5.2.1 Sensor proposal                                | 128      |

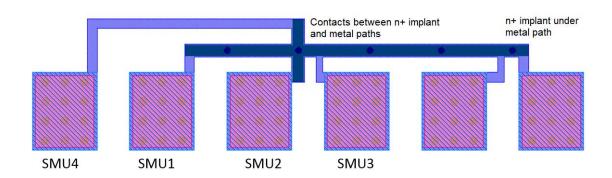

| 5.2.2 Technological challenges                       | 131      |

| 5.2.3 Alternative solutions                          | 135      |

| Experimental results                                 | 141      |

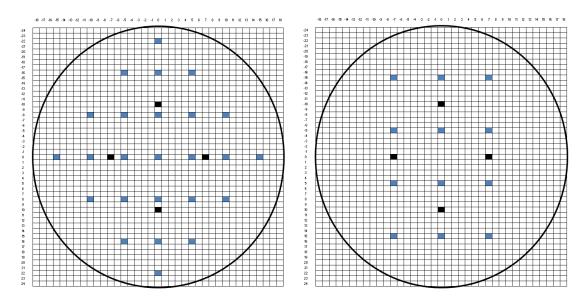

| 6.1 The Petalet Prototyne                            | 141      |

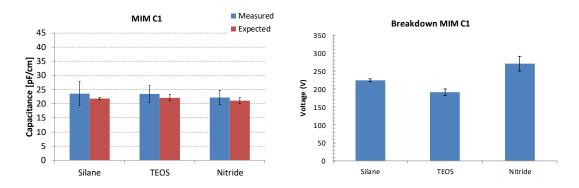

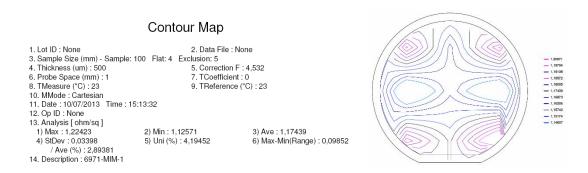

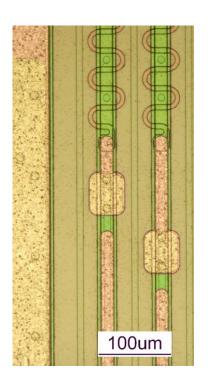

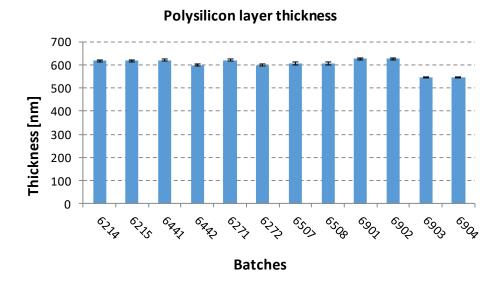

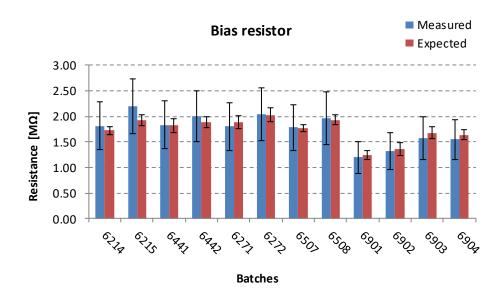

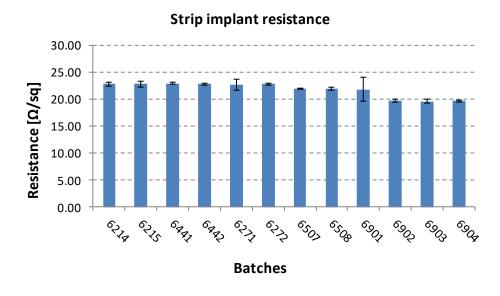

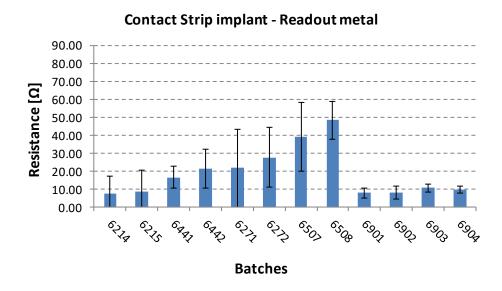

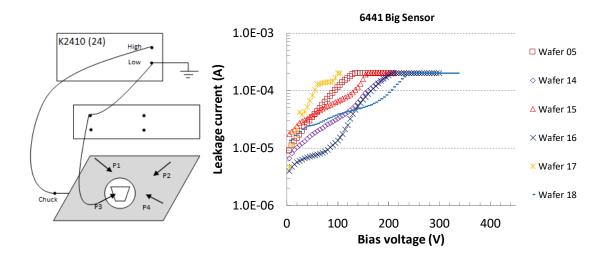

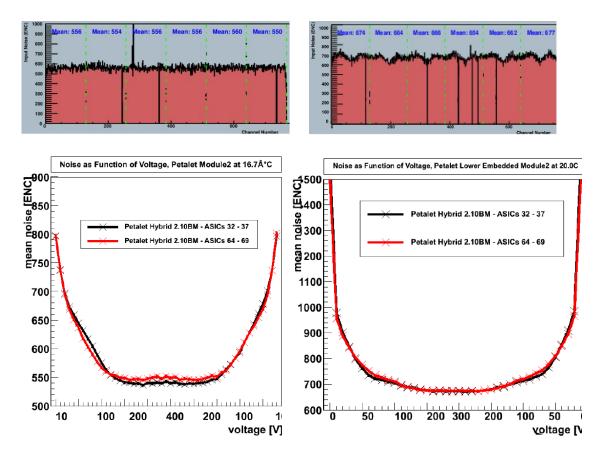

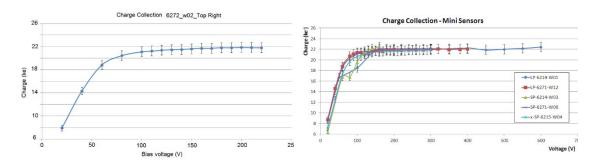

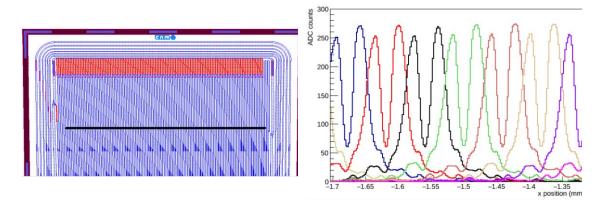

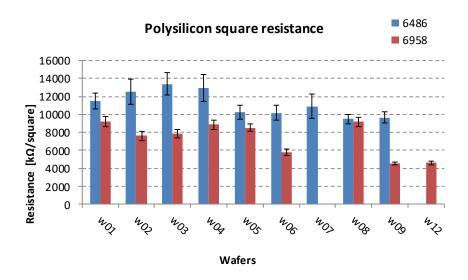

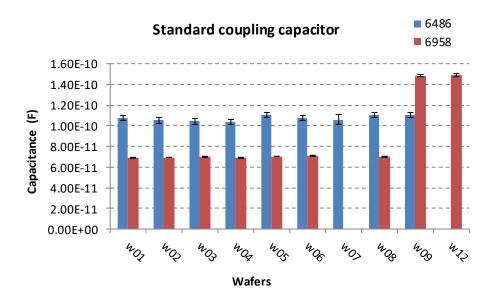

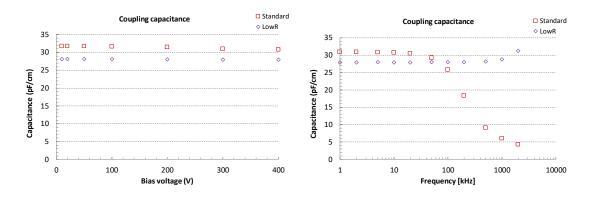

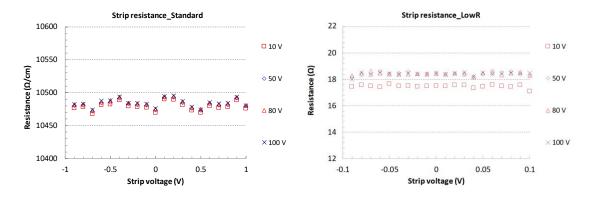

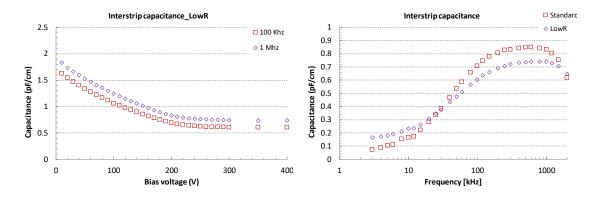

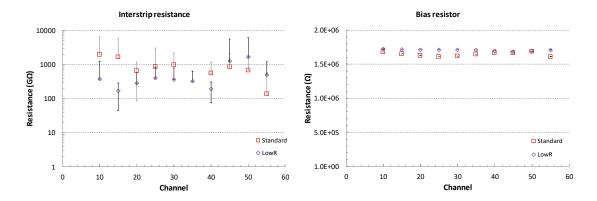

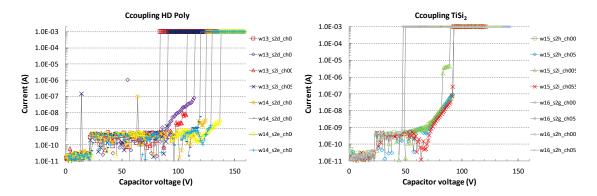

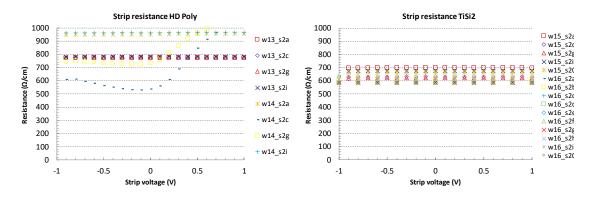

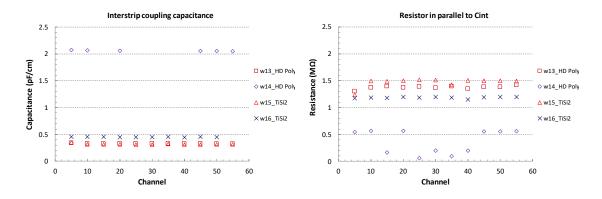

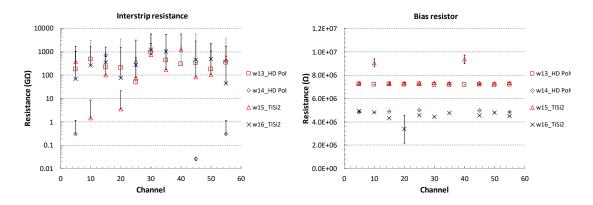

| 6.1.1 Technological parameters                   | . 143 |

|--------------------------------------------------|-------|

| 6.1.2 Leakage current                            | . 155 |

| 6.1.3 Full depletion Voltage                     | . 168 |

| 6.1.4 Strip parameters                           | . 174 |

| 6.1.5 Interstrip parameters                      | . 178 |

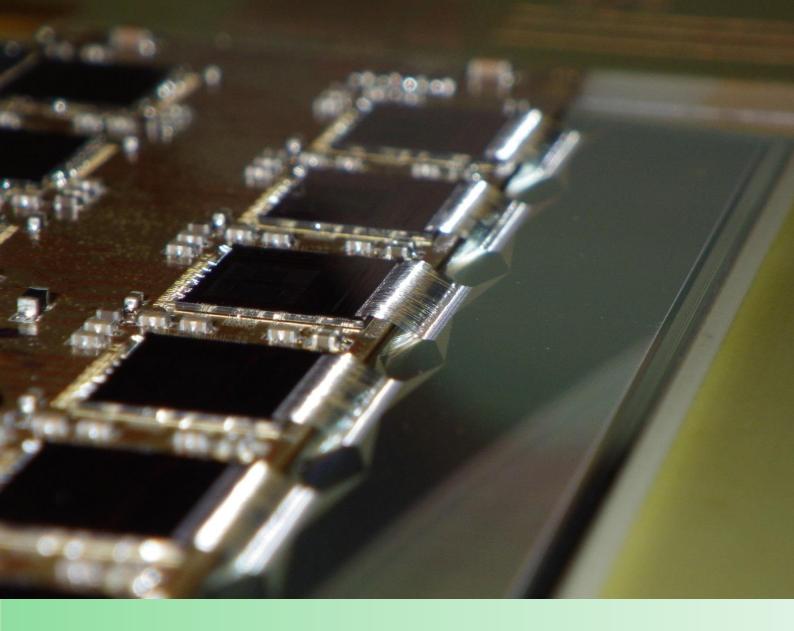

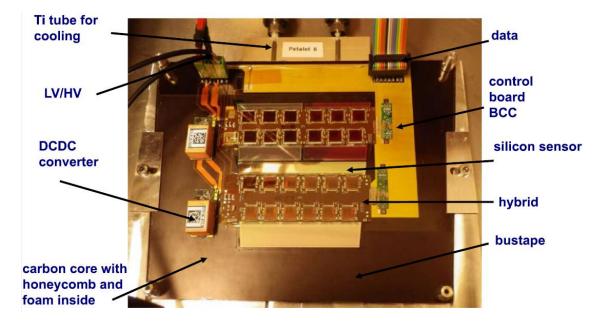

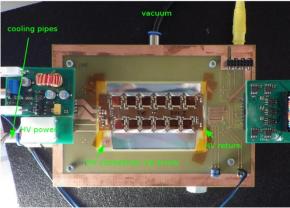

| 6.1.6 Modules building                           | . 184 |

| 6.1.7 Measurements performed by other institutes | . 189 |

| 6.2 LowR sensors                                 | . 192 |

| 6.2.1 Sensor general characteristics             | . 199 |

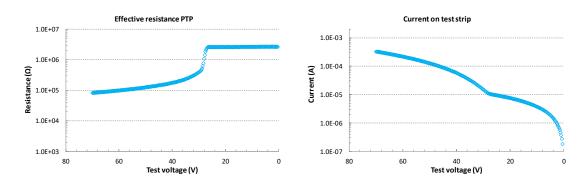

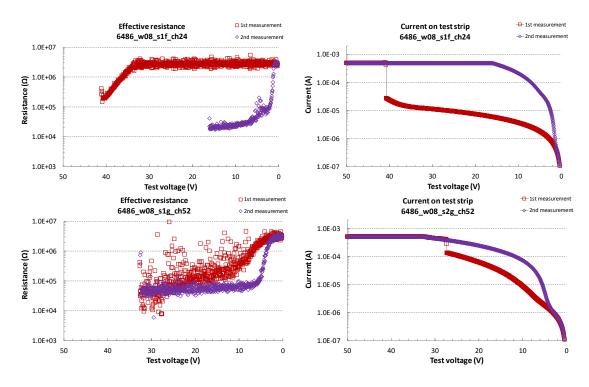

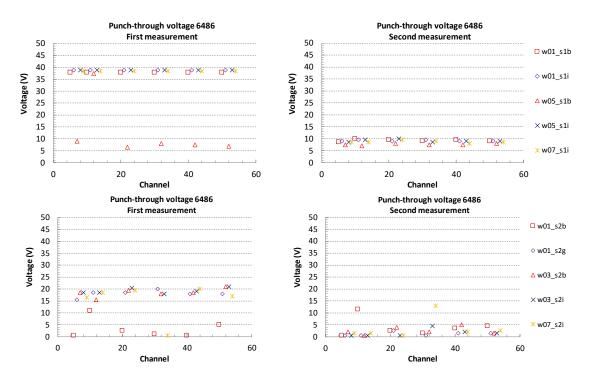

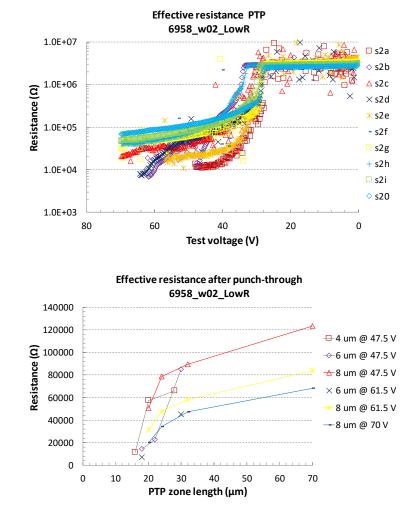

| 6.2.2 PTP measurements                           | . 206 |

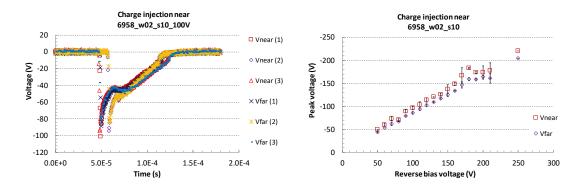

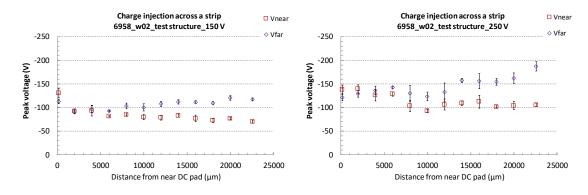

| 6.2.3 Laser Test                                 | . 212 |

| 6.2.4 Technological alternatives                 | . 216 |

| 6.2.5 PTP tests                                  | . 222 |

| 6.2.6 Comparison                                 | . 224 |

| Conclusions                                      | . 227 |

| Bibliography                                     | . 231 |

| List of publications by the author               | . 237 |

| List of conferences by the autor                 | . 239 |

|                                                  |       |

#### Introduction

High-energy physics experiments present technical challenges in different areas due their complexity and demanding operational conditions. The sensors used to detect the particles generated need to provide high resolution and high reliability during their lifetime. This work is focused on the design, fabrication and electrical characterization of microstrip silicon radiation sensors.

The objectives of this work are: fabricate radiation sensor prototypes with challenging design specifications, and develop protection structures and technologies for sensors against beam accidents. At the same time, design, fabrication and electrical characterization processes and know-how are expected to be enhanced.

The design of the radiation sensor prototypes requires the development of a software tool, in order to allow flexibility on the design of the non-conventional sensor structures. The development of the protection structures requires changes in the standard fabrication process used for the radiation sensor prototypes. Therefore, the design flexibility obtained by the developed software tool is expected to be used in the design of the protection structures, while some of the modifications to the fabrication process to achieve protection against beam accidents are expected to be also included in the sensor prototypes.

For both projects the plan is: design of the sensors and their corresponding wafers, use the designed mask layouts in the fabrication processes, complete electrical characterization of the resulting wafers to validate the fabrication process, complete electrical characterization of the sensors to validate the designs, integrate the sensor prototypes with the readout electronics, simulate beam accidents to test the designed protection structures.

#### Framework: High-energy physics experiment

To understand the physics of the standard model and beyond, several laboratories around the world [1] - [6] utilize the most advanced techniques and equipment in high-energy physics experiments. To study the basic constituents of matter, the European Organization for Nuclear Research (CERN) uses accelerators to move particles inside a cavity at high speeds and forces them to collide using detector systems to extract experimental data that are useful for improved understanding of the fundamental laws of nature. The main project at CERN is the Large Hadron Collider (LHC) and its most relevant detector for this work is ATLAS (A Toroidal Large Hadron Collider Apparatus).

#### 1.1 The LHC and the ATLAS experiment

The LHC is currently the world's largest and most powerful particle accelerator [6]. The LHC, inside its main 27 km ring located 100 m underground, accelerates hair-thin beams of particles just below the speed of light before they are forced to collide. The LHC's high-energy particle collisions (up to 14 TeV) may yield extraordinary discoveries about the nature of the physical universe.

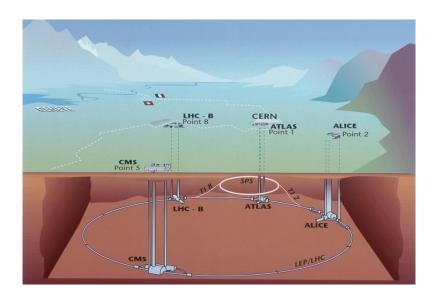

More than 10000 scientists, engineers and students from 113 nations on five continents contribute to the LHC, which is headquartered at the CERN laboratory in Geneva, Switzerland. All the controls for the accelerator, its services and technical infrastructure are housed under one roof at the CERN Control Centre. From here, the beams inside the LHC are made to collide at four locations around the accelerator ring, corresponding to the positions of four particle detectors: ATLAS (A Toroidal Large Hadron Collider Apparatus), CMS (Compact Muon Solenoid), ALICE (A Large Ion Collider Experiment) and LHCb (Large Hadron Collider beauty). Figure 1.1 provides a sketch of the LHC and its four detectors. The LHC experiments attempt to uncover the origins of mass, shed light on dark matter, expose the hidden symmetries of the universe and possibly find extra dimensions in space.

To achieve such high-energy collisions, thousands of powerful superconducting magnets of different types and sizes steer the beams around the LHC's main ring. This requires the magnets to work at temperatures close to absolute zero. For this reason, much of the accelerator is connected to a liquid-helium distribution system, which cools the magnets, as well as to other supply services.

Two proton beams travel in opposite directions in separate beam pipes, which are kept in an ultrahigh vacuum. These two beams are then made to cross paths and some of the particles smash head-on into one another. Just prior to collision, another type of magnet is used to move the particles closer together to increase the chances of collisions. Table 1.1 lists the main parameters of the LHC machine.

#### Framework: High-energy physics experiment

Figure 1.1 Overview of all LHC experiments [6].

| Parameter                               | Symbol        | Value                                             |

|-----------------------------------------|---------------|---------------------------------------------------|

| Beam energy                             | Е             | 7.0 TeV                                           |

| Dipole magnetic field                   | В             | 8.4 T                                             |

| Luminosity                              | L             | 10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> |

| Injection energy                        | $E_i$         | 450 GeV                                           |

| Circulating current/beam                | $I_{beam}$    | 0.53 A                                            |

| Number of bunches                       | $k_b$         | 2835                                              |

| Time between bunches                    | $\tau_{b}$    | 24.95 ns                                          |

| Protons per bunch                       | $N_b$         | 1.05x10 <sup>11</sup>                             |

| Stored beam energy                      | $E_s$         | 334 MJ                                            |

| r.m.s beam radius at intersection point | σ*            | 16 μm                                             |

| Crossing angle                          | Φ             | 200 μrad                                          |

| Beam lifetime                           | $\tau_{beam}$ | 22 h                                              |

| Luminosity lifetime                     | $	au_{L}$     | 10 h                                              |

Table 1.1 The LHC machine's parameters [6].

Collisions occur where the four experiments are located and for each collision, the physicist's goal is to track and characterize all the different particles that were produced in order to reconstruct the process in full.

The experiments in the LHC focus on different areas, such as studying the properties of quark-gluon plasma by analysing lead-ion collisions, asymmetry between matter and antimatter present in interactions of B-particles, as well as a wider range of physics—from the search for the Higgs boson to supersymmetry (SUSY) and extra dimensions [6]. General-purpose detectors, such as CMS and ATLAS, cover the widest range of physics.

#### 1.1.1 ATLAS

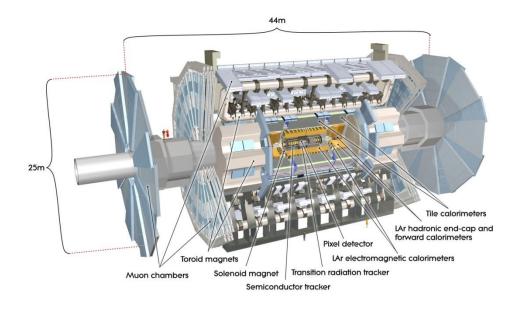

ATLAS is one of two general-purpose detectors at the LHC. ATLAS is 46 m long, 25 m high and 25 m wide. The 7000-tonne ATLAS detector is the largest particle detector ever constructed [7]. It sits in a cavern 100 m underground near the main CERN site, close to the village of Meyrin in Switzerland. More than 3000 scientists from 174 institutes in 38 countries work on the ATLAS experiment.

Beams of particles from the LHC collide at the centre of the ATLAS detector, making collision debris in the form of new particles that fly out from the collision point in all directions. Different detecting subsystems arranged in layers around the collision point record the paths, momentum and energy of the particles, allowing them to be individually identified. A huge magnet system bends the paths of charged particles so that their momenta can be measured.

The ATLAS detector consists of four major components: the inner detector, which measures the momentum of each charged particle; the calorimeter, which measures the energies that the particles carry; the muon spectrometer, which identifies and measures the momenta of muons; and the magnet system, which is responsible for bending charged particles for momentum measurement. Figure 1.2 depicts the dimensions for the ATLAS detector and its subsystems.

Figure 1.2 The ATLAS detector [7].

The interactions in the ATLAS detector create a large quantity of data. To collect and analyse this data, a complex system is required; it consists of the following: the trigger system—selecting 100 interesting events per second out of 1000 million, the data acquisition system—channelling the data from the detectors to the storage, and the computing system—analysing 1000 million events recorded per year [7].

#### 1.1.2 The Inner Detector

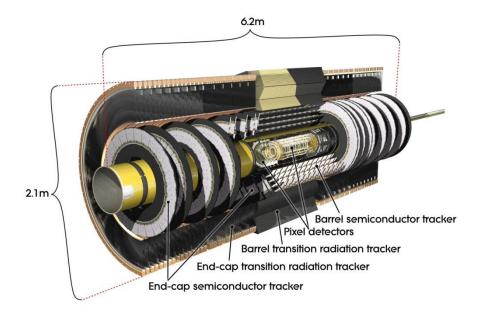

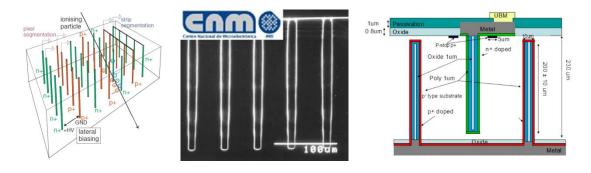

The Inner Detector (ID) is the component of the ATLAS detector that is closest to the interaction point. It is formed by three different tracking technologies, each one being the representative characteristic of the two main parts of the ID: the semiconductor tracker (SCT), which comprises the pixel detector and the strip detector; and the transition-radiation tracker (TRT). Figure 1.3 displays the ID structure and its main components.

In the barrel region, which is closest to the interaction point and coaxial with the beam pipes, the high-precision detectors are arranged in concentric cylinders of different radii around the beam axis. There are three cylindrical silicon-pixel layers, four cylindrical layers of barrel-silicon micro-strip modules (SCT) and 72 straw layers in the barrel-TRT modules. The barrel TRT straws are parallel to the beam direction.

The end-cap detectors are mounted on disks perpendicular to the beam axis. All end-cap tracking elements are located in planes that are perpendicular to the beam direction and are separated by different gaps. There are three silicon-pixel disks, nine disks of the end-cap silicon-strip layers and 40 planes of TRT wheels. Figure 1.4 displays diagrams illustrating the sensors and structural elements in the ID for both the barrel and end-cap regions.

Figure 1.3 The Inner Detector [7].

The ATLAS pixel detector provides high granularity and high precision set of measurements as close to the interaction point as possible. There are 80 million pixels or channels; the pixel size is  $50 \times 400~\mu m^2$  with a resolution of  $14 \times 115~\mu m^2$ . Each barrel has 1744 modules with 46080 readout channels per module, while there are 6.6 million channels on the three pixel disks per end-cap.

#### The LHC and the ATLAS experiment

# R = 1082 mm R = 554 mm R = 544 mm R = 443 mm R = 443 mm R = 371 mm R = 299 mm SCT R = 325 mm R = 505 mm R = 505 mm R = 505 mm R = 505 mm R = 50 mm Pixels R = 1082 mm Pixels R = 1082 mm Fixed mm Fixed mm Pixels R = 1082 mm Fixed mm Fi

Figure 1.4 Sensors and structural elements of the ID in the barrel (left) and in the end-cap (right) with pixel and SCT-barrel elements depicted for reference [7].

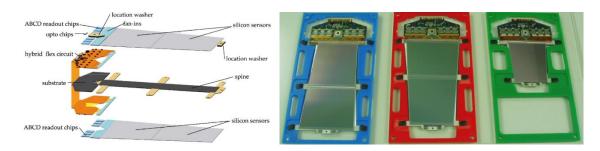

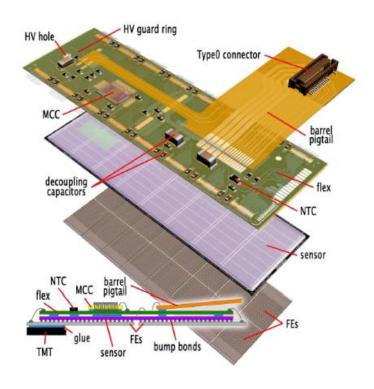

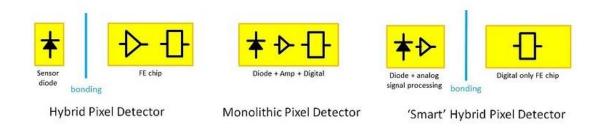

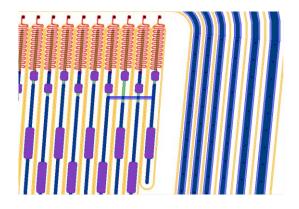

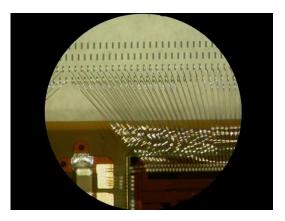

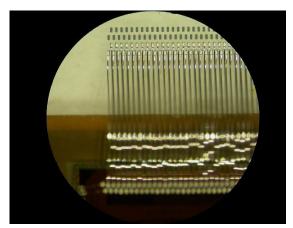

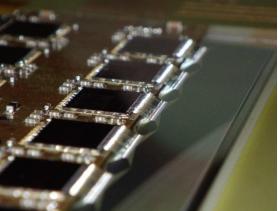

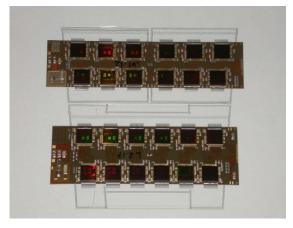

The SCT-strips system is designed to provide eight precision measurements per track in the intermediate radial range, contributing to the measurement of momentum, impact parameter and vertex position. Modules are the basic structural components of the system. Each module uses strip-silicon sensors as radiation-to-electrical signal transducers and has the electronic elements to emit the sensor's signal from the module. The barrel modules and end-cap modules are similar in construction; however, their associated sensor geometries are different. Figure 1.5 displays the structure and pictures of end-cap modules.

Figure 1.5 The SCT modules for the end-cap region. A schematic view with its different components (left) and three different modules (right): outer, middle and inner modules can be observed in the pictures from left to right [8].

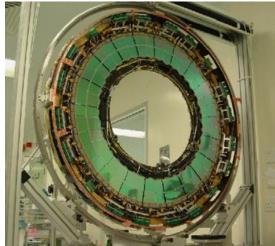

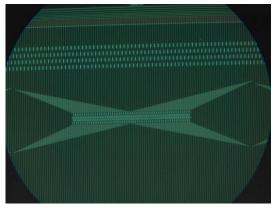

The SCT-strip system consists of 4088 two-sided modules and over 6 million implanted readout strips or channels. The silicon is distributed in 60 m<sup>2</sup> over four cylindrical barrel layers and 18 planar end-cap disks, which are illustrated in Figure 1.6. The readout for strips is done every 80  $\mu$ m on the silicon; this allows the positions of charged particles to be recorded to an accuracy of 17  $\mu$ m per layer.

The TRT has 350000 read-out channels in a volume of 12 m<sup>3</sup>; the basic detector element is a straw tube 4 mm in diameter with a gold-plated tungsten wire 0.03 mm in diameter at the centre. There are 50000 straws in the barrel region and each straw is 144 cm long, while there are 250000 straws on the end-caps with each straw being 39 cm long.

#### Framework: High-energy physics experiment

Figure 1.6 The end-cap disk of the SCT. One side of the disk comprises outer and inner modules (left), while the other side is built with middle modules (right) [8].

#### 1.2 The ATLAS Upgrade

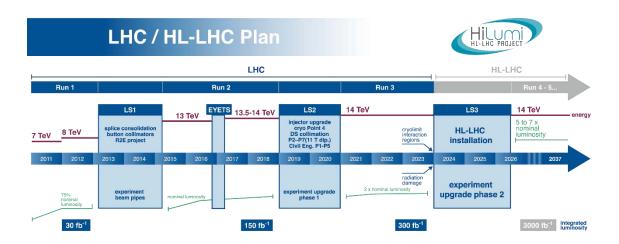

The LHC began to accelerate particles in 2009. The current ATLAS detector is now active and has been reading data since it was first turned on in 2010. The LHC is being upgraded to exploit its full potential by increasing the luminosity by up to  $10^{35}$  cm<sup>-2</sup> s<sup>-1</sup> [9], which is ten times its design-luminosity value. The upgrade is planned to follow many phases, three of which have already been scheduled. Each of these three phases began with a long shutdown period for detector upgrades.

Phase-0 began in 2013 and the operation restart occurred during 2015. The primary targets in this phase were to reach the system-design energy and nominal luminosity of  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>, as well as to increase the integrated luminosity from the actual 30 fb<sup>-1</sup> to 150 fb<sup>-1</sup>. Phase-I should commence in 2019 and the goals are to reach the ultimate-design luminosity of 2 x  $10^{34}$  cm<sup>-2</sup>.s<sup>-1</sup> and to increase the integrated luminosity to 300 fb<sup>-1</sup>. Phase-II is scheduled for 2024 and the targets are to reach a higher luminosity of 5 x  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> and to continue increasing the integrated luminosity to reach 3000 fb<sup>-1</sup> [10]. Figure 1.7 illustrates the planned schedule for the LHC upgrade to the High-Luminosity LHC (HL-LHC).

The ATLAS experiment plans stages of upgrades, including a number of detector, trigger, software, and computing developments, which will be required to continue the exploitation of ATLAS throughout and beyond the next decade. Upgrades are required to cope with the anticipated increase in the beam luminosity.

For Phase-0, a new pixel-detector element, the Insertable B-Layer (IBL), has been installed. Upgrade plans for Phase-I include new muon small wheels and new electronics for calorimeter triggering. For Phase-II, some upgrades of the muon chambers and calorimeter electronics; major upgrades on the triggers Data Acquisition (DAQ); and

#### The ATLAS Upgrade

possibly a new forward calorimeter as well as a completely new inner tracker will be installed [11].

Figure 1.7 The LHC upgrade plan [10].

The existing ID was not designed to meet the requirements that are part of the Phase-II upgrade as its performance would suffer the effects of radiation damage, bandwidth saturation and limitations from detector occupancy due to the increased beam luminosity. For Phase-II of the upgrade, the ID will be replaced with a new tracking system that is fully made of semiconductor detectors; therefore, the TRT regions will be covered with silicon-radiation sensors, while both the pixel detector and the strip detector will be upgraded.

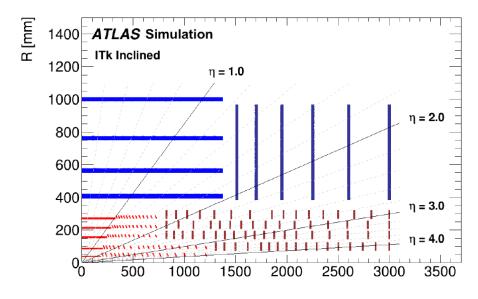

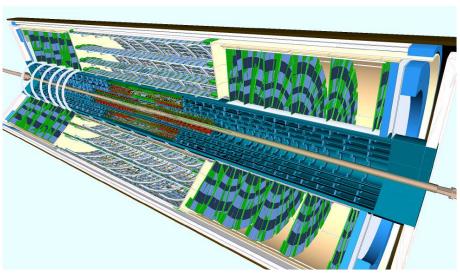

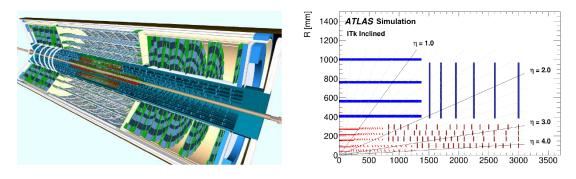

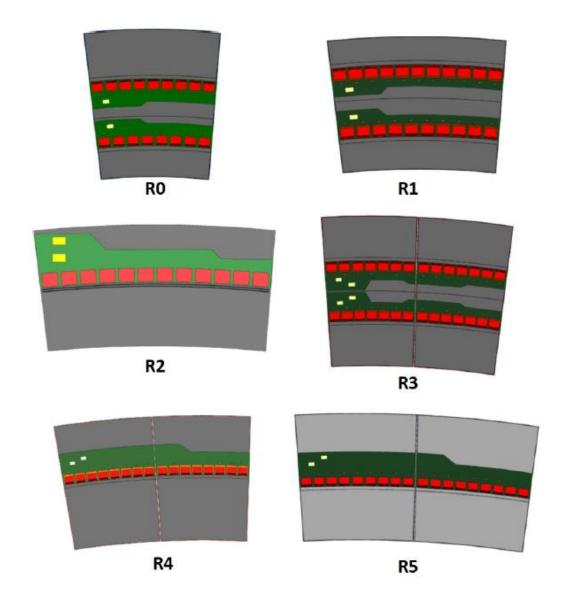

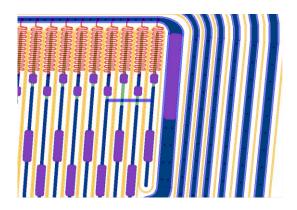

The upgraded ID is known as the Inner Tracker (ITk). The layout for the ITk comprises a more complex structure, especially for the pixel layers close to the beam line [12]. The ITk pixel detector consists of a central five-layer barrel region with four layers of rings composing the end-cap region. The barrel layers will feature also inclined modules. The ITk strip detector consists of a four-layer barrel section and one end-cap section on each side, with six disks each. The design of the future ITk is depicted in Figure 1.8.

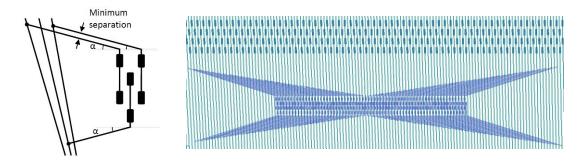

The two inner layers of the strip-barrel will be equipped with short strips of 24.1 mm length. The two outer layers will have longer strips with 48.2 mm. All strips in the barrel section will have a constant pitch of 75.5  $\mu$ m. The strips in the end-cap will be radially distributed, pointing to the centre of the beam axis. The strip lengths in the end-caps are optimized to keep the strip occupancy below 1%, resulting in different strip lengths increasing from 19.0 mm in the region closest to the beam axis, to 60.1 mm in the outermost region [12].

Figure 1.8 Schematic view of the proposed layout for the ITk . In the layout (up), the red lines represent pixel detectors and the blue lines represent strip detectors. In the sectional view of a simulated model (bottom), the disks on the end-cap sections can be clearly observed [12].

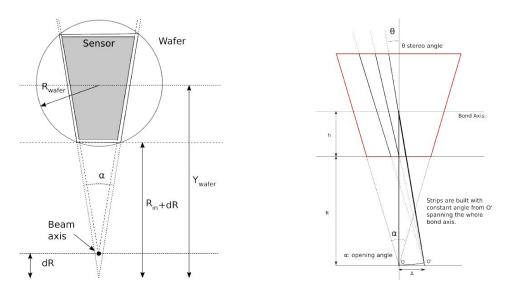

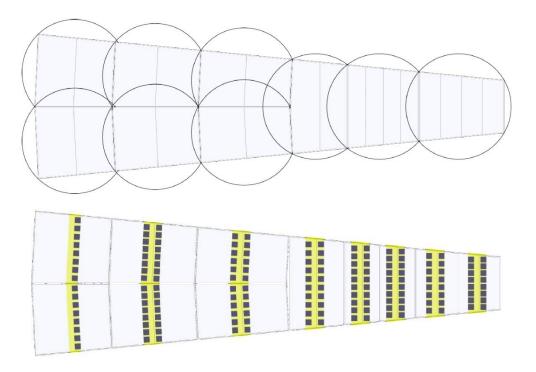

#### 1.2.1 The End-cap Upgrade

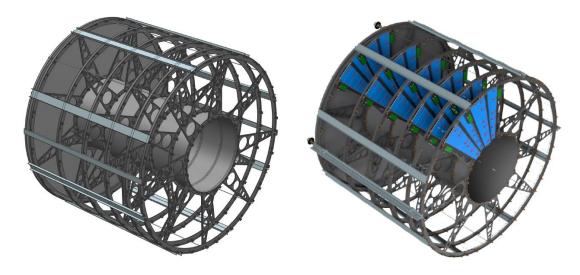

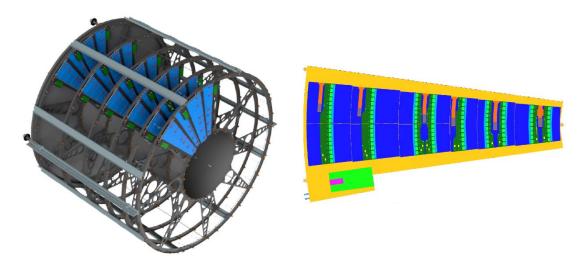

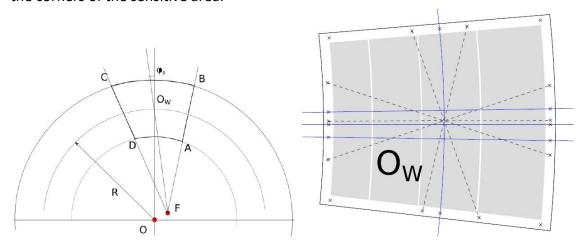

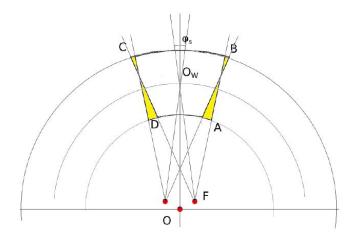

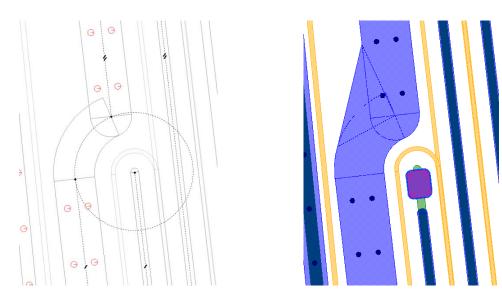

The proposed layout of the ITk includes six strip disks on each end-cap side. Each disk will comprise 32 identical structures, called petals [12]. Each petal is planned to be removable to allow for easier repair than in the current modules on the end-cap disks. Different sensor geometries, electronic components and mechanical structures must be designed and produced. Research activities regarding the strip-silicon radiation sensors for the end-cap upgrade are of particular interest for this work.

The basic mechanical building blocks of the barrel and the end-caps are the stave and petal, respectively. The local supports consist of low mass central cores that provide the mechanical rigidity, support for the modules and houses the common electrical, optical and cooling services. They also provide the accurate alignment and fixation points.

Figure 1.9 illustrates the design of the support structure for one end-cap section. The six disks are supported by an inner tube, which provides the space for the ITk Pixel Detector. The petals for an end-cap disk are mounted onto carbon-fibre wheel structures.

Figure 1.9 Design of the end-cap sections. Support structure (left) and petal modules after insertion (right) [12].

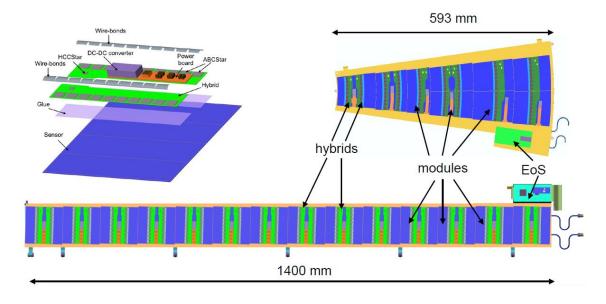

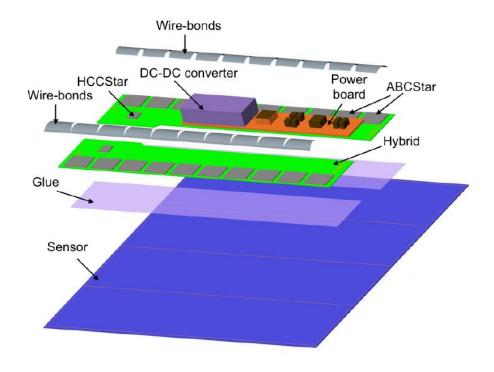

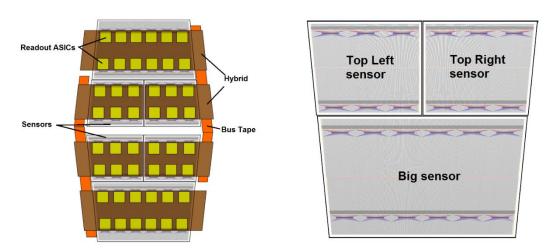

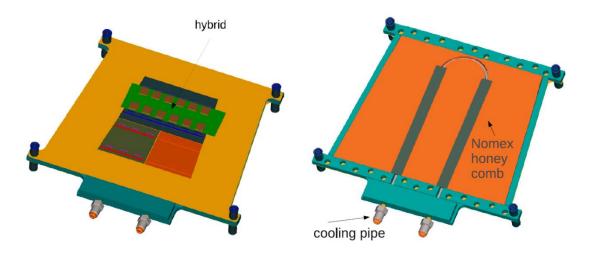

The designs of the stave and petal are depicted in Figure 1.10. For both cases, the silicon strip sensors are electrically connected to readout electronic boards, called hybrids. A sensor and a hybrid form a 'module'. All the power and data links are channelled through an End of Substructure (EoS) card, which forms the interface to the off-detector electronics.

Figure 1.10 Electrical components of the building blocks of the strip detector of the ITk. Composition of a generic module (top left), petal (top right) and stave (bottom) [12].

The main electrical components for both petals and staves are illustrated in Figure 1.10. Hybrids are mounted on each silicon sensor. Each hybrid contains ABCStar chips, which are application-specific integrated circuits (ASICs) fabricated on 130 nm complementary metal-oxide semiconductor (CMOS) technology. Each hybrid also has a Hybrid Controller

Chip (HCC Star), which interfaces the ABCStars to the End of Substructure (EoS). Trigger, Timing, and Control (TTC) signals are sent from the EoS to each HCCStar via the TTC bus. Each HCCStar has a unique address and sends its data to the EoS using a dedicated link, known as e-link. The TTC signals are sent to each HCC in parallel mode. The TTC bus and data lines, which sit beside the power bus, are integrated into a single copper/kapton bus tape that is co-cured onto the petal core. The EoS has a low-power GigaBit Transceiver (IpGBT), which connects to the HCCs, and a Versatile link (VTRX) fiber-optic driver.

The low-voltage power converter and high-voltage switching circuits are combined into one power board, which will be located between two hybrids and connected to the EoS, and the power will be distributed to each hybrid via a power bus.

The petal core, which is wedge shaped and has a V-shaped cooling tube, supports and cools end-cap modules. A single length of tube cools each module in the outer three rings, while two lengths of tube cool the inner three modules, which have higher-power densities.

Regarding power load and servicing needs, a cable bus will run down each outer edge of a petal, with the modules glued directly to the core face-sheets. On each side of the petal, there will be an EoS, which will connect the cable bus on that side.

A more detailed description of the electrical and mechanical properties of the ITk is available in the literature [12]. This work is focused in the development of strip sensor prototypes for the strip end-cap section of the ITk.

#### 1.3 The RD50 Collaboration

The RD50 Collaboration is a CERN's approved Research and Development Project that was created in 2002 and focuses on radiation-hard semiconductor devices for high-luminosity colliders. The RD50 collaboration comprises more than 280 researchers working in 49 international research institutes.

The primary objective of the RD50 Collaboration is to develop radiation-hard semiconductor detectors that can operate beyond the limits of present devices. These devices should withstand fast hadron fluences of the order of 10<sup>16</sup> cm<sup>-2</sup>, as expected, for example, for a luminosity upgrade of the LHC to 10<sup>35</sup> cm<sup>-2</sup> s<sup>-1</sup> [13].

To discuss research activities, results and new studies, two dedicated RD50 workshops take place annually and many status reports and presentations are delivered at different conferences worldwide.

There are four key areas of study in RD50. Defect and Material Characterization, which focuses on both the electrical parameters and chemical structure of the defects and on studies regarding defect engineering for better devices. Detector Characterization, which focuses on studies regarding charge multiplication in silicon detectors, the

#### The RD50 Collaboration

electric-field profile in the irradiated sensors, long-term annealing effects, effective trapping time, and development of simulation models for charge multiplication. New Structures, which focus on thin-pixel detectors, double-sided 3D detectors, trenched detectors, stripixels and charge-multiplication studies. The fourth key area is Full Detector Systems, where the research activity is related to charge multiplication in segmented silicon detectors, the geometry role in multiplication, annealing studies of charge-collection efficiency, irradiations to extremely high fluences, detectors designed for operation with charge multiplication, and novel sensor design and features, such as punch-through protection and the SCP technique for slim edges [14].

Studies regarding the usage of punch-through protection structures for future siliconradiation sensors are also particularly interesting for this work.

#### Radiation detectors

#### 2.1 Radiation and units

Radiation is a form of energy transmitted through space. Many types of radiation exist, some of them are more popular than others and are part of daily conversations, such as light, radio-waves, microwaves and X-rays [15]. This work is focused in high energy particle radiation.

The different types of radiation can be classified considering their source or taking into account their effects on matter, when interactions between radiation and matter occur. Independent of their classification, different but interrelated units are used in radiation metrology: activity, exposure, absorbed dose and dose equivalent.

Activity refers to the amount of radiation released by a material, whether it emits alpha or beta particles, gamma rays, x-rays, or neutrons, a quantity of radioactive material is expressed in terms of its activity, which represents how many atoms in the material decay in a second. The unit in the International system of units (SI) is the Bequerel "Bq", which corresponds to one disintegration per second. Another unit used due to its historical background is the Curie "Ci", which corresponds to the activity of one gram of pure <sup>226</sup>Ra.

$$1 Bq = 2.703 \times 10^{-11} Ci$$

Equation 2.1

Exposure measures the electric charge, which is released in a given volume of air due to ionizing radiation like X-rays and gamma rays, per unit mass of air. The units for exposure in the SI is Coulomb/kilogram (C/kg). Another widely used unit is the Roentgen "R"

$$1 R = 2.58 \times 10^{-4} C/kg$$

Equation 2.2

Absorbed dose refers to the amount of radiation absorbed by an object, it is the amount of energy that radiation deposits in materials per unit mass. Two commonly units are used: the Rad "rad" in the Centimetre-Gram-Second unit system (CGS), and the Gray "Gy" in the SI.

$$1 Gy = 1 I/kg = 100 rad$$

Equation 2.3

Dose equivalent, or effective dose, is the combination of both the amount of radiation absorbed and the medical effects of that type of radiation. For beta and gamma radiation, the dose equivalent is the same as the absorbed dose. In contrast, the dose equivalent is larger than the absorbed dose for alpha and neutron radiation, due to the higher damage to the human body these types of radiation produce. The dose equivalent  $H_T$  is calculated using the absorbed dose  $D_{T,R}$ , corresponding to a determined type of tissue T and radiation R, and the radiation-weighting factor  $W_R$ .

$$H_T = \sum_{R} W_R. D_{T,R}$$

Equation 2.4

The unit in the SI for the dose equivalent is the Sievert "Sv", expressed in J/Kg as the radiation-weighting factor is a factor without units. In radiation safety, the most commonly used unit is the milli Sievert (mSv) [15].

On the other hand, fluence is defined as the number of incident particles per cross-sectional area. The fluence is commonly expressed in number of particles/cm<sup>2</sup>. Table 2.1 lists different units for physical, operational and protection related quantities in radiation metrology.

| Quantity            | Name        | Symbol | Unit                                       |

|---------------------|-------------|--------|--------------------------------------------|

| Exposure (X)        | Roentgen    | R      | 2.58 x 10 <sup>-4</sup> C.kg <sup>-1</sup> |

| Absorbed dose (D)   | Rad         | Rad    | 100 erg.g <sup>-1</sup>                    |

| Absorbed dose (D)   | Gray        | Gy     | J.kg <sup>-1</sup>                         |

| Activity (A)        | Becquerel   | Bq     | S <sup>-1</sup>                            |

| Dose equivalent (H) | Sievert     | Sv     | J.kg <sup>-1</sup>                         |

| Fluores (Φ)         | (reciprocal |        | m <sup>-2</sup> or cm <sup>-2</sup>        |

| Fluence (Φ)         | area)       |        | iii or cm -                                |

Table 2.1 Radiation units [15].

Another unit used to describe radiation is the electron volt "eV", which describes the radiation energy. One eV is defined as the energy gained by an electron moving through an electrical potential difference of one volt [16]. The radiation energy is expressed in Joule "J" in the SI.

$$1 eV = 1.602 \times 10^{-19} I$$

Equation 2.5

#### 2.2 Radiation types and sources

To classify the types of radiation, its source or origin can be considered. As already stated, this work focuses on the detection of particle radiation.

Neutrons are sub-atomic particles that do not feature electrical charge and their mass is 939.57 MeV. Alpha particles are bound systems of two protons and two neutrons, which are identical to a  $^4$ He nuclei [17]. They have positive electrical charge of 3.204 x  $10^{-19}$  C. and a mass of 3727.33 MeV. Beta particles can be electrons or positrons, with negative or positive charge respectively of  $1.602 \times 10^{-19}$  C. The mass for both types of beta particles is 0.511 MeV. Gamma rays are electromagnetic radiation, formed by high-energy photons between one hundred keV and a few MeV. Photons do not have electric charge nor mass.

A variant of a chemical element with different number of neutrons is called an isotope [17]. For example, <sup>12</sup>C is the most common form of carbon in the planet, with 6 protons

#### Radiation types and sources

and 6 neutrons in its nucleus. Nevertheless, two isotopes of Carbon also exist, <sup>13</sup>C and <sup>14</sup>C with 7 and 8 neutrons respectively.

Some isotopes are unstable due to excess of nuclear energy, which are called radioactive isotopes. The excess of nuclear energy can be emitted as gamma radiation or a new particle, alpha or beta, may be created. This emission of energy is called radioactive decay. The remaining isotope after a radioactive decay is known as a decay product. If a decay product is not stable, more radioactive decays will take place until the decay product is a stable isotope.

#### 2.2.1 Natural sources

Three types of natural sources of radiation are considered: cosmic, terrestrial, and internal. Exposure from most of these sources is minimal and, therefore, does not cause any measurable damage to people.

Cosmic radiation sources are related to space origins. The outer space is filled with radiation that comes from a variety of sources such as burning and exploding stars. These bodies produce immense amounts of radiation, some of which reach earth. Fortunately, the earth's atmosphere acts as a shield to the worst of these radiations, such as ultraviolet rays from the sun, which are blocked by the ozone layer. Another natural protection against radiation is the earth magnetic field. It captures electrons and protons, forming the Van Allen radiation belts [15]. Two Van Allen radiation belts exist, an internal one centred at about 3000 km and an external one centred at about 22000 km from the earth's surface.

Terrestrial radiation sources are present in small quantities all around us. The main source of terrestrial radiation is the uranium element and its decay products such as thorium, radium, and radon. Although the overall natural concentration of these radioactive materials is within the tolerable range of humans, some parts of the world have been identified to present higher levels of uranium and thorium in surface soil have increased the radiation to dangerous levels. The average activity values for <sup>238</sup>U and <sup>40</sup>K are 33 Bq/kg and 412 Bq/kg, while maximum activity values of 1000 Bq/kq for <sup>238</sup>U in Sweden and 3200 Bq/kg for <sup>40</sup>K in the United Kingdom were reported [15].

Internal radiation sources are related to the human body itself, which contain some traces of radioactive elements that expose human tissues to continuous low-level radiation. The main radioactive isotope present is the human body is the  $^{40}\rm{K}$ . Potassium is regularly ingested and it is important for biological functions in the human body. The radioactive isotope  $^{40}\rm{K}$  emits gamma rays , which are normally absorbed by the human tissues. The second most important radioactive isotope in the human body is  $^{14}\rm{C}$ , which emits electrons.

Table 2.2 lists some average annual effective dose values for different types of natural radiation.

#### Radiation detectors

| Source                    | Worldwide average<br>annual effective dose<br>(mSv) | Typical range<br>(mSv) |

|---------------------------|-----------------------------------------------------|------------------------|

| External exposure:        |                                                     |                        |

| Cosmic rays               | 0.4                                                 | 0.3 - 1.0              |

| Terrestrial gamma rays    | 0.5                                                 | 0.3 - 0.6              |

| Internal exposure:        |                                                     |                        |

| Inhalation (mainly radon) | 1.2                                                 | 0.2 - 10               |

| Ingestion                 | 0.3                                                 | 0.2 - 0.8              |

| Total                     | 2.4                                                 |                        |

Table 2.2 Average radiation dose from natural sources [15].

#### 2.2.2 Artificial sources

These sources are made for specific purposes and generally give off one type of radiation. Common examples of such sources are medical x-ray machines, airport x-ray scanners, nuclear medicine apparatus, particle accelerators, or lasers. For comparison with natural source related doses, a chest X-ray test results in a typical dose of 0.05 mSv, when a Computer Tomography scan is about 10 mSv [15].

A particle accelerator is built either in the form of a ring, or circular accelerator ("cyclotron"), where a beam of particles travels repeatedly round a loop, or in a straight line, known as linear accelerator, where the particle beam travels from one end to the other. Figure 2.1 illustrates a picture of a linear accelerating cavity.

Figure 2.1 Linear accelerating cavity image. TESLA 9-cell 1.3 GHz SRF cavities for ILC [5].

In linear accelerators, particles travel in vacuum through a long tube. Electromagnets keep the particles confined in a narrow beam. When the particle beam collides with a target, normally at the end of the tube, detectors record the events as the subatomic particles and radiation are released.

#### Radiation types and sources

Circular accelerators perform essentially the same operation as linear accelerators. Nevertheless, instead of using a long linear track, they accelerate the particles around a circular path for many cycles. Magnets are used to bend the path of the beam of particles and to create a nearly circular path. The more energy a beam of particles has, the greater the magnetic field needed to bend its path.

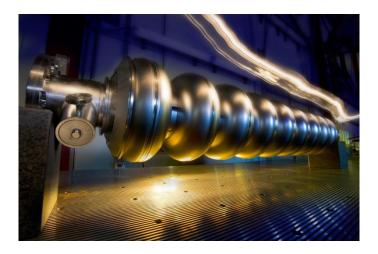

A synchrotron is a type of circular particle accelerator. Its main characteristic is the synchronization between the applied magnetic field and the kinetic energy of the particles being accelerated, to reach high energy levels in the order of GeV. At each pass, the magnetic field is strengthened to accelerate the particle beam. The first element is the linear accelerator (LINAC), where the particles are produced by a canon and have a first acceleration. Synchrotrons are mainly used in particle colliders and as synchrotron radiation sources.

The LHC at CERN uses three synchrotrons to accelerate the protons before injecting them into the main collision ring [6]. The proton source is a simple bottle of hydrogen gas. An electric field is used to strip hydrogen atoms of their electrons to yield protons. The first accelerator in the chain accelerates the protons to the energy of 50 MeV. The beam is then injected into the Proton Synchrotron Booster (PSB), which accelerates the protons to 1.4 GeV, followed by the Proton Synchrotron (PS), which pushes the beam to 25 GeV. Protons are then sent to the Super Proton Synchrotron (SPS) where they are accelerated to 450 GeV.

Another example is a synchrotron radiation facility like ALBA, which is a machine that produces many beams of bright X-ray light. Each beam is guided through a set of lenses and instruments, called a beamline, where the X-rays illuminate and interact with samples of material being studied [18].

Synchrotron light is produced when high-energy electrons, circulating in a storage ring, are deviated by magnetic fields. Since first synchrotron radiation beam was observed in 1947, a lot of progress has been made in accelerator physics, electronics and computing as well as in magnet and vacuum technologies. Figure 2.2 depicts a generic structure for a synchrotron radiation source facility.

Figure 2.2 Synchrotron radiation source facility diagram [16].

#### 2.3 Interaction of radiation with matter

Electromagnetic radiation is normally characterized by the frequency of the oscillating waves associated of the energy irradiated. The higher the frequency, the higher the energy related the electromagnetic radiation. Electromagnetic radiation that has enough energy to move atoms in a molecule or make them vibrate, but not enough to remove electrons, is referred to as non-ionizing radiation. Examples of this kind of radiation are visible light, and microwaves. No energy threshold for non-ionizing radiation is defined, but normally radiation with energy less than 10 eV is considered non-ionizing [15].

#### 2.3.1 Ionizing radiation

Radiation that is considered as ionizing radiation has enough energy to remove electrons from atoms, thus creating ions. Ionizing radiation is used to generate electric power (as in solar cells), to kill cancer cells, and in many industrial processes.

The flow of charged particles, such as alpha and beta particles, are related to direct ionizing radiation, because coulomb interaction with matter causes ionization and excitation of atoms. Indirect ionizing radiation is radiation of particles or photons, which have no charge and may transfer energy to charged particles during their interaction with matter, nuclei and atom electrons due to electromagnetic or nuclear interaction.

#### 2.3.1.1 Alpha particles

Alpha particles are heavier than others and have charge. They react strongly with matter, producing large numbers of ions per unit length of their path. As a result, they do not feature long penetration lengths. Alpha particles may interact with either nuclei or orbital electrons in any absorbing medium. An alpha particle moving close to a nucleus may be deflected with no change in energy, known as Rutherford scattering, or deflected with small change in energy or absorbed by nucleus, causing nuclear transmutation. The most probable processes involved in the absorption of alphas are ionization and excitation of orbital electrons. Ionization occurs whenever the alpha particle is sufficiently close to electron to pull it out from orbit though coulomb attraction, each time this occurs, the alpha particle loses kinetic energy. The alpha particle also loses kinetic energy by exciting orbital electrons with interactions that are insufficient to cause ionization. As it is slowed, the alpha particle has tendency to cause ionization at an increasing rate. When the alpha particle is close to the end of its path, its rate of ionization peaks and it stops, collects two electrons and becomes a helium atom. Since alpha particles are low in penetration ability, they themselves are usually not hazardous for external exposure, unless the alpha-emitting nuclide is deposited into the human organism. When internally deposited, alpha particles are normally more dangerous than most other types of particles because large amounts of energy are deposited within a small volume of tissue.

#### 2.3.1.2 Beta particles

Beta particles may interact with electrons as well as nuclei in the medium which they are moving through. Beta particles moving near nucleus will be deflected by the coulomb forces and they may lose kinetic energy. The interactions of beta particles with orbital electrons are the most important, as coulomb repulsion between beta particles and electrons frequently results in ionization. In the ionization process, the beta particles lose energy which is equal to the kinetic energy of the electron plus the energy used to free it from the atom. Beta particles also cause excitation of external orbital electrons, which in turn leads to the emission of ultraviolet photons.

The final condition of a beta particle depends on its charge. For a negatively charged beta particle, after its kinetic energy has been spent, it may combine with a positively charged ion, or become a free electron. In case of positrons, despite they dissipate their kinetic energy just like beta particles through ionization and excitation, they cannot exist at rest in the vicinity of the electrons. When a positron has been slowed sufficiently, it will be attracted to the opposite charge of an electron. When the electron and positron collide, they are both annihilated and an amount of energy equal to the sum of the particle masses is released in the form of two photons. These photons are referred to as annihilation radiation. Both annihilation photons carry energy of 0.512 MeV, which is equivalent to the rest mass of the electron or the positron. Like alpha particles, beta particles have a characteristic average traveling distance through matter that is dependent upon their initial kinetic energy.

#### 2.3.1.3 Gamma rays

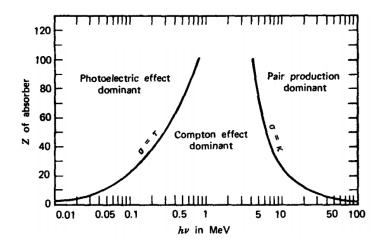

The interaction of gamma rays with matter involves several distinct processes. The relative importance and efficiency of each process is dependent on the energy of the photons and the density and atomic number of the absorbing medium. Figure 2.3 describes the relation between the energy of the photons and the atomic number of the material that determines which interaction processes are dominant.

Figure 2.3 Interaction mechanisms between phonons and matter. Relation between dominant interaction processes for photons with the atomic number of the absorbing material and photon energy [17].

#### Radiation detectors

In the photoelectric effect, an electron is emitted from an atom and the photon disappears. The electron then moves through matter and loses its energy as described for beta interactions. This is the predominant effect at low gamma energies.

In case of Compton scattering, the photon interacts with an electron, causing an increase in the electron's energy. A new photon with a smaller energy is then emitted. The electron interacts as explained earlier. The new photon may escape or be absorbed through the photoelectric effect.

For pair production, high-energy photons are absorbed and two particles are created: an electron and a positron, which share the total energy of the photon. The electron interacts with matter, as explained above for beta interaction, while the positron loses its energy through ionization or excitation. If it is stationary, the positron interacts with an electron creating two photons with energies of 0.512 MeV each, known as annihilation radiation. These two photons may escape or interact with matter through the Compton scattering or Photoelectric effect.

#### 2.3.1.4 Neutrons

Neutrons are not able to ionize an atom directly due their lack of charge. Nevertheless, indirect ionization occurs if the neutron is absorbed into a stable nucleus, a radioactive isotope is created and radioactive decay occurs. Inelastic collisions of neutrons with nuclei create unstable nuclei that later emits a neutron and a gamma ray. Neutrons can also interact elastically with nuclei displacing them from their crystallographic position and therefore creating secondary ionization due to the resulting broken bonds. Due to their lack of electrical charge, neutrons can travel longer distances than alpha or beta particles without interacting with matter.

#### 2.3.2 Detector physics

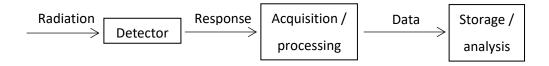

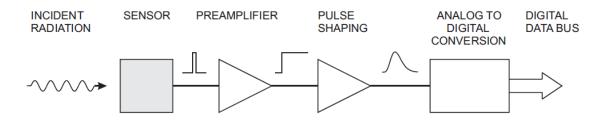

The general model of a radiation detection system is illustrated in Figure 2.4. The incoming radiation reaches the detector, where interactions between radiation and matter produce a response. This response must be acquired and processed in order to extract information about the radiation which interacted with the detector. Finally, the data may be stored and/or analysed to give information about the incident radiation with the detector system.

Figure 2.4 Basic radiation detection system.

Important parameters in a radiation detection system are: the energy resolution, spatial resolution, time resolution, and sensitivity. Depending on the application, a compromise

#### Semiconductor radiation detectors

should be found to choose the best radiation detector system. Many types of radiation detectors exist, depending on the criteria to classify them. Four types of radiation detectors are defined considering their physical composition: Gas-filled detectors, inorganic scintillators, organic scintillators (liquid and plastic) and solid-state detectors, such as semiconductors.

The interaction of radiation with semiconductor materials causes the creation of electron-hole pairs that may be detected as electric signals. For charged particles, ionization may occur along the path of travel by many collisions with the electrons. Photons have first to interact with a target electron, resulting in a photoelectric or Compton effect, or with the semiconductor nucleus, resulting in pair production. In any case, part of the energy absorbed in the semiconductor will be converted into ionization, resulting in the creation of electron—hole pairs) and the rest into phonons, or lattice vibrations, resulting into thermal energy. The fraction of energy converted into electron—hole pair creation is a property of the detector material.

In general, the energy loss rate by particles that pass through a solid,  $\partial E/\partial x$ , reaches a minimum when  $\beta\gamma\approx3.5$ , being  $\beta=v/c$  and  $\gamma=1/\sqrt{1-\beta^2}$  the kinematic constants of the ionizing particle [19]. A minimum ionization particle (MIP) is considered a particle whose mean energy loss rate through matter is close to the its minimum. In the case of silicon, all particles with  $\beta\gamma>3$  are considered MIPs. The most probable number of electron—hole pairs generated by a MIP in 1  $\mu$ m of silicon is 76 and the average is 108 [19].

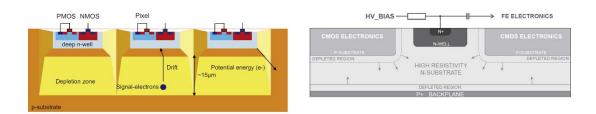

#### 2.4 Semiconductor radiation detectors

Semiconductor radiation detectors are basically ionization chambers. In the simplest configuration, pairs of electrodes are placed in an absorbing medium with an applied voltage. Absorbed radiation liberates charge pairs, which move under the influence of an applied field and induce an electrical current in the external circuit.

Devices made from semiconductors can be used for amplification, switching, energy conversion, sensors, etc. Silicon is the most used semiconductor material in modern industry. Table 2.3 contains some physical properties of silicon.

#### 2.4.1 Principles of semiconductor detectors

The aim of this section is to give a short overview of the basic principles of the semiconductor p-n junction, which is the base of the radiation detectors used in this work. A deeper understanding of the semiconductor principles may be found in [18]-[21].

Solid state materials that feature variable electrical conductivity, depending on external conditions are known as semiconductor materials. The electrical conductivity of a semiconductor material increases with temperature, in contrast to metals. The electrical properties of a semiconductor material may be modified by controlled addition of

#### Radiation detectors

impurities. Therefore, a semiconductor may feature electrical resistance values from  $m\Omega$  up to  $G\Omega$ , corresponding to conductors and insulators respectively, depending on the operational conditions.

| Parameter                   | Symbol             | Unit                               | Value                  |

|-----------------------------|--------------------|------------------------------------|------------------------|

| Atomic number               |                    |                                    | 14                     |

| Relative atomic weight      |                    |                                    | 28.0855                |

| Structure                   |                    |                                    | diamond                |

| Lattice constant            | $a_0$              | Å                                  | 5.4307                 |

| Density                     | ρ                  | gcm <sup>-3</sup>                  | 2.328                  |

| Melting point               | T <sub>m</sub>     | °C                                 | 1414                   |

| Boiling point               | T <sub>b</sub>     | °C                                 | 2355                   |

| Gap energy (300 K)/(0 K)    | Eg                 | eV                                 | (1.124)/(1.170)        |

| Dielectric constant         | ε <sub>r</sub>     |                                    | 11.7                   |

| Intrinsic carrier density   | ni                 | cm⁻³                               | 1.45×10 <sup>-10</sup> |

| Max. electrical field       | E <sub>max</sub>   | Vμm <sup>−1</sup>                  | 30                     |

| Intrinsic resistivity       |                    | kΩ cm                              | 235                    |

| Mobility of electrons       | $\mu_{\mathrm{e}}$ | cm <sup>2</sup> [Vs] <sup>-1</sup> | 1350                   |

| Mobility of holes           | $\mu_{h}$          | cm <sup>2</sup> [Vs] <sup>-1</sup> | 450                    |

| Effective density of states |                    |                                    |                        |

| of the conductance band     | N <sub>c</sub>     | cm <sup>-3</sup>                   | 3.22×10 <sup>19</sup>  |

| of the valence band         | $N_{v}$            | cm <sup>-3</sup>                   | 1.83×10 <sup>19</sup>  |

Table 2.3 Silicon physical properties [20].

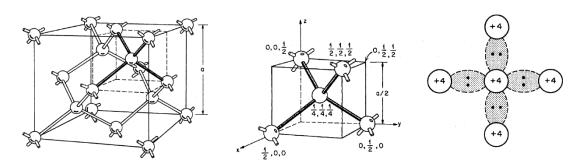

Semiconductors are crystalline materials normally arranged in different crystal lattice types: diamond for silicon and germanium, and zinc blende for gallium arsenide and other semiconductor compounds [19]. Figure 2.5 illustrates the crystal lattice for silicon. Tetrahedron bonds are part of the diamond lattice. In each tetrahedron bond, four close neighbours surround an atom in the diamond lattice. The four valence electrons of the central silicon atom form covalent bonds with the four surrounding silicon atoms.

Figure 2.5 Crystal lattice for silicon. Diamond lattice (left), tetrahedron bond (centre) and its schematic representation (right) [20].

#### *2.4.1.1 Band theory*

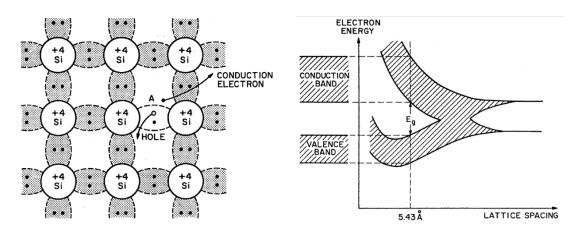

For low temperatures, valence electrons remain bound in their respective tetrahedral lattice. When the temperature of the silicon is increased, thermal vibrations break the covalent bond and a valence electron may become a free electron, leaving behind a free place, called hole, which is filled by a neighbour electron. Both electron and hole are available for electrical conduction. Figure 2.6 describes a free electron production, from the brake of a covalent bond, due to thermal influence.

Overlap of the electron wave functions occurs due to the periodic arrangement of the atoms in the crystal. Besides, the existence of more than one electron in the same energy quantum state is not permitted by the Pauli principle [17]. Therefore, regions of many discrete energy levels are formed, which are known as energy bands. The energy levels formation depends on the lattice spacing [20]. Figure 2.6 also illustrates the electron energy levels for diamond crystal lattices.

Figure 2.6 Schematic representation of electron-hole production due to thermal influence (left) and energy states in diamond crystal lattice dependency on lattice spacing (right) [20].

Two energy bands are defined to describe the electrical behaviour of semiconductors: the valence and conduction bands. The valence band correspond to the electrons bond to their lattice atoms, while the conduction band correspond to the electrons that are detached from their atoms and are free to move to different atoms in the lattice. For silicon, which features a lattice spacing of 5.43 A, the valence and conduction bands are separated by an energy band gap of 1.1 eV (at 300  $^{\circ}$ K), as illustrated in Figure 2.6.

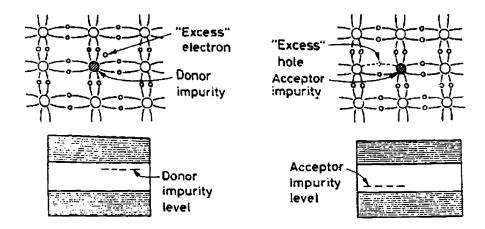

In pure semiconductors, the number of holes equals the number of electrons in the conduction band. This balance can be changed by the introduction of impurity atoms, which have one electron more or one electron less in their valence bands. Trivalent or pentavalent atoms introduced in the silicon lattice would act as impurities, as silicon is tetravalent. These impurities, called also dopants, integrate themselves in the crystal lattice and create a doped semiconductor. Figure 2.7 describes the changes in the semiconductor crystal lattice due to the introduction of dopants.

For silicon, if the dopant is pentavalent, one extra electron remains in a discrete energy level. This discrete energy level is located the energy gap of pure silicon and close to the conduction band. Dopants that introduce electrons in the crystal lattice are called

#### Radiation detectors

donors. Doped silicon with electrons as majority charge carries is known as n-type silicon.

For silicon, if the dopant is trivalent, no enough electrons will be available to fill the valence band and one extra hole remains in a discrete energy level. The discrete energy level created by the trivalent impurity is also in the energy gap of pure silicon, but it is close to the valence band. Dopants that create extra holes in the crystal lattice are called acceptors. Doped silicon with holes as majority charge carries is known as p-type silicon.

Figure 2.7 Addition of dopants to a semiconductor crystal lattice. Donor dopants (left) and Acceptor dopants (right) [18].

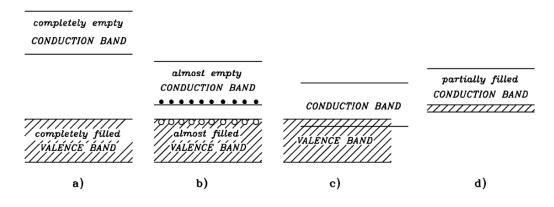

A useful way to visualize the difference between conductors, insulators and semiconductors is to plot the available energy levels for electrons in the materials. Figure 2.8 describes the schematic representation of the band theory for conductors, insulators and semiconductors.

Figure 2.8 Typical energy band levels representation. Insulators (a), semiconductors (b) and metals (c, d) [20].

Crucial to the conduction process is the existence of electrons in the conduction band level. In insulators, the electrons in the valence band are separated by a large gap from the conduction band. In conductors like metals, the valence band overlaps the conduction band. In semiconductors a small gap between the valence and conduction bands exist, which can be overcome due to thermal or other excitation types. With such a small gap, the presence of a small percentage of a doping material may increase the conductivity dramatically.

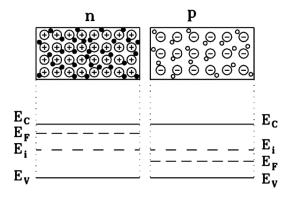

The application of band theory to n-type and p-type semiconductors allows to explain the extra levels added by the impurities. In n-type silicon, electron energy levels are located near the top of the band gap; therefore, they may be easily excited into the conduction band. In p-type silicon, extra holes with energies in the band gap allow excitation of valence band electrons; therefore, leaving mobile holes in the valence band. An important parameter in the band theory is the Fermi level, which corresponds to the energy level where the probability of occupancy of one energy state is 50%. For pure silicon, the Fermi level is located in the middle of the energy gap and it is equal to the intrinsic energy level. For doped silicon, the Fermi level is shifted, close to the conduction band for donor dopants and close to the valence band for acceptor dopants. Figure 2.9 illustrates the energy bands for n-type and p-type semiconductors, where  $E_c$ ,  $E_v$ ,  $E_i$  and  $E_f$  refer to the energy levels on the conduction band, valence band, intrinsic material and the Fermi level respectively.

Figure 2.9 Energy bands for n-type and p-type semiconductors [20].

#### 2.4.1.2 PN junction

When p-type and n-type silicon are connected to each other, a p-n junction is formed. The electrical properties of the p-n junction are different compared to the electrical properties of each doped silicon alone.

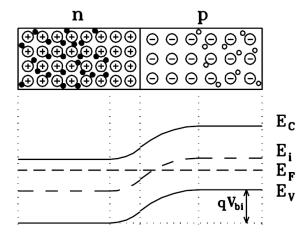

When a p-n junction is formed, some of the electrons in the n-type region diffuse to the p-type region and fill up holes in the p-type region. The equivalent process occurs from the p-type region to the n-type region, as holes from the p-type region capture electrons in the n-type region. This recombination of electrons and holes creates a depletion region, and a space charge is built up, generating an electric field across the junction. This electric field produces a drift of the electrons and holes in the direction opposite to the diffusion process, reaching an equilibrium between both processes. This dynamic equilibrium remains unless an external voltage is applied on the junction. In thermal equilibrium, the total potential difference in the space charge region is built-in voltage,  $V_{\rm bi}$ .

$$V_{bi} = \frac{kT}{e} \log \left( \frac{N_a N_d}{n_i^2} \right)$$

Equation 2.6

where k is the Boltzmann constant, T is the temperature is Kelvin degrees, e is the electron charge,  $n_i$  is the intrinsic carrier concentration, while  $N_a$  and  $N_d$  are the acceptor and donor concentrations respectively. Typical values for  $V_{bi}$  are in the order of hundreds of millivolts.

Figure 2.10 illustrates a p-n junction in thermal equilibrium, non-flat energy band levels correspond to the space charge region, except for the Fermi level that is flat in all regions. The depletion region extends predominantly in the lighter doped zone.

Figure 2.10 P-N junction in thermal equilibrium [20].

When an external voltage is applied to each side of the junction, the conditions for thermal equilibrium are no longer applicable and the junction built-in voltage, which prevents the flow of electrons across the junction will be reduced or incremented, depending on the sign of the applied external voltage.

Specifically, current will flow in one direction when forward biased but not in the other, when reverse biased, creating the basic diode. This non-reversing behaviour comes from the nature of the charge transport processes in the two types of materials.

#### 2.4.1.3 Reverse bias

Having one electrode on the n-type silicon and another electrode on the p-type silicon, allows to apply voltage on the p-n junction and bias it. An applied voltage on reverse bias restricts the flow of electrons and holes across the junction. For conduction in the device, electrons from the n-type region must move to the junction and combine with holes in the p-type region. A reverse voltage drives the electrons away from the junction, preventing conduction and increasing the volume of the depleted region. An equivalent argument can be applied to holes.

Considering the dopant concentration in the n-type silicon to be much higher than the doping concentration in the p-type silicon, the depletion region mostly extends into the p-type zone. A one-dimensional model describes the depletion width as:

$$w \approx \sqrt{\frac{2\epsilon V_b}{eN}}$$

Equation 2.7

where  $\epsilon$  is the dielectric constant,  $V_b$  is the reverse bias voltage applied and N represents the less dominant doping concentration, in our case the p-type doping concentration. As the depletion region is free of mobile charge, a capacitor is formed between the two electrodes:

$$C = \epsilon \frac{A}{w} \approx A \sqrt{\frac{eN\epsilon}{2V_b}}$$

Equation 2.8

where A is the area of the p-n junction. Equation 2.7 and Equation 2.8 describe the behaviour of the p-type silicon, which is lightly doped compared to the n-type silicon, in a PN junction in reverse bias, when the reverse bias voltage is higher than the junction built-in voltage, which is the case for the typical operation conditions of silicon semiconductor sensors in this work.

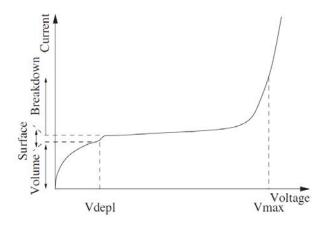

The reverse biased p-n junction offers an attractive radiation detector because charge carriers created in the depletion region are able to be quickly and efficiently collected. The width of the depletion region is related to the active volume of the detector and is modified in sensors by modifying the reverse bias voltage. The variable active volume of semiconductor junctions is unique among radiation detectors and normally is considered as an advantage. The capacitance of a partially depleted sensor changes with the applied voltage. Therefore, stable operation is obtained when full depletion is reached and the detection volume is maximized. The reverse voltage needed to fully deplete the sensor volume is known as the full depletion voltage. For a silicon sensor with a thickness equal to "t", the full depletion voltage increases as the thickness of the sensor also increases.

$$V_{full\_dep} = t^2 \frac{eN}{2\epsilon} - V_{bi}$$

Equation 2.9

For a charged particle moving through a silicon sensor, the energy loss and hence the signal will increase with sensor thickness. Minimum ionizing particles (MIPs) average about 80 electron-hole pairs per micrometre length path in fully depleted silicon [22]. A charged particle traversing the sensor forms charge pairs along the track with a radial extent of the order of micrometres. The signal is formed when the liberated charge carriers move in the electric field, which changes the induced charge on the sensor electrodes.

A reverse biased p-n junction is ideally non-conducting. Nevertheless, small current flows through the junction when an external voltage is applied. This current is known as leakage current and has several sources. The most important contributor of the leakage current are surface channels [17]. It depends on the surface chemistry and sensor fabrication contaminants. The other contributors of the leakage current are the movement of minority carriers and the thermally generated electron-hole pairs.

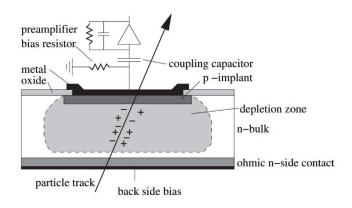

The simplest geometry possible is sketched in Figure 2.11, called a pad sensor. A large area n+ implantation is performed in a p-bulk. When applying a negative bias to the backside, which has an ohmic contact provided by a p implantation and an aluminium layer, the depletion zone starts to grow from the junction into the bulk. Signal charge liberated by an ionizing particle will be collected by the field and can be detected by both electrodes of the diode. If possible, one connects the preamplifier to the electrode on ground potential.

Figure 2.11 Schematic cross section of a simple silicon pad sensor [23].

# 2.4.2 Detector limits: Radiation damage

Semiconductor devices are affected by two basic radiation damage mechanisms: displacement and ionization damage. A deeper study can be found in [21].

For displacement damage, incident radiation displaces silicon atoms from their lattice sites. The resulting defects alter the electrical characteristics of the crystal. Displacement damage depends on the nonionizing energy loss, i.e. energy and momentum transfer to lattice atoms, which depends on the mass and energy of the incident quanta. A simple measure as for ionizing radiation is not possible, so that displacement damage must be specified for a specific particle type and energy. Displacement damage manifests itself in three important ways: Formation of mid-gap states, which facilitate the transition of electrons from the valence to the conduction band. In depletion regions this leads to a generation current, i.e. an increase in the current of reverse-biased p-n junctions. In forward biased junctions or no depleted regions mid-gap states facilitate recombination, i.e. charge loss. States close to the band edges facilitate trapping, where charge is captured and released after some time. A change in doping characteristics, such as effective donor or acceptor density, is also produced.

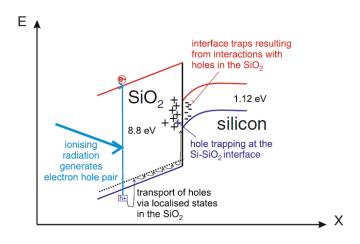

In case of ionization damage, the energy absorbed by ionization in insulating layers, usually SiO<sub>2</sub>, liberates charge carriers, which diffuse or drift to other locations where they are trapped. This leads to unintended concentrations of charge and, as a consequence, parasitic fields. Ionization effects depend primarily on the absorbed

#### Semiconductor radiation detectors

energy, independent of the type of radiation. At typical incident energies ionization is the dominant absorption mechanism, so ionization damage is proportional to energy absorption per unit volume. Since the charge liberated by a given dose depends on the absorber material, the ionizing dose must be referred to a specific absorber. Ionization effects are determined by interface traps, oxide trapped charge, the mobility of trapped charge.

#### 2.4.2.1 Bulk damage

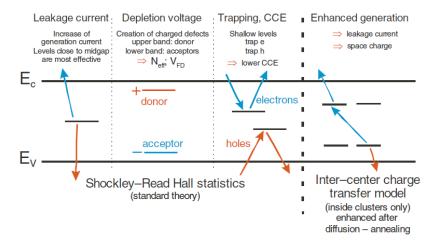

This damage to the lattice is created by traversing particles that create ionization and also may interact with atomic bodies and create defects. All relevant defect levels related to bulk damage and produced by radiation are located in the forbidden energy gap. Figure 2.12 describes the defect locations and their effects. Mid-gap levels are mainly responsible for dark current generation, according to the Shockley–Read–Hall statistics [19], and decreasing the charge carrier lifetime. Donors in the upper half of the band gap and acceptors in the lower half can contribute to the effective space charge. Deep levels, with trapping times larger than the detector electronics peaking time, are detrimental. Charge is "lost", the signal decreases and the charge collection efficiency is degraded. Defects can trap electrons or holes. The theory of inter-centre charge transfer model [19] states that combinations of the different defects in so-called defect clusters additionally enhance the effects.

Change of the full depletion voltage is expected, due to creation of mainly additional acceptor levels, which result in change of the effective doping concentration.

Figure 2.12 Defect level locations and their effects [19].

#### 2.4.2.2 Annealing

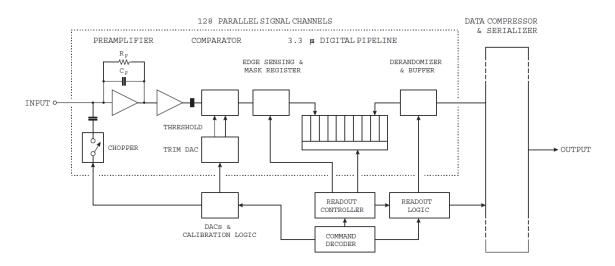

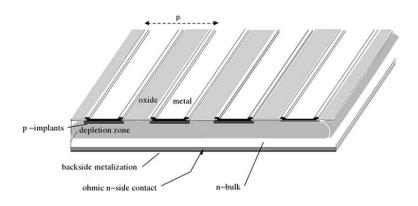

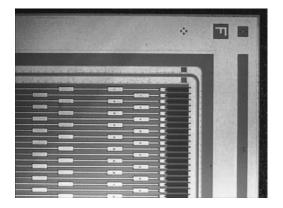

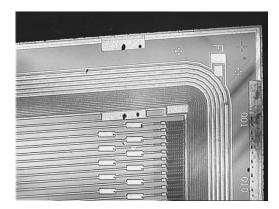

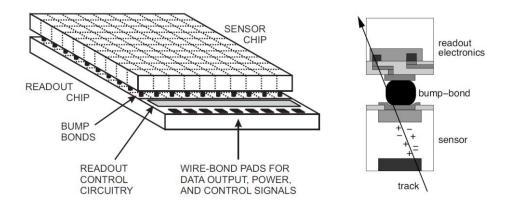

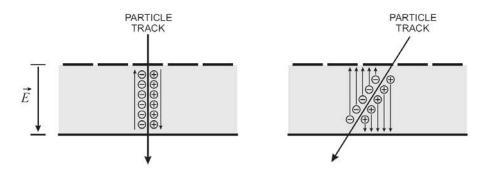

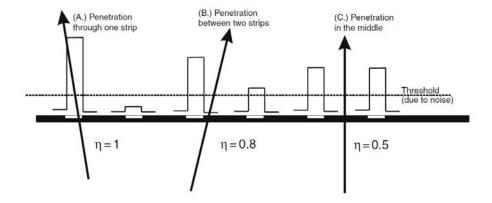

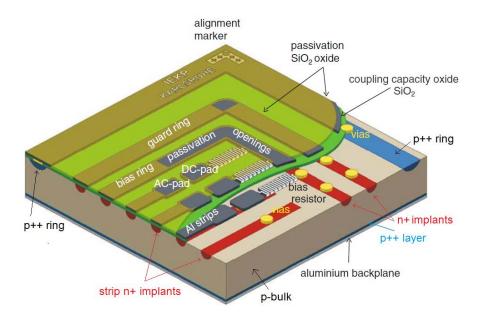

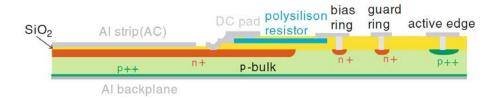

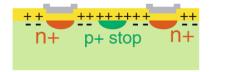

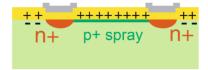

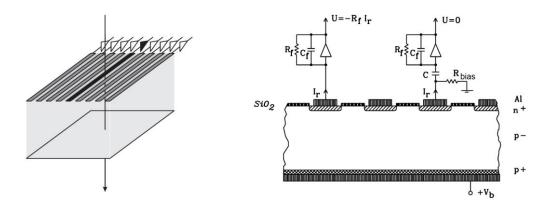

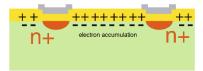

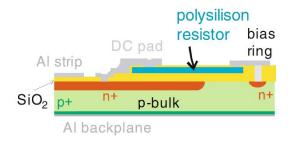

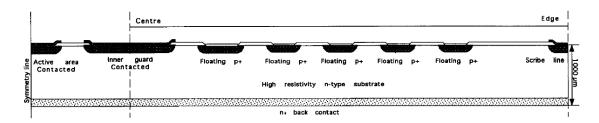

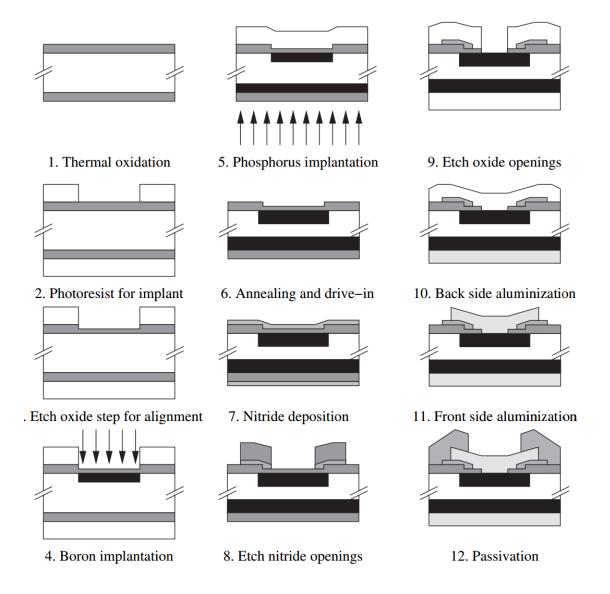

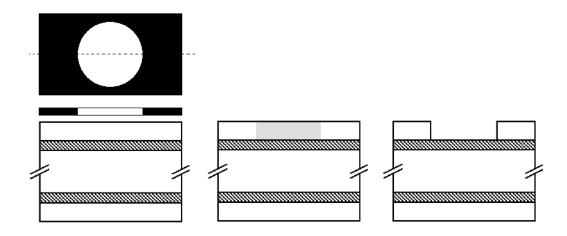

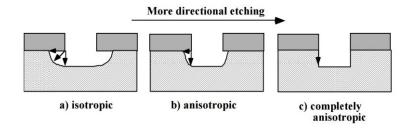

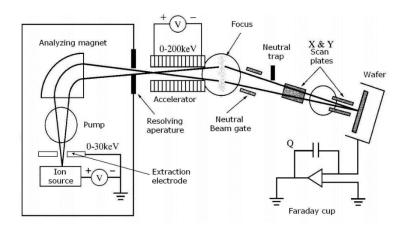

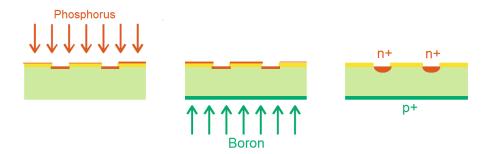

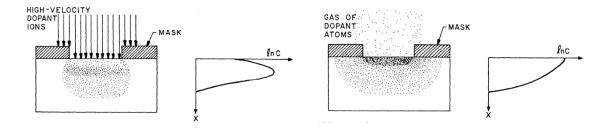

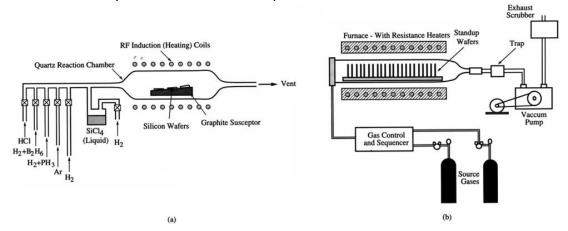

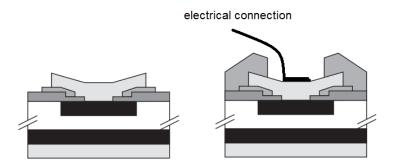

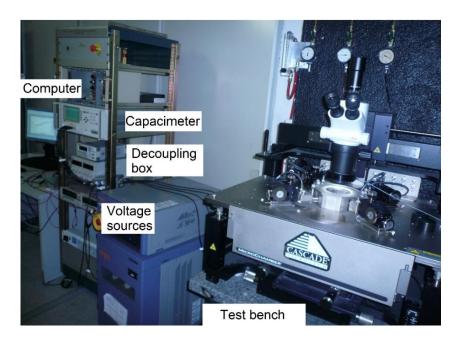

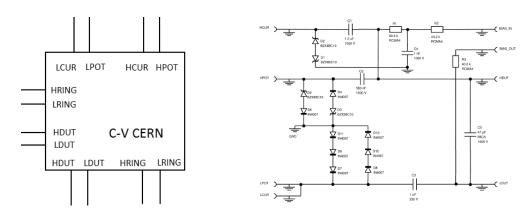

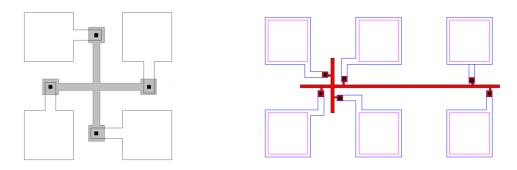

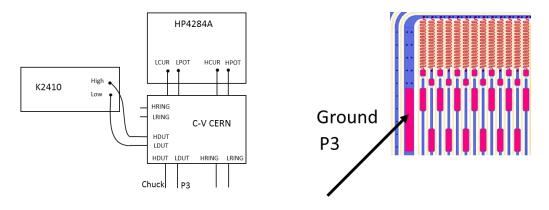

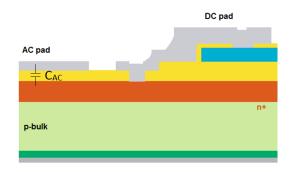

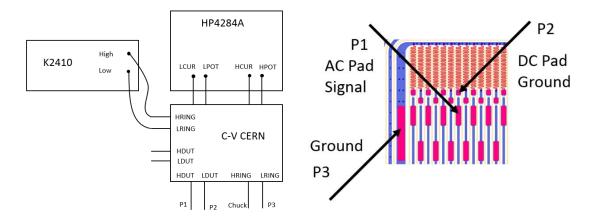

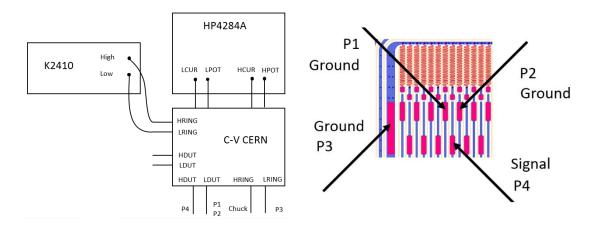

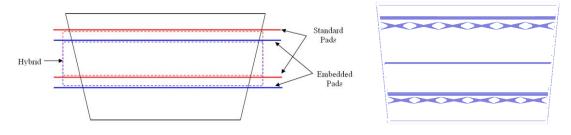

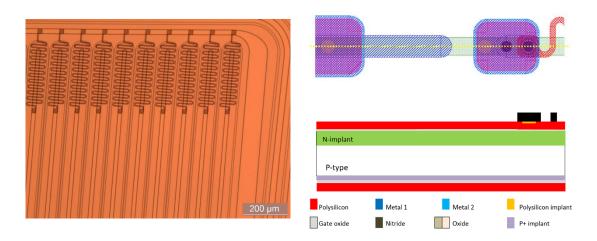

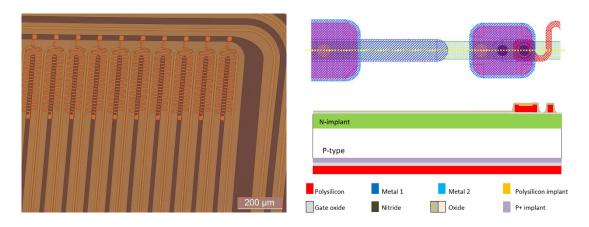

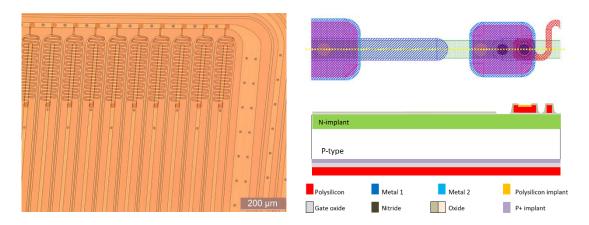

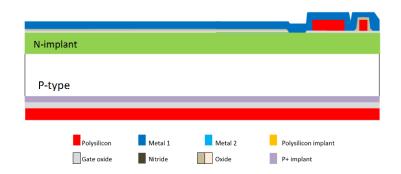

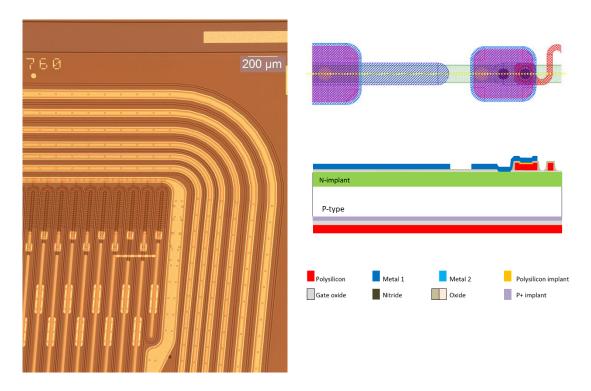

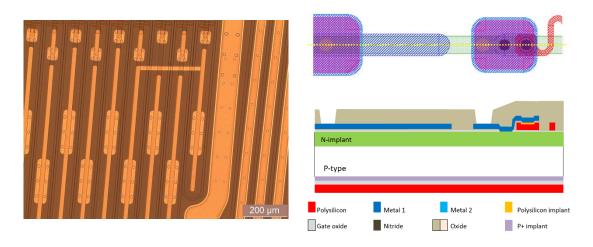

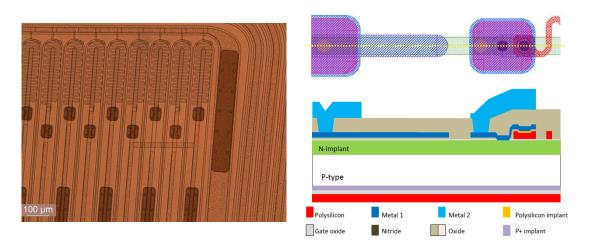

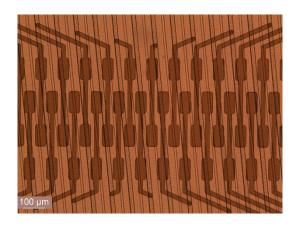

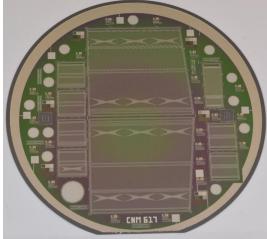

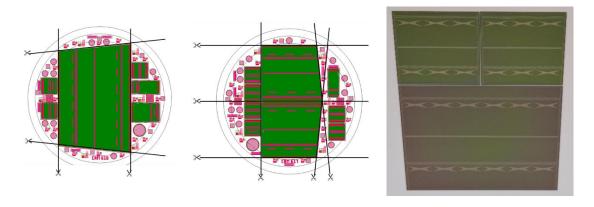

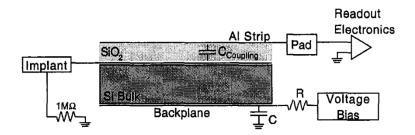

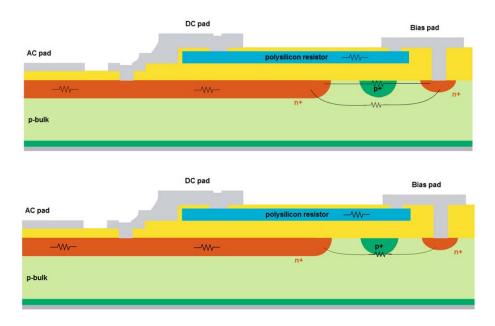

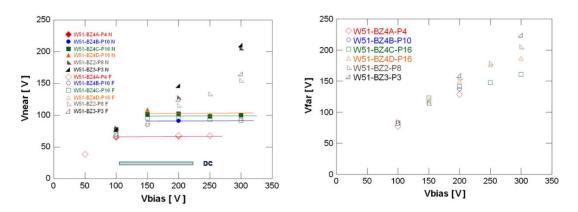

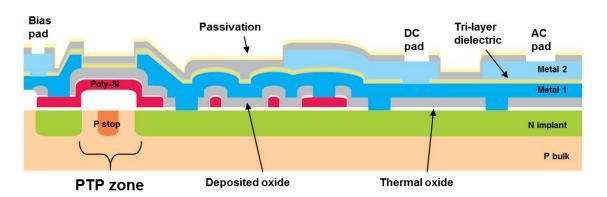

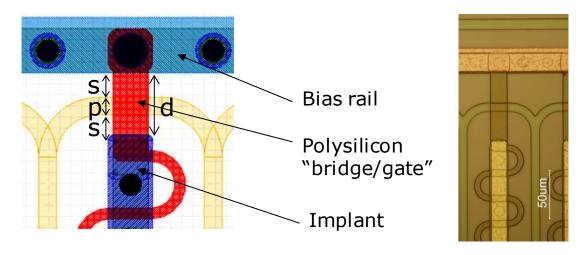

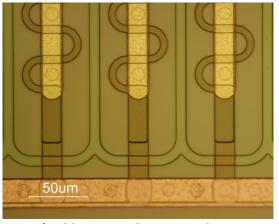

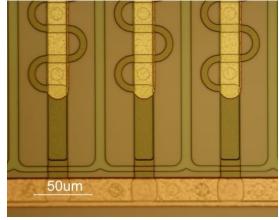

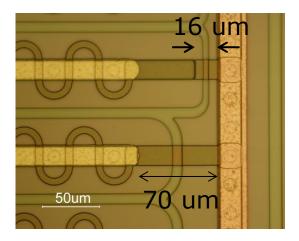

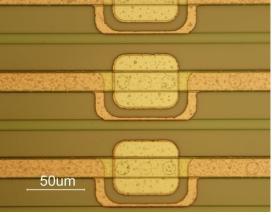

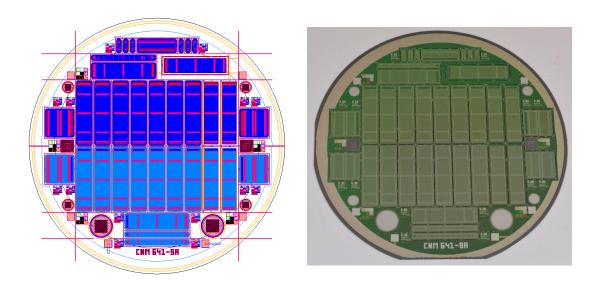

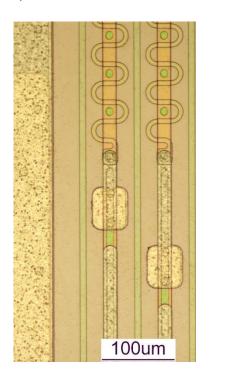

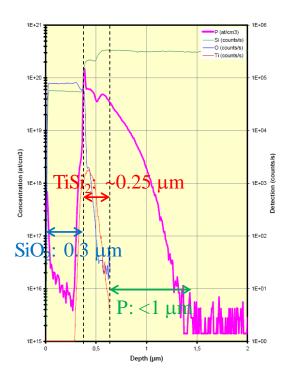

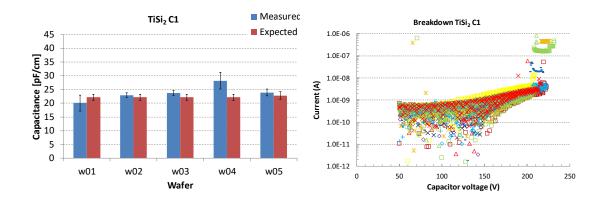

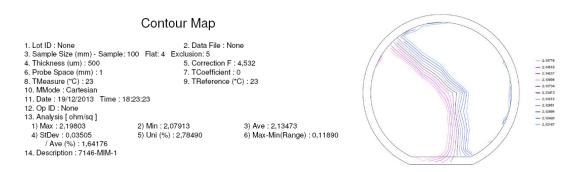

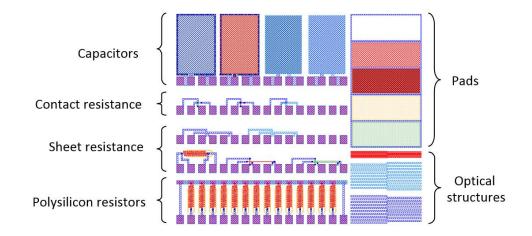

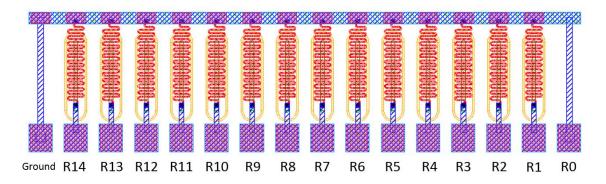

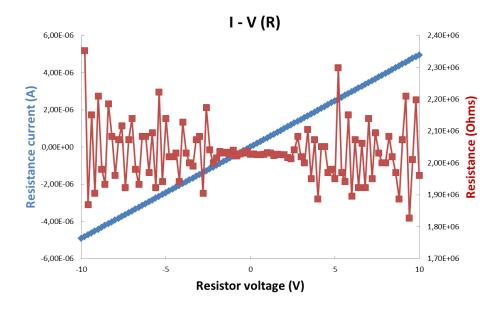

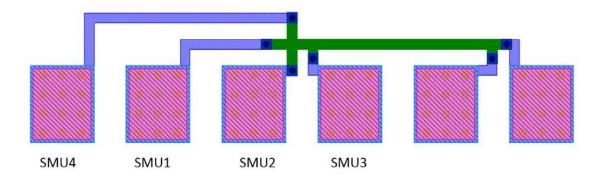

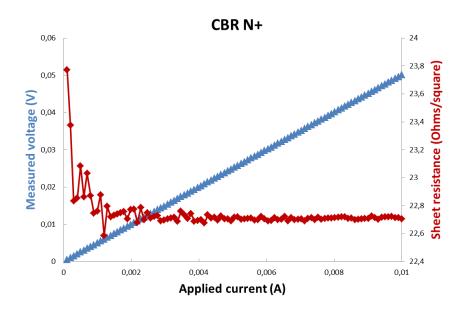

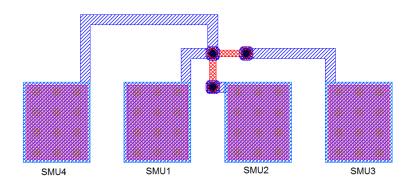

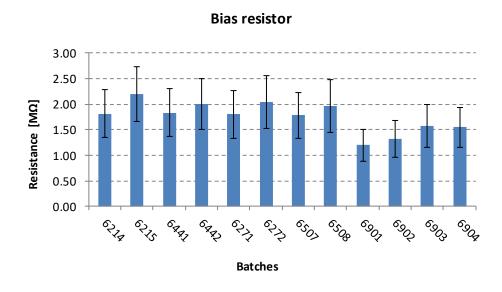

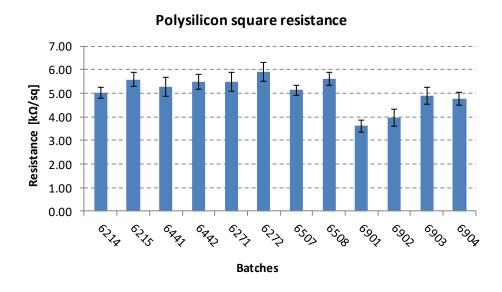

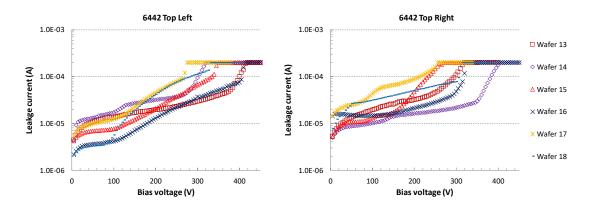

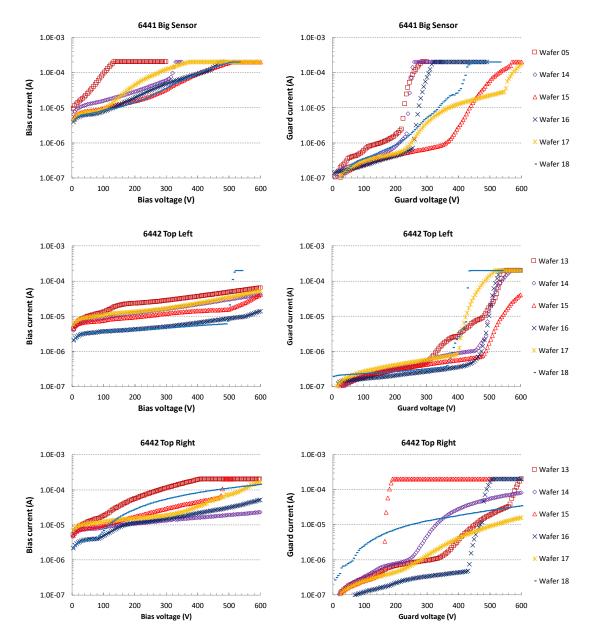

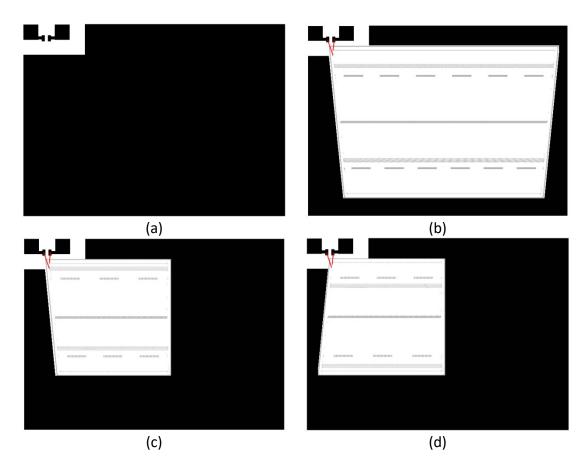

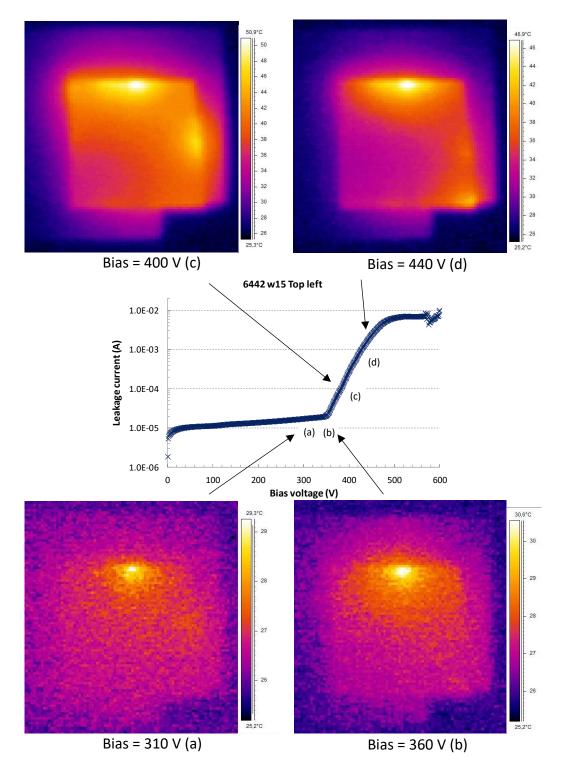

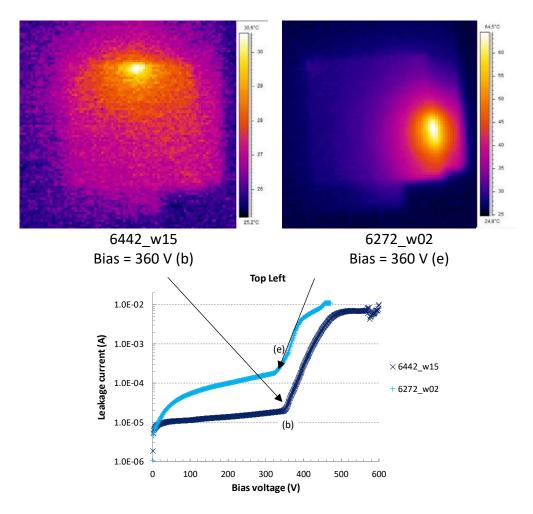

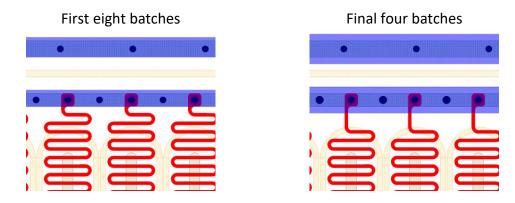

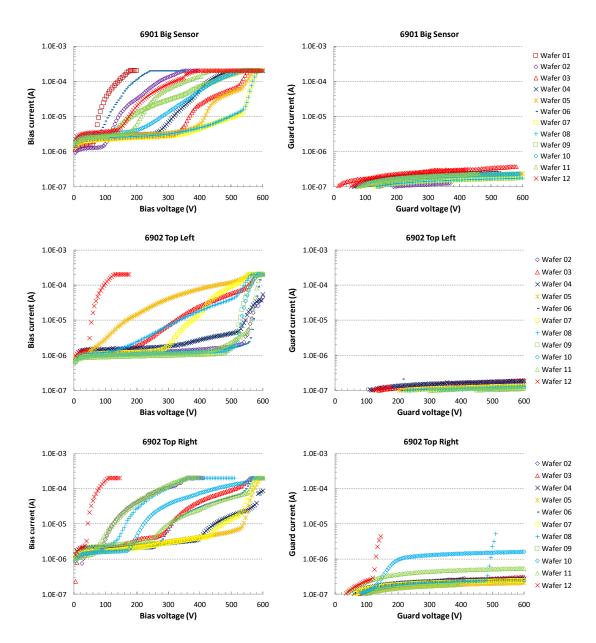

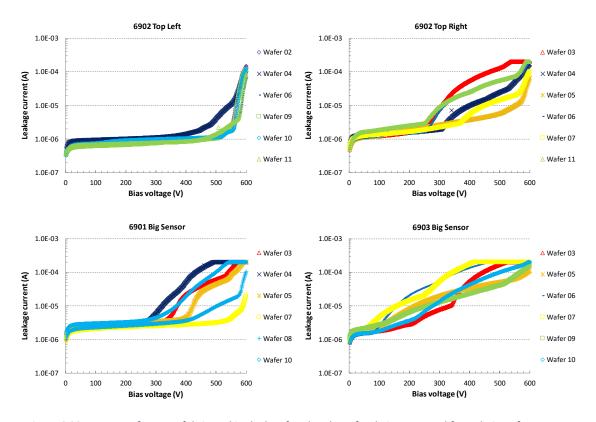

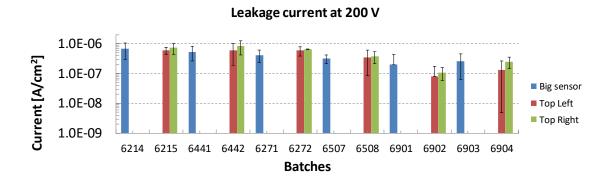

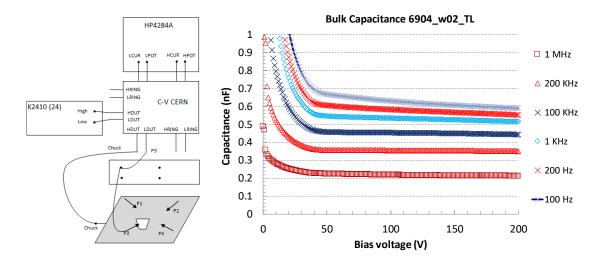

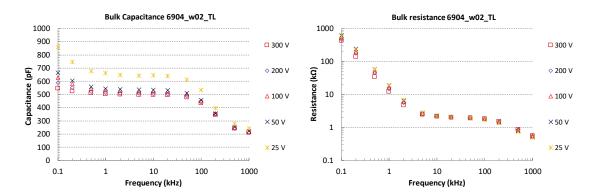

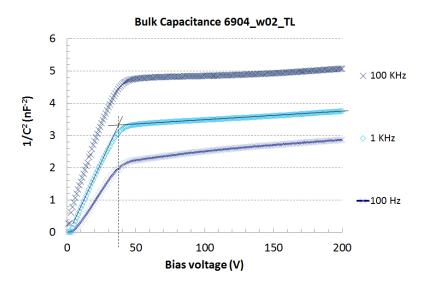

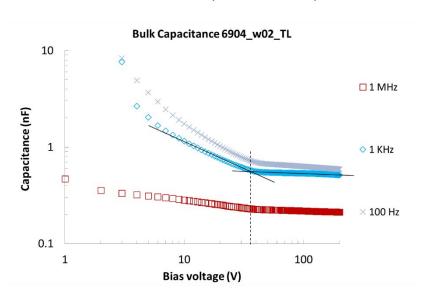

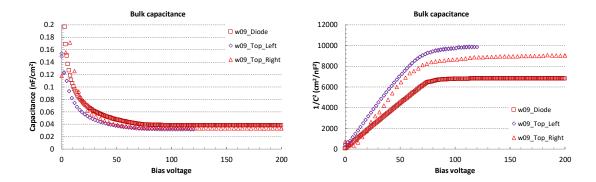

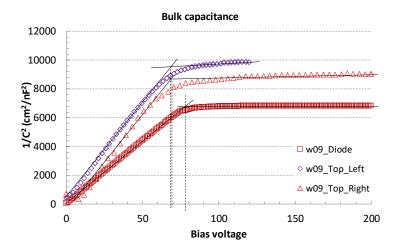

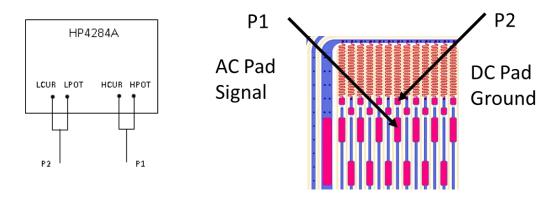

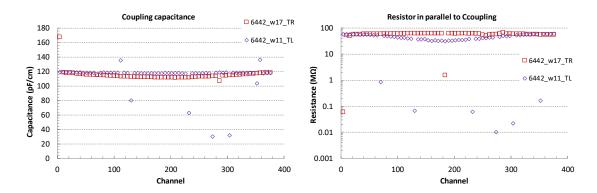

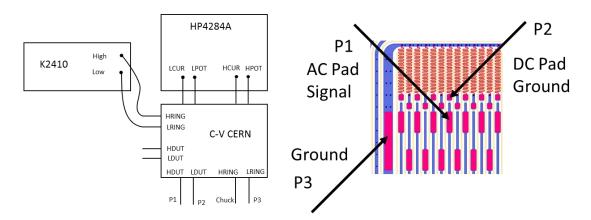

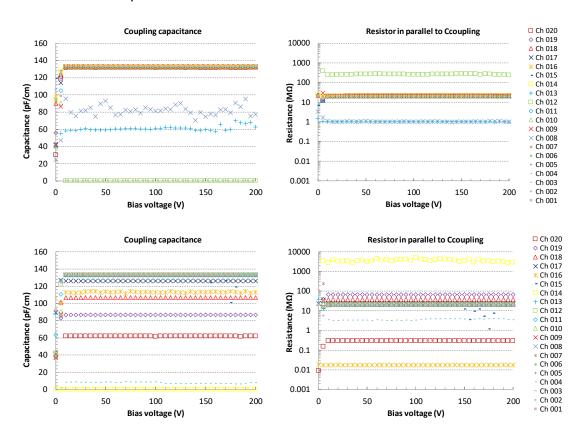

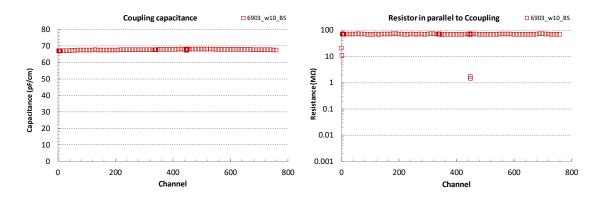

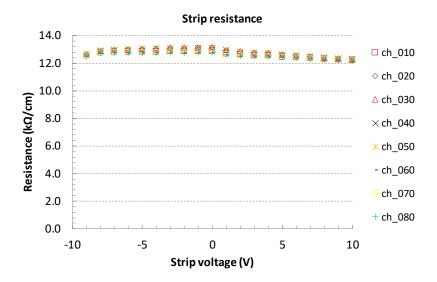

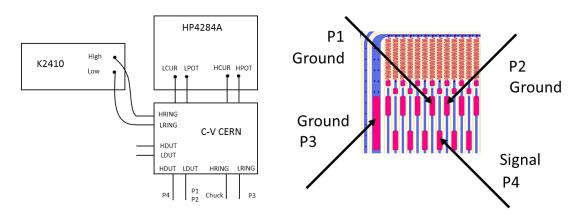

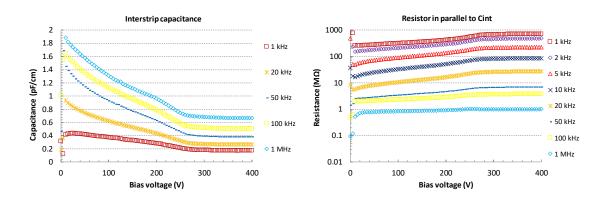

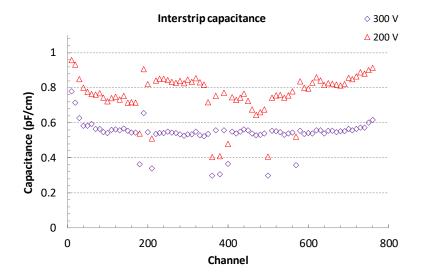

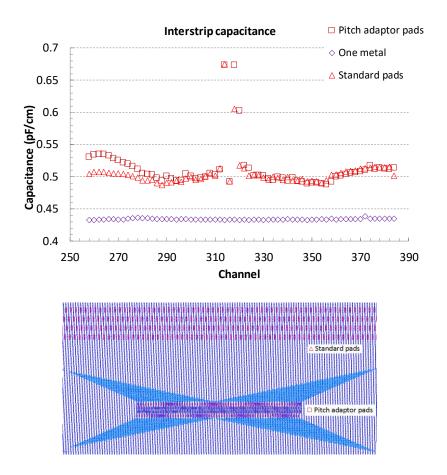

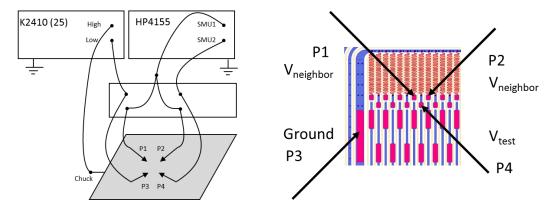

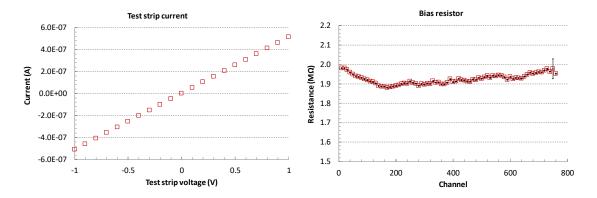

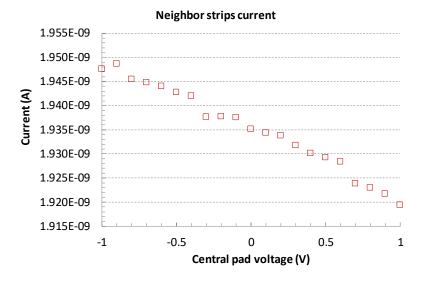

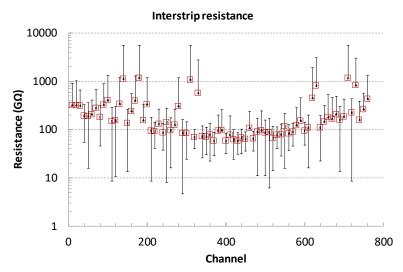

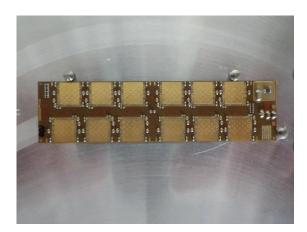

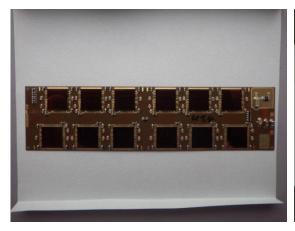

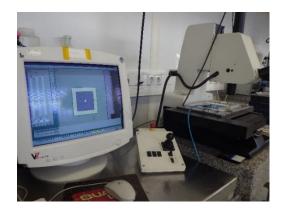

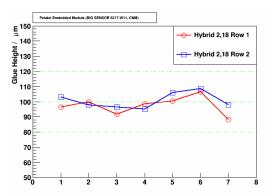

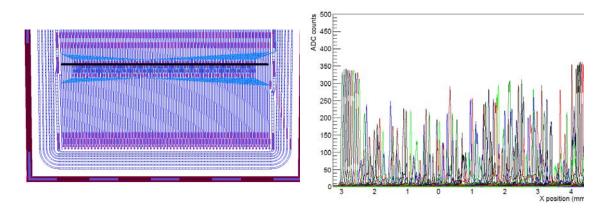

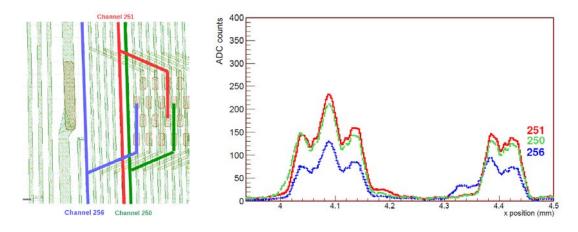

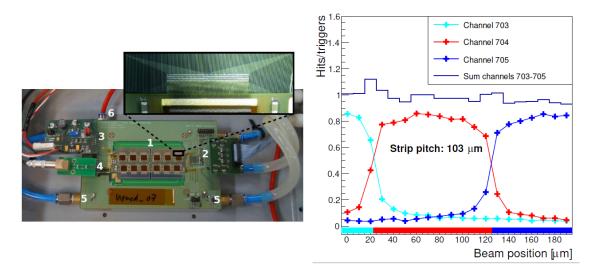

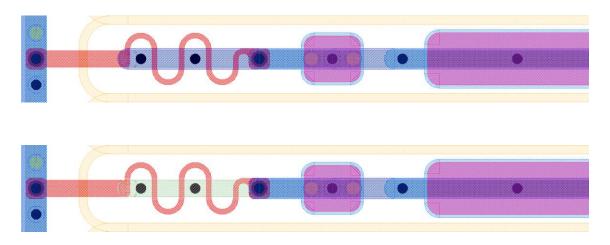

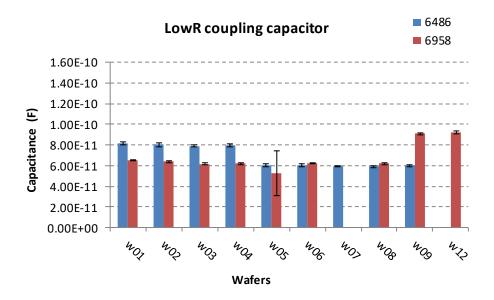

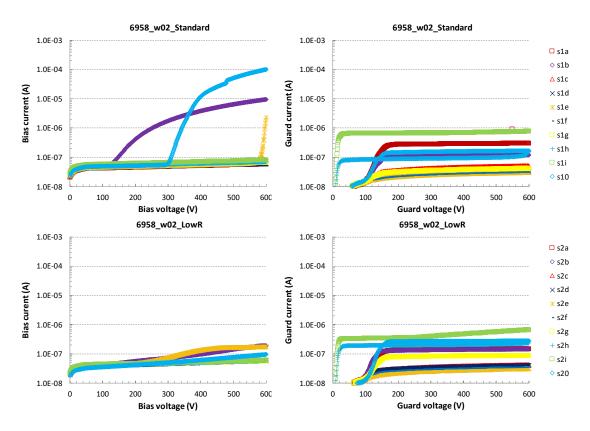

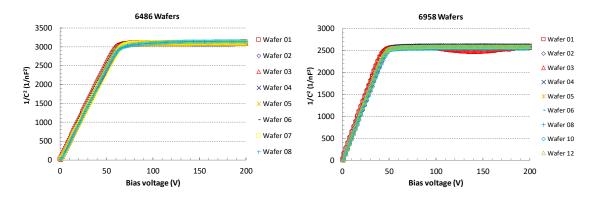

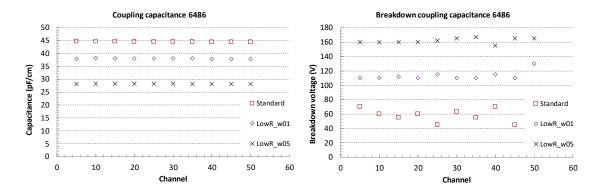

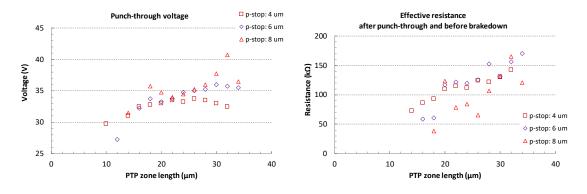

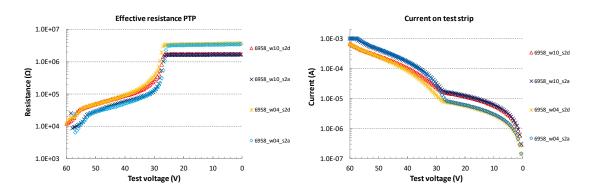

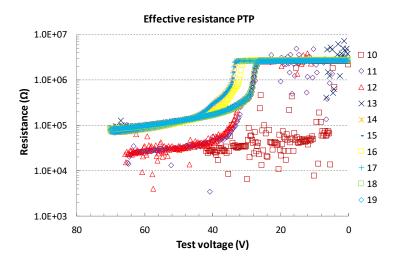

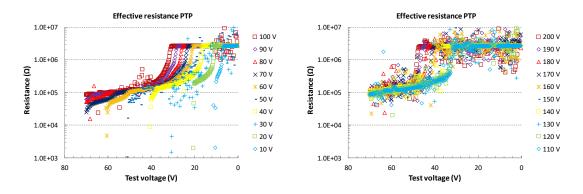

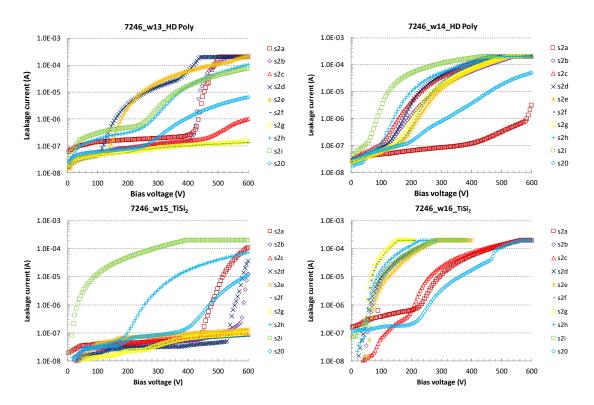

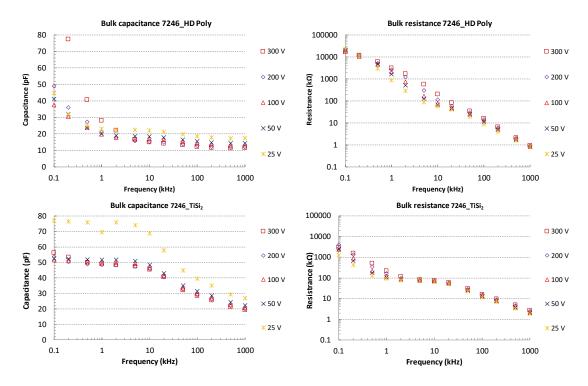

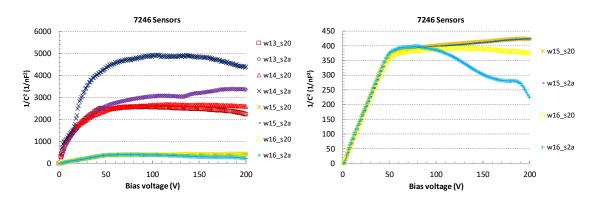

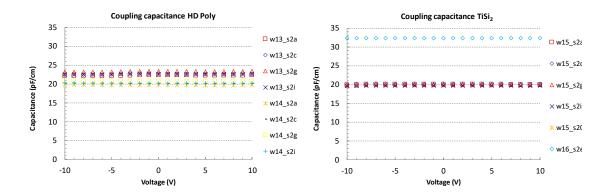

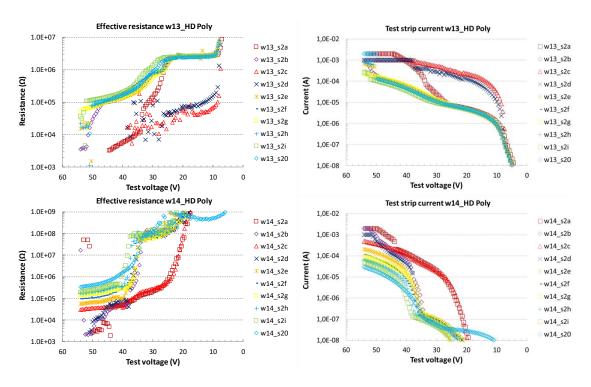

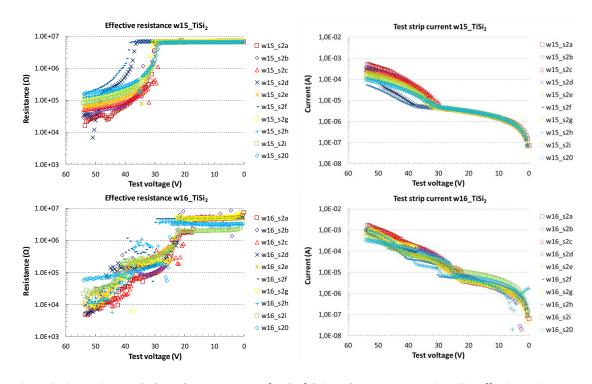

Defects created by crossing particles, like interstitials and vacancies, are highly mobile at temperatures higher than 150 °K. Defect diffusion may occur due to Frenkel pair recombination, vacancy and interstitial combination, both being short-range and highly mobile processes and therefore happen with a shorter time constant, or combination of more complex defects with a longer time constant [21]. The whole process is called