**ADVERTIMENT.** L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús establertes per la següent llicència Creative Commons: http://cat.creativecommons.org/?page\_id=184

**ADVERTENCIA.** El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons: http://es.creativecommons.org/blog/licencias/

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: https://creativecommons.org/licenses/?lang=en

# Novel CMOS Devices for High Energy Physics and Medical Applications

Author:

Fabian Alexander Förster

Directors:

Sebastian Grinstein Stefano Terzo

Ph.D. Thesis **June 2020**

### Abstract

High Energy Physics (HEP) experiments at particle colliders probe our understanding of the structure and dynamics of matter. In order to advance the field, the accelerator systems are periodically upgraded to higher energies and luminosities. Experiments have to keep up, by improving their detector instrumentation.

Silicon pixel detectors play a critical role in HEP experiments. Thanks to their excellent position resolution, compactness, speed and radiation hardness, they enable particle track reconstruction in high radiation environments like hadron colliders. In turn, their performance allows excellent track impact parameter resolution, a key ingredient for secondary vertex identification and jet b-tagging.

Currently the standard pixel detector consists of a segmented sensor, in which each pixel is connected to a readout channel of an Application-Specific Integrated Circuit (ASIC) through a complicated, and expensive, technique called bump bonding.

An alternative approach to hybrid pixel devices are monolithic detectors, which combine the particle sensing and the signal processing tasks in the same substrate. These kinds of detectors developed in the CMOS process have been used in the past, but only relatively recently radiation hard devices based on this technology have been proposed.

In this thesis a first full size prototype of a monolithic detector developed in the High Voltage CMOS (HV-CMOS) technology is investigated as a pixel device for the outer layers of the future upgrade ATLAS tracker, which is located in the Large Hadron Collider (LHC) at CERN.

Besides the application of this technology in HEP experiments, the detection of soft X-ray photons is also investigated in one matrix in one of the HV-CMOS pixel detectors. Lastly, the usage of CMOS devices for the detection of Near-Infrared (NIR) photons with Avalanche Photodiode (APD) is explored.

### Resumen

El Large Hadron Collider (LHC) del European Organization for Nuclear Research (CERN) de Ginebra es tancarà entre el 2025 i el 2027 per tal de ser actualitzat a High Luminosity LHC (HL-LHC). Això augmenta la lluminositat nominal de les col·lisions protó-protó fins a  $5 \cdot 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> amb un centre d'energia de massa de 14 TeV.

El detector ATLAS és un dels dos experiments de propòsit general del LHC i haurà de ser actualitzat per satisfer els nous requisits a causa de la major lluminositat. Una de les novetats previstes és la substitució del detector interior per un silici complet Inner Tracker (ITk) amb granularitat més fina i amb major duresa de la radiació. La tecnologia comercial High Voltage CMOS (HV-CMOS) es va considerar una opció rendible per a la capa exterior del detector de píxels ITk. En aquesta tesi, s'investiguen dues iteracions de HV-CMOS detectors de píxels.

A més de l'aplicació d'aquesta tecnologia en experiments High Energy Physics (HEP), la detecció de fotons de raigs X suaus també s'investiga en una matriu en un dels HV-CMOS detectors de píxels. Per últim, s'explora l'ús de CMOS dispositius per a la detecció de Near-Infrared (NIR) fotons amb Avalanche Photodiode (APD).

# Contents

| $\mathbf{A}$ | bstra        | ct      |                                              | i   |  |  |

|--------------|--------------|---------|----------------------------------------------|-----|--|--|

| $\mathbf{R}$ | esum         | en      |                                              | iii |  |  |

| 1            | Introduction |         |                                              |     |  |  |

| 2            | Soli         | d Stat  | e Detectors                                  | 5   |  |  |

|              | 2.1          | Semice  | onductor Physics                             | 5   |  |  |

|              |              | 2.1.1   | The Band Model                               | 5   |  |  |

|              |              | 2.1.2   | The p-n junction                             | 8   |  |  |

|              | 2.2          | Silicon | n Detectors                                  | 11  |  |  |

|              |              | 2.2.1   | Interaction of Charged Particles with Matter | 13  |  |  |

|              |              | 2.2.2   | Interaction of Photons with Matter           | 15  |  |  |

|              |              | 2.2.3   | Signal Formation                             | 17  |  |  |

|              |              | 2.2.4   | Detector Applications                        | 18  |  |  |

|              | 2.3          | Radia   | tion Damage                                  | 20  |  |  |

|              |              | 2.3.1   | The NIEL Scaling Hypothesis                  | 21  |  |  |

|              |              | 2.3.2   | Impact on Sensor Performance                 | 22  |  |  |

| 3            | $Th\epsilon$ | ATLA    | AS Experiment                                | 27  |  |  |

|              | 3.1          | The L   | arge Hadron Collider                         | 27  |  |  |

|              | 3.2          | Overv   | iew of the ATLAS Experiment                  | 29  |  |  |

|              | 3.3          | Inner   | Detector                                     | 30  |  |  |

<u>vi</u> CONTENTS

|   |                                 | 3.3.1                                                         | Pixel Detector                                                                                                                                                                                                                                      | 32                                                 |

|---|---------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|   |                                 | 3.3.2                                                         | SemiConductor Tracker                                                                                                                                                                                                                               | 33                                                 |

|   |                                 | 3.3.3                                                         | Transient Radiation Tracker                                                                                                                                                                                                                         | 34                                                 |

|   | 3.4                             | Calori                                                        | meters                                                                                                                                                                                                                                              | 34                                                 |

|   |                                 | 3.4.1                                                         | Electromagnetic Calorimeter                                                                                                                                                                                                                         | 35                                                 |

|   |                                 | 3.4.2                                                         | Hadronic Calorimeter                                                                                                                                                                                                                                | 36                                                 |

|   |                                 | 3.4.3                                                         | Forward Calorimeter                                                                                                                                                                                                                                 | 36                                                 |

|   | 3.5                             | Muon                                                          | Spectrometer                                                                                                                                                                                                                                        | 37                                                 |

|   |                                 | 3.5.1                                                         | Monitored Drift-Tube Chambers                                                                                                                                                                                                                       | 37                                                 |

|   |                                 | 3.5.2                                                         | Cathode Strip Chambers                                                                                                                                                                                                                              | 38                                                 |

|   |                                 | 3.5.3                                                         | Resistive Plate Chambers                                                                                                                                                                                                                            | 38                                                 |

|   |                                 | 3.5.4                                                         | Thin Gap Chambers                                                                                                                                                                                                                                   | 39                                                 |

|   | 3.6                             | Magne                                                         | et System                                                                                                                                                                                                                                           | 39                                                 |

|   | 3.7                             | Inner                                                         | Detector Upgrade for the HL-LHC                                                                                                                                                                                                                     | 39                                                 |

|   |                                 |                                                               |                                                                                                                                                                                                                                                     |                                                    |

| 4 | H35                             | Demo                                                          | chip                                                                                                                                                                                                                                                | 43                                                 |

| 4 |                                 | 5Demo                                                         | -                                                                                                                                                                                                                                                   | <b>43</b>                                          |

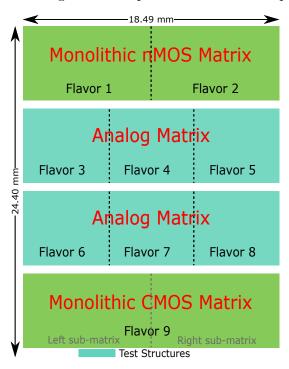

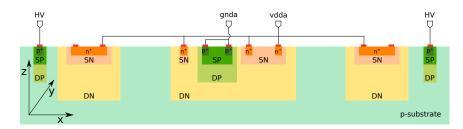

| 4 | <b>H35</b>                      | Descri                                                        | ption of the Chip                                                                                                                                                                                                                                   | 43                                                 |

| 4 |                                 |                                                               | -                                                                                                                                                                                                                                                   |                                                    |

| 4 |                                 | Descri                                                        | ption of the Chip                                                                                                                                                                                                                                   | 43                                                 |

| 4 |                                 | Descri                                                        | ption of the Chip                                                                                                                                                                                                                                   | 43<br>45                                           |

| 4 |                                 | Descri 4.1.1 4.1.2                                            | ption of the Chip                                                                                                                                                                                                                                   | 43<br>45<br>46                                     |

| 4 |                                 | Descri 4.1.1 4.1.2 4.1.3 4.1.4                                | ption of the Chip                                                                                                                                                                                                                                   | 43<br>45<br>46<br>46                               |

| 4 | 4.1                             | Descri<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Reado           | ption of the Chip                                                                                                                                                                                                                                   | 43<br>45<br>46<br>46<br>47                         |

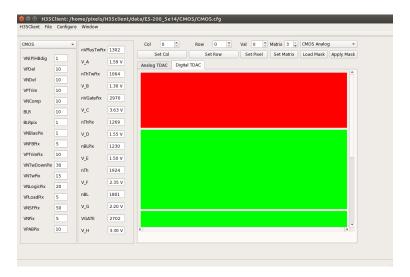

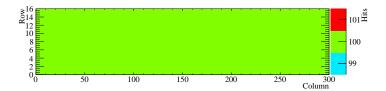

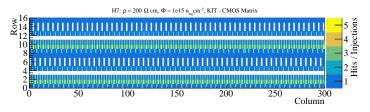

| 4 | 4.1                             | Descri 4.1.1 4.1.2 4.1.3 4.1.4 Reado Sample                   | ption of the Chip  The Monolithic nMOS Matrix  First Analog Matrix  Second Analog Matrix  The Monolithic CMOS Matrix  out Architecture (Column-Drain)                                                                                               | 43<br>45<br>46<br>46<br>47<br>48                   |

| 4 | 4.1<br>4.2<br>4.3               | Descri 4.1.1 4.1.2 4.1.3 4.1.4 Reado Sample Curren            | ption of the Chip  The Monolithic nMOS Matrix  First Analog Matrix  Second Analog Matrix  The Monolithic CMOS Matrix  out Architecture (Column-Drain)  es and Irradiations                                                                          | 43<br>45<br>46<br>46<br>47<br>48<br>49             |

| 4 | 4.1<br>4.2<br>4.3<br>4.4        | Descri 4.1.1 4.1.2 4.1.3 4.1.4 Reado Sample Currer Edge       | ption of the Chip  The Monolithic nMOS Matrix  First Analog Matrix  Second Analog Matrix  The Monolithic CMOS Matrix  out Architecture (Column-Drain)  es and Irradiations  nt-Bias (I-V) Characterization                                          | 43<br>45<br>46<br>46<br>47<br>48<br>49             |

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5 | Descri 4.1.1 4.1.2 4.1.3 4.1.4 Reado Sample Currer Edge Teado | ption of the Chip  The Monolithic nMOS Matrix  First Analog Matrix  Second Analog Matrix  The Monolithic CMOS Matrix  out Architecture (Column-Drain)  es and Irradiations  out-Bias (I-V) Characterization  Transient Current Technique (Edge-TCT) | 43<br>45<br>46<br>46<br>47<br>48<br>49<br>49<br>51 |

<u>CONTENTS</u> vii

|   | 4.9  | Threshold Scan               | 9 |

|---|------|------------------------------|---|

|   | 4.10 | Threshold Calibration        | 2 |

|   |      | 4.10.1 Fluorescence Spectrum | 4 |

|   |      | 4.10.2 Experimental Setup    | 5 |

|   | 4.11 | Test Beams                   | 9 |

|   |      | 4.11.1 Tested Modules        | 1 |

|   |      | 4.11.2 Track Reconstruction  | 2 |

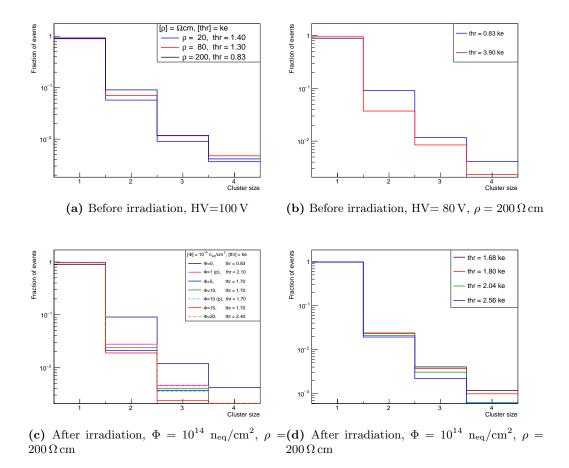

|   | 4.12 | Cluster Sizes                | 3 |

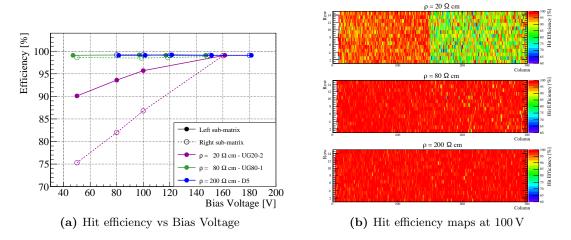

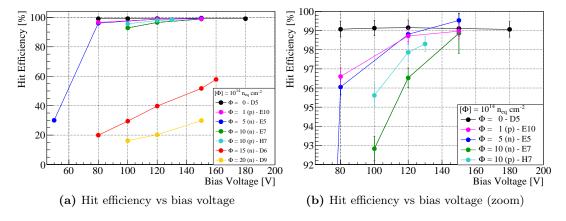

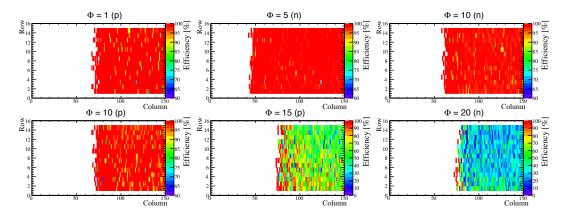

|   | 4.13 | Efficiency                   | ŝ |

|   |      | 4.13.1 Before Irradiation    | ŝ |

|   |      | 4.13.2 After Irradiation     | 7 |

|   | 4.14 | Noise occupancy              | Э |

|   | 4.15 | Summary and Outlook          | 2 |

| _ | T T0 |                              | _ |

| 5 |      | Chip 88                      |   |

|   | 5.1  | Description of Chip          | 5 |

|   | 5.2  | Samples and Irradiations     | 3 |

|   | 5.3  | Electrical Characterization  | 3 |

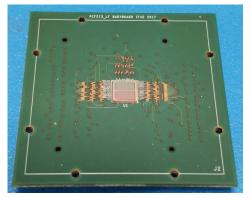

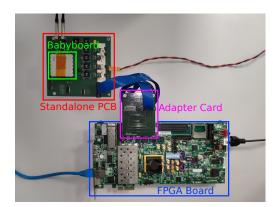

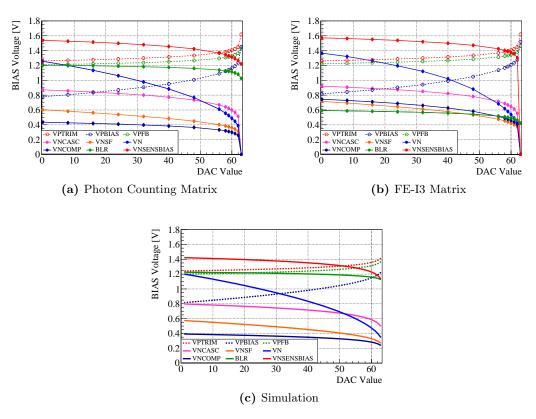

|   | 5.4  | Readout System         90    | ) |

|   | 5.5  | FE-I3 Matrix                 | 1 |

|   |      | 5.5.1 Analog Scan            | ĉ |

|   |      | 5.5.2 Threshold Scan         | 7 |

|   |      | 5.5.3 Tuning of Threshold    | 3 |

|   |      | 5.5.4 Time over Threshold    | ) |

|   |      | 5.5.5 Source Scan            | 2 |

|   |      |                              | 2 |

|   |      | 5.5.6 Discriminator Study    |   |

|   | 5.6  | 5.5.6 Discriminator Study    | 5 |

|                  |        | 5.7.1   | FE-I3 Matrix                  | 107 |

|------------------|--------|---------|-------------------------------|-----|

|                  |        | 5.7.2   | Photon Counting Matrix        | 108 |

| 6                | Ava    | lanche  | e Photodiodes                 | 109 |

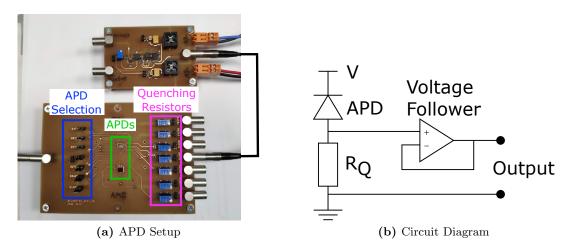

|                  | 6.1    | Descri  | ption of Chip                 | 110 |

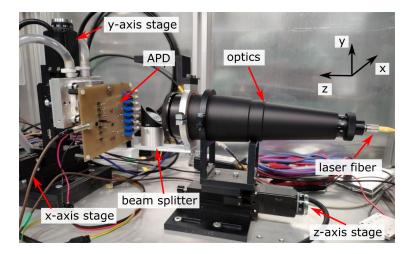

|                  |        | 6.1.1   | Experimental Setup            | 112 |

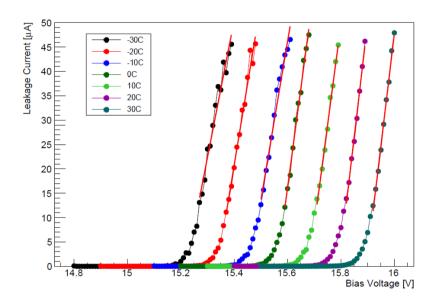

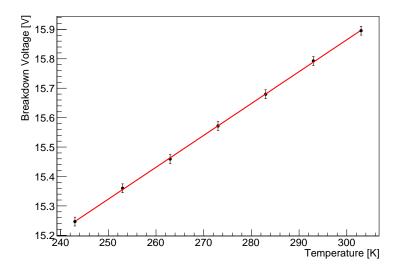

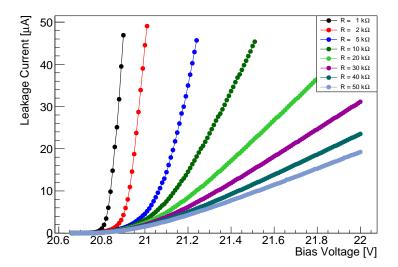

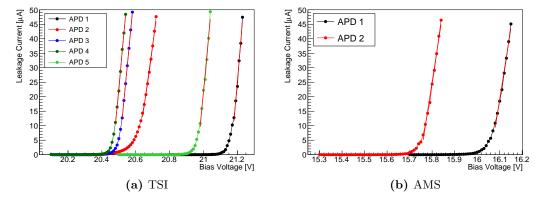

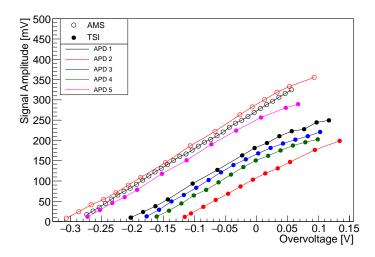

|                  | 6.2    | Break   | down Voltage                  | 114 |

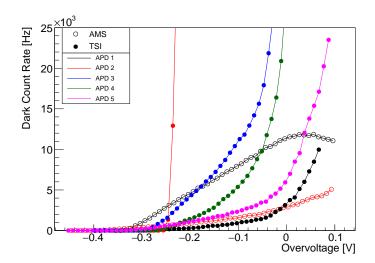

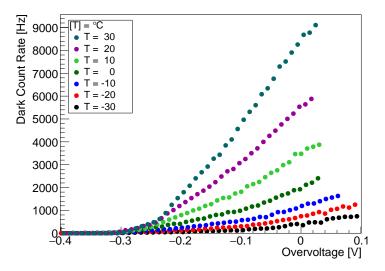

|                  | 6.3    | Dark    | Count Rate                    | 120 |

|                  | 6.4    | Laser   | Studies                       | 122 |

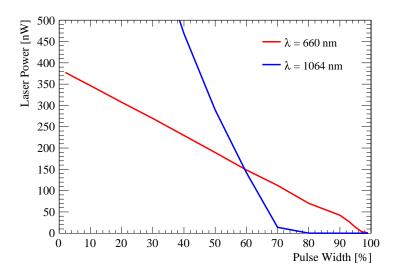

|                  |        | 6.4.1   | Laser Sources                 | 123 |

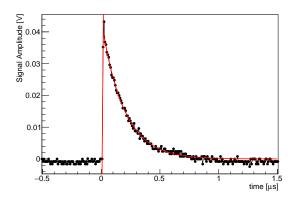

|                  |        | 6.4.2   | Readout                       | 125 |

|                  |        | 6.4.3   | Movable Stages                | 125 |

|                  |        | 6.4.4   | Pointing the Laser on the APD | 125 |

|                  |        | 6.4.5   | Laser Focus                   | 127 |

|                  |        | 6.4.6   | Count Rates                   | 127 |

|                  | 6.5    | Summ    | nary                          | 129 |

| 7                | Cor    | nclusio | n and Outlook                 | 131 |

| Bi               | ibliog | graphy  |                               | 140 |

| $\mathbf{A}_{0}$ | ckno   | wledge  | ements                        | 151 |

# Chapter 1

# Introduction

Segmented silicon detectors are nowadays widely used in High Energy Physics (HEP) experiments to provide a precise measurements of the position of charged particles. Several layers of these detectors allow a reconstruction of the particle trajectory, thus playing a critical role to understand the dynamics of the physics processes under study. Initially, strip detectors were used in collider and fixed target experiments. However, due to their superior position resolution, pixel detectors have become the norm in high multiplicity environments. The standard pixel detector is made of two parts, connected pixel by pixel through solder bumps, called a hybrid device: A sensor in which the signal is created by the charged particle and a readout chip that amplifies and digitizes the signal and sends the hit information to the data acquisition system. The first pixel matrix was used in the European Organization for Nuclear Research (CERN) Omega spectrometer in 1993 and had a planar sensor with  $75 \,\mu\text{m} \times 500 \,\mu\text{m}$  pixels connected to a readout chip produced in the Complementary Metal–Oxide–Semiconductor (CMOS) technology, which allowed to see particle tracks for the first time in the WA94 experiment [1].

Hybrid devices are still the most common pixel detectors today, due to the possibility to optimize the performance of the sensor and readout chip independently.

An example of the state of the art is the RD53A prototype chip with a pixel size of 50 µm × 50 µm for the planned A Toroidal LHC ApparatuS (ATLAS) and Compact Muon Solenoid (CMS) inner tracker upgrades for the High Luminosity LHC (HL-LHC) period. However, this approach is cost intensive and limits the pixel size to about 30 to 40 µm due to the size of the interconnecting solder bumps. A solution for both of these limitations is producing both sensor and readout chip on the same substrate, thus called a monolithic detector. Monolithic CMOS detectors are those fabricated in commercial CMOS foundries. CMOS detectors were already used in the Heavy Flavor Tracker of the STAR experiment [2] in 2014 and are being installed in the A Large Ion Collider Experiment (ALICE) Inner Tracking System [3] in 2020. In these devices the charge collection is through thermal diffusion which is both a slow and non radiation hard process, thus not suitable for a hadron collider experiment like ATLAS. A critical advancement of the CMOS technology was proposed in 2006 [4]. By using a High Voltage CMOS (HV-CMOS) process, it is possible to produce a depleted region in the CMOS detector bulk, enabling the charge collection by drift, resulting in a fast and more radiation hard technology. Furthermore, compared to standard hybrid devices, the price is lower due to the lack of the need of hybridization, the fact that only one substrate is needed and that a commercial process is used to fabricate the CMOS device (less expensive than specific ones needed for sensor fabrication).

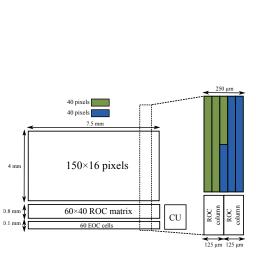

In this thesis the feasibility of this technology for the upgrade of the ATLAS Inner Tracker (ITk) is investigated through the first full size depleted monolithic CMOS prototype for ATLAS, the H35Demo, with a pixel size of  $50 \,\mu\text{m} \times 250 \,\mu\text{m}$ . Its characterization is presented after an introduction to solid state detectors (chapter 2) and the ATLAS experiment (chapter 3). A consequent development is the LF2 chip, that has a reduced pixel size of  $50 \,\mu\text{m} \times 50 \,\mu\text{m}$  and is characterized in chapter 5. The HV-CMOS technology is also being investigated for applications outside of HEP. The LF2 chip has a second matrix that is dedicated to detect soft X-ray photons,

which is also presented in this chapter. Finally, chapter 6 focuses on the usage of CMOS devices for Near-Infrared (NIR) photon detection in the form of Avalanche Photodiodes (APDs).

# Chapter 2

# Solid State Detectors

### 2.1 Semiconductor Physics

#### 2.1.1 The Band Model

Solid materials with a crystal lattice have discrete energy levels in which electrons are confined. These energy levels are called bands. Due to the Pauli exclusion principle, each band can only be filled by a finite number of electrons. At low temperatures, the lowest energetic bands are fully filled, while bands above a certain energy are not occupied.

The highest energetic band that is fully filled is called valence band, while the next higher energetic level, that is either partially filled or empty, is called conduction band. If the conduction band is partially filled, the electrons are free to move in the crystalline lattice and the solid is called a conductor. Otherwise the energy gap between the bands  $E_g = E_C - E_V$  either defines the material as a semiconductor or an insulator. Insulators are usually defined by an energy gap larger than  $3 \,\mathrm{eV}$ , while all materials with a lower energy gap are called semiconductors [5]. Silicon, a widely used material for particle detection, has an energy band gap of  $E_g = 1.12 \,\mathrm{eV}$ ,

though 3.6 eV are needed to create an e/h pair by ionizing radiation as described in subsection 2.2.1.

When an electron is excited from the valence to the conduction band, either through thermal or external excitation, it leaves a hole in the valence band, that acts as a particle with positive charge and can freely move. Thus, both electrons and holes contribute to the charge carrier concentration in the material.

In general, the concentration of electrons in the conduction band can be calculated by:

$$n = \int_{E_C}^{\infty} g_e(E) f(E) dE \tag{2.1}$$

where  $g_e(E)$  is the density of states and f(E) is the Fermi-Dirac distribution, integrated from the minimum energy level of the conduction band  $E_C$  to infinity. The concentration of holes p can be calculated similarly, by integrating the energy levels from zero to the energy of maximum energy level in the valence band  $E_V$ :

$$p = \int_0^{E_V} g_h(E) f(E) dE \tag{2.2}$$

The Fermi-Dirac distribution used both in the electron and hole calculation is given by:

$$f(E) = \frac{1}{1 + e^{(E - E_F)/(k_B T)}}$$

(2.3)

where  $k_B$  is the Boltzmann constant, T is the absolute temperature, and  $E_F$  is the Fermi energy which in an intrinsic semiconductor (i.e. without doping) is laying approximately in the middle of the energy gap:

$$E_F \sim \frac{E_C - E_V}{2} \tag{2.4}$$

The density of states for both electrons and holes can be calculated by considering them to be able to move freely in an infinite quantum well (box potential). Solving this potential leads to the following density of states:

$$g_e(E) = \frac{(2m_n)^{3/2}}{2\pi^2\hbar^3} \sqrt{E - E_C} \text{ with } E \ge E_C$$

(2.5)

$$g_h(E) = \frac{(2m_p)^{3/2}}{2\pi^2\hbar^3} \sqrt{E_V - E} \text{ with } E \le E_V$$

(2.6)

where  $m_n$  and  $m_p$  are the effective masses of electrons and holes (For silicon at  $T = 300 \,\mathrm{K}$ :  $m_n = 1.09 \,m_e$  and  $m_p = 1.15 \,m_e$ , with  $m_e$  being the rest mass of the electron), and  $\hbar$  is the reduced Planck constant. Using the density of states and the Fermi-Dirac distribution, Equation 2.1 and Equation 2.2 can be integrated to yield the electron and hole concentrations:

$$n = 2\left(\frac{m_n k_B T}{2\pi\hbar^2}\right)^{3/2} e^{-(E_C - E_F)/(k_B T)} = N_C e^{-(E_C - E_F)/(k_B T)}$$

(2.7)

$$p = 2\left(\frac{m_p k_B T}{2\pi\hbar^2}\right)^{3/2} e^{-(E_F - E_V)/(k_B T)} = N_V e^{-(E_F - E_V)/(k_B T)}$$

(2.8)

$N_C$  and  $N_V$  are called the effective density of states in the conduction and valence band. Multiplying both the density for electrons and holes gives:

$$np = n_i^2 = N_C N_V e^{-E_g/k_B T} (2.9)$$

where  $n_i$  is the intrinsic charge carrier concentration. This assumes  $n=p=n_i$  for intrinsic semiconductors. Since, as mentioned before,  $E_g(300\,\mathrm{K})=1.12\,\mathrm{eV}$ , a typical value for  $n_i$  is  $1.5\cdot 10^{10}\,\mathrm{cm}^{-3}$ . For example, in a typical volume (pixel) of  $100\,\mathrm{\mu m}\times 100\,\mathrm{\mu m}$  with a thickness of  $300\,\mathrm{\mu m}$  the charge carrier already present in the cell is already  $4.5\cdot 10^4\,e^-/h^+$  pairs. This number is comparable to the charge created from a minimum ionizing particle (mip) (see subsection 2.2.1) which is  $3.2\cdot 10^4\,e^-/h^+$  pairs.

For particle detection, the signal should be much higher than the intrinsic charge carrier concentration. However, the charge carrier concentration of silicon (and other semiconductor materials) can be changed by adding impurities to the crystal structure (called doping) and thus improve the behavior in order to detect particles, as it will be described in the following subsection.

#### 2.1.2 The p-n junction

Doping consists of introducing atoms in a semiconductor material of an element with more valence electrons (n-type) or more holes (p-type). For silicon, the doping elements are:

- *n-type*: Elements from group V of the periodic table like phosphorus (P) have one more valence electron than silicon, thus providing an extra electron in the conduction band. Such impurities are called *donors*.

- p-type: Elements from group III of the periodic table like boron (B) have one valence electron less and thus traps electrons from the valence band and creates a hole. Such impurities are called acceptors.

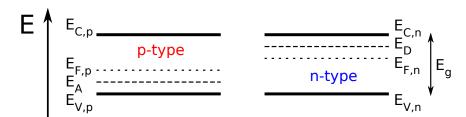

Acceptors/donors add an energy level that is slightly above/below the valence/conduction band, which is called  $E_A/E_D$ , as seen in Figure 2.1.

**Figure 2.1:** Energy levels for p-type (left) and n-type (right) silicon. In the p-type silicon, another energy level  $E_A$  slightly above the valence band energy is added, while in the n-type silicon an energy level  $E_D$  slightly below the conduction band energy is added. The Fermi energy  $E_F$  is close to the middle of the band gap and shifted towards the energy level introduced by the doping.

When p-doped and an n-doped region of a semiconductor are in contact, a p-n junction is formed. The free electrons from the n-doped region and the holes from the

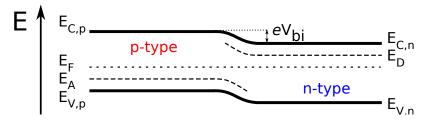

p-doped region diffuse to the opposite region and recombine with the opposite carriers. This creates a small region that is almost free of charge carriers, called *depletion* zone. Since the depletion zone is surrounded by donors and acceptors that did not recombine, an electrical field is present across the junction, which is characterized by a built-in voltage  $V_{bi}$ , shown in Figure 2.2. The width of the depletion zone can be expressed in a one-dimensional approximation as:

$$d = \sqrt{\frac{2\epsilon}{e} \frac{N_A + N_D}{N_A N_D} V_{bi}} \approx \sqrt{\frac{2\epsilon}{e N_{D/A}} V_{bi}} \text{ if } N_A \gg N_D \text{ or } N_A \ll N_D$$

(2.10)

Where  $\epsilon$  is the dielectric constant,  $N_D$  and  $N_A$  are the dopant concentration of donors and acceptors. In the last step it was assumed that one doping concentration is much higher than the other, which is usually the case. In order to increase the depletion zone, and thus allow a larger signal to detect particles (see subsection 2.2.1), an additional external reverse bias  $(V_{bias})$  can be applied. This increases the size of the depletion zone to:

$$d = \sqrt{\frac{2\epsilon}{eN_{D/A}} \left(V_{bi} + V_{bias}\right)}$$

(2.11)

The voltage  $V_{bias}$  that is required to deplete the full thickness of the diode is called depletion voltage  $(V_{depl})$ . The resistivity  $\rho$  of a doped n/p - type semiconductor can

**Figure 2.2:** Energy levels of a p-n junction. The Fermi energy  $E_F$  is at the same level for the p-type and the n-type silicon, thus creating a zone where the conduction and valence bands are bent. This energy shift creates the built-in voltage  $V_{bi}$  in the central area (depletion zone).

be expressed as:

$$\rho_{n/p-type} = \frac{1}{eN_{D/A}\mu_{e/h}},\tag{2.12}$$

where  $\mu_{e/h}$  is the mobility of electrons or holes. This allows to express the depletion

depth as a function of the resistivity:

$$d = \sqrt{2\mu_{e/h}\epsilon\rho(V_{bi} + V_{bias})}$$

(2.13)

Thus, the depletion depth at the same voltage is bigger on higher substrate resistivities. Note that the depletion depth is growing into the less doped region of the semiconductor.

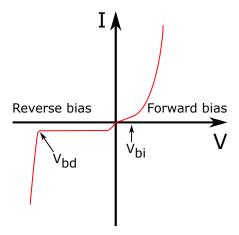

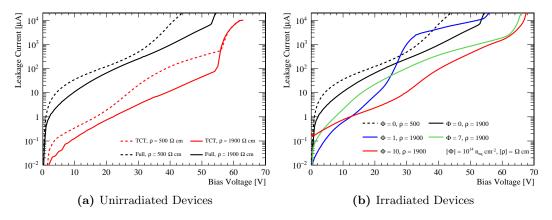

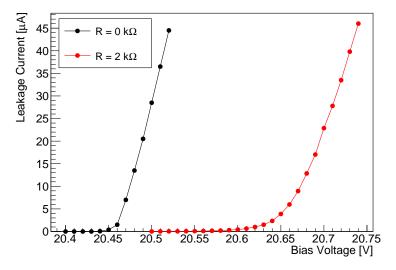

In this manner, by operating the detector as a reversed biased diode, an average signal of  $3.2 \cdot 10^4 e^-/h^+$  (for a thickness of 300 µm) is observed. However, there will be a dark current flowing through the detector volume. This dark current, or leakage current, is generated when the external voltage  $V_{bias}$  is applied to remove the free space charge. In unirradiated sensors this current is mostly coming from thermal excitations in the depleted region, thus it increases with the volume of the depletion region and the temperature. In Figure 2.3, the leakage current for a p-n junction (that acts like a diode) is shown: By increasing the reverse bias of the p-n junction, the electric field gets stronger, thus creating a larger depleted region. After a certain voltage, the electric field becomes so strong, that any charge created in the depletion zone gets so much energy that it can create more charge through impact ionization, leading to an avalanche. This voltage is called the breakdown voltage  $(V_{bd})$ . A small leakage current is desired, since the current introduces noise and can also damage the readout electronics. As an example, in the RD53A Application-Specific Integrated Circuit (ASIC) [6] a maximum leakage current per pixel of 10 nA is specified. Note that in forward biasing, the depletion zone gets reduced till the intrinsic built-in voltage  $V_{bi}$  is overcome. Afterwards, the leakage current rises exponentially [7].

The rate of thermal excitations of electron-hole pairs that lead to the leakage current is temperature dependent, one finds the following dependency for the leakage current:

$$I_{leak} \propto T^2 e^{-E_g/2kT} \tag{2.14}$$

Figure 2.3: Leakage current as a function of bias voltage for a p-n junction (diode). In reverse bias the leakage current does not change over a large range of voltage until the breakdown voltage  $V_{bd}$  where it rises exponentially. In forward bias the current rises linearly until the intrinsic built-in voltage  $V_{bi}$  is overcome. Afterwards, the the leakage current rises exponentially.

A detector that is operated at a lower temperature has thus a lower leakage current and consequently lower noise. This is especially important when dealing with devices that have an increased leakage current in the bulk due to radiation induced damage. Note that this relation is only valid for leakage current from the bulk and not from surface currents.

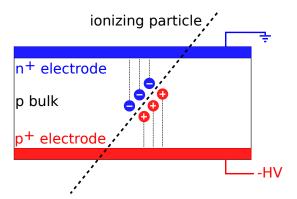

#### 2.2 Silicon Detectors

As described above, the core element of a silicon detector is a reverse biased p-n junction, where electron-hole pairs that are created in the bulk by ionizing particles are collected by heavily doped p- and n-type regions that act as electrodes. These p-type and n-type regions as usually noted as  $p^+$  and  $n^+$ , respectively. The most basic silicon detector, shown in Figure 2.4, without any segmentation is called a pad diode. These are usually used for prototypes since they are easy to fabricate, or if the segmentation is not a requirement for the experiment.

If the device is segmented in one dimension, thus forming parallel lines, it is called

**Figure 2.4:** Sketch of a n-on-p pad diode with an ionizing particle creating e/h pairs in the bulk that are collected by the electrodes.

strip detector. The readout of one line in a strip detector is usually at one end of each strip. Strip detectors can only measure particles in one dimension, thus two strip detectors (that are not aligned) are required for a precise 2D measurement of the particle impact point.

When more than one particle creates a signal in two strip detectors, there is an ambiguity on to where each particles crossed. This can be resolved by using a device that is segmented in both directions and thus creating a 2D matrix of pixels, called a *pixel detector*. In a pixel detector, each pixel needs to be connected to a readout channel, thus creating a high amount of readout channels in comparison to strip detectors. Traditionally, each sensing pixel (i.e. the pixel where the ionization is created) is connected (pixel-by-pixel) to a separate readout chip through solder bumps. The pixel to pixel interconnection technique, called bump-bonding, is quite complicated and expensive. Detectors where the sensor and readout chip are two different substrates are called *hybrid detectors*.

Recently in HEP, silicon pixel detectors have been produced in the CMOS technology. This allows to have the sensor and electronics on the same substrate. Since the sensor and readout chip are a single component, these devices are called *monolithic detectors*. In a monolithic device the analog signal generated in each pixel can be amplified and digitized, and then sent to the periphery of the sensor from where

it can be read out.

The advantage of hybrid detectors is that sensor and readout chip can be produced in different technologies. This allows to use a readout chip for different types of sensors and vice versa. In this way one can optimize each component separately which is especially important to achieve radiation hard detectors. On the other hand, in monolithic devices no bump-bonding is required, which is an expensive process in hybrid detectors and also adds to the material budget of the detector. In addition, since the limitation for the pixel size in hybrid detectors are due to the size of the bumps, monolithic devices can also be produced with smaller pixel sizes. The missing bump-bond also allows to achieve a lower pixel capacity and thus noise. Thus, CMOS is a promising technology when the requirements on the radiation hardness are not too strict and the cost of the pixel detector has to be held low, for example when large areas need to be covered.

#### 2.2.1 Interaction of Charged Particles with Matter

When charged particles pass through matter, they interact with the atoms of the material, thus continuously losing part of their energy. For relativistic charged particles in a momentum range of  $0.1 \lesssim \beta \gamma \lesssim 1000$  the mean energy loss per distance is described by the Bethe-Bloch equation [8]:

$$\left\langle -\frac{dE}{dx} \right\rangle = Kz^2 \frac{Z}{A} \frac{1}{\beta^2} \left[ \frac{1}{2} \log \frac{2m_e c^2 \beta^2 \gamma^2 W_{max}}{I^2} - \beta^2 - \frac{\delta(\beta \gamma)}{2} \right]$$

(2.15)

where  $K=4\pi N_A r_e^2 m_e c^2$  ( $N_A$  being the Avogrado's number,  $r_e$  the classical electron radius and  $m_e c^2$  the rest mass of the electron), z is the charge of the particle in multiples of the electron charge, Z is the atomic number of the medium, A is the atomic mass of the medium,  $W_{max}$  is the maximum energy transfer in a single collision, I is the mean excitation energy of the medium,  $\beta = v/c$ ,  $\gamma = 1/\sqrt{1-\beta^2}$  is the Lorentz factor, and  $\delta(\beta\gamma)$  is a correction factor for high energy ionization [9]. In

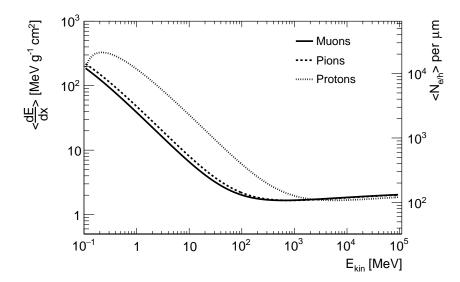

Figure 2.5 the Bethe-Bloch formula is shown for muons, pions and protons in silicon. The formula has a minimum at  $\beta\gamma \sim 3$  (around 500 MeV for pions) that hardly increases for several orders of magnitudes of momentum. At this point, particles are called *minimum ionizing particle* (*mip*). A *mip* has an average stopping power of  $\langle \frac{dE}{dx} \rangle = 1.66 \,\text{MeV} \,\text{cm}^2/\text{g}$  in silicon, or 107 e/h pairs per µm. Note that in silicon 3.6 eV are required to create an electron/hole pair, higher than the band-gap of 1.12 eV, due to the indirect band-gap that requires the creation of phonons for momentum conservation.

**Figure 2.5:** Average stopping power for muons, pions and protons in silicon as a function of the kinetic energy. The average number of created electron/hole pairs per micrometer is also shown. Adapted from [10].

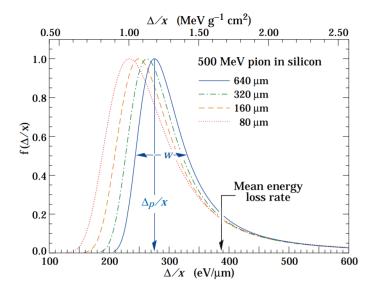

The energy loss probability distribution follows roughly a Landau distribution. This asymmetric distribution has a long tail, thus shifting the mean energy loss to higher values. Therefore it is more common to quote the most probable value  $\Delta_p$  (MPV) of the Landau Distribution:

$$\Delta_p = \xi \left[ \log \frac{2m_e c^2 \beta^2 \gamma^2}{I} + \log \frac{\xi}{I} + 0.200 - \beta^2 - \delta \left( \beta \gamma \right) \right]$$

(2.16)

with  $\xi = (K/2) \langle Z/A \rangle (x/\beta^2)$  MeV for a detector with a thickness x expressed in

$g/cm^2$ . The MPV of this distribution thus depends on the active thickness - the distribution for a mip for several detector thicknesses is shown in Figure 2.6.

**Figure 2.6:** Landau distribution of the deposited energy by 500 MeV pions in silicon for different silicon thicknesses. The distributions are normalized to the most probable value of each distribution. Adapted from [8].

#### 2.2.2 Interaction of Photons with Matter

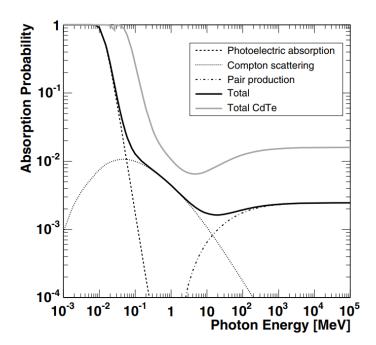

Photons interact in a different way when passing through matter than charged particles. They do not lose energy continuously along their path, but instead release most of their energy locally after being absorbed by the material. The absorption probability increases exponentially with the penetration depth, and the cross section (and absorption mechanism) also depends on the photon energy, as seen in Figure 2.7. The main three processes in which HEP photons interact with matter are the following [7]:

• Photoelectric Effect: The photon is completely absorbed by an atom and frees an electron of an energy equal to the photon energy minus the ionization energy. The cross-section of this process strongly depends on the proton number Z of the atom ( $\sigma_{pe} \propto Z^n$ , where n ranges from 4 to 5 [11]), thus materials with

high Z have a much higher probability for photon absorption. This effect is the dominating contribution to the cross section in silicon at energies below 100 keV. For higher energies, the cross-section falls off several orders of magnitude.

- Compton Scattering: At higher energies between  $\sim 100\,\mathrm{keV}$  and  $\sim 10\,\mathrm{MeV}$  Compton scattering of the photons with the electrons in the material becomes a more important component of the cross section. This results in a lower energy photon and a recoil electron.

- Pair Production: For photon energies above twice the electron rest mass (1.022 MeV),  $e^+/e^-$  pairs can be created, which can create further photons through bremsstrahlung.

**Figure 2.7:** Absorption probablity of photons in 300 µm silicon as function of the photon energy. The three contributions from photoelectric absorption, compton scattering and pair productions are shown. From [7].

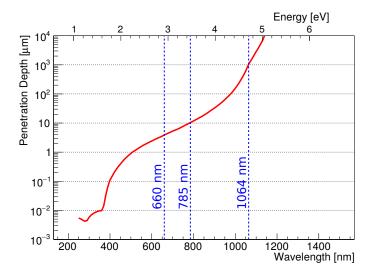

For low energy photons in the visible and Infrared Radiation (IR) range, like in the use of APDs, photons interact with the electrons in the valence band and excite them to the conduction band. In Figure 2.8 the penetration depth of photons in intrisic silicon at  $T=300\,\mathrm{K}$  is shown for wavelengths in the visible and NIR. Note that even photons with an energy below the mean energy to create a  $e^-/h^+$  pair of

$3.6\,\mathrm{eV}$  (thus above  $\sim 350\,\mathrm{nm}$ ), but below the band-gap energy, can be absorbed. This can happen due to an additional absorbed thermal phonon that gives the necessary energy to allow this process [12]. Since this process is unlikely, the penetration depth of photons above this wavelength is reduced.

**Figure 2.8:** Penetration depth of photons in intrinsic silicon at  $T = 300 \,\mathrm{K}$  as a function of the wavelength and photon energy. Lines for the wavelengths used in chapter 6 (660 nm, 785 nm and 1064 nm) are shown. Data taken from [13].

#### 2.2.3 Signal Formation

Previously, the creation of charge in the bulk from passing particles was described. This charge is then collected, leading to a signal and thus the detection of the particle if the signal is large enough. The electron-hole pairs that are created in the depleted region drift towards the positive and negative electrodes in the electric field E. The velocity of this drift is characterized by their mobility  $\mu_{e/h}^{-1}$  in the medium and can be expressed as:

$$v_{e/h} = \mu_{e/h} E \tag{2.17}$$

$<sup>^1\</sup>mathrm{In}$  silicon at T=300 K:  $\mu_e=1400\,\mathrm{cm^2/V/s}$  and  $\mu_h=450\,\mathrm{cm^2/V/s}$

The movement of the charge in the electric field induces a current in the readout electrode that is described by the Schockley-Ramo theorem [14, 15]:

$$i = e\vec{v} \cdot \vec{E_w}. \tag{2.18}$$

Here  $E_w$  is the weighting field of the read-out electrode, which can be obtained by applying a unit potential  $\Phi_w$  to the read-out electrode and a zero potential to all others and then solving the Laplace equation  $\nabla^2 \Phi_w = 0$ .

The collected charge in the readout electrode in the time between  $t_1$  and  $t_2$  can then be calculated by integrating the current in the time domain:

$$Q = \int_{t_1}^{t^2} i(t)dt = e\Delta\Phi_w \tag{2.19}$$

This assumes, that in the time frame all the charge carriers reach the electrodes, thus the collected charge is equal to the number of generated electron/hole pairs. This is usually not the case for irradiated silicon where trapping of some charge carriers can occur during the collection time due to radiation induced defects, as discussed in section 2.3.

#### 2.2.4 Detector Applications

Silicon detectors are widely used in HEP and in medical imaging, but also in more commercial applications like the automotive industry or photo cameras. Each application has its own requirements for the detector, since the expected signal and environment is different in each of them, as well as the particle to be detected and the interaction mechanism. In the following, two applications, one for HEP and one for medical physics are explained.

#### **Tracking Detectors**

The possibility to fabricate compact detectors with segmentation of the order of tens of micrometers, makes pixel devices good candidates as tracking detectors in a HEP experiment. The depletion depth should be large enough, so that the charge generated by a passing particle is enough to trigger the discriminator level of the readout electronics. Thus they are operated at a reverse bias voltage that is sufficiently high, but before the breakdown voltage, as explained in subsection 2.1.2. A mip usually only loses a small fraction of its energy when passing through the detector, thus it is possible to add several layers of silicon detectors without perturbating the particle path significantly. This allows a precise reconstruction of its trajectory. The position resolution of this reconstruction depends on the overall geometry of the detector system and the segmentation of the detector: A finer segmentation allows a better resolution. For a sensor with a given pitch a, the digital position resolution is given by the standard deviation  $\sigma = a/\sqrt{12}$  of a particle that passes through the sensor with a flat probability distribution over the pixel area, assuming the signal is generated in one readout channel.

The particle can, however, also leave a signal in more than one pixel. This can happen if the particle passes the volume corresponding to neighbouring pixels, if the charge that is generated diffuses to a neighbouring pixel, or if delta electrons are produced that have enough energy to travel to nearby pixels and deposit its energy on the path. In order to estimate the particle position when passing through the detector, contiguous pixels with a hit information are merged into a cluster. The position of the cluster depends on the algorithm used, either purely based on hit information, or with additional information like deposited charge per pixel.

#### **Avalanche Photodiodes**

Medical imaging applications often require the detection of visible or IR photons. In contrast to photons in HEP experiments, these optical (or near optical) photons produce a very small number of electron/hole pairs in the silicon material. This means that a different mechanism then charge drifting towards the electrodes is needed to generate a signal. Avalanche Photodiodes (APDs) are silicon sensors operated close to the breakdown voltage. In this region, the electric field is so strong (for fields above  $E = 50 \,\mathrm{V\mu m^{-1}}$  [16]), that the electron or hole created in the bulk gets enough energy to knock another electron in the conduction band, thus creating more charge carriers (impact ionization). This process happens many times, thus leading to an avalanche and an amplification of the signal. A device operated in this region (linear region) is called APD. If a higher gain is required, the device can also be operated above the breakdown voltage. The created avalanche is then self-sustaining and can only be stopped by reducing the bias voltage below  $V_{bd}$ . This operation mode is called Geiger-mode in analogy to the Geiger counter, and the device is then called a Single-Photon Avalanche Diode (SPAD). Since the internal gain is very high, the electrical noise also gets amplified and this leads to fake signals. The frequency of this effect is called Dark Count Rate (DCR). When designing a SPAD it is important to try to reduce the DCR, otherwise the signal can not be distinguished from noise.

### 2.3 Radiation Damage

Silicon detectors in hadron collider experiments are typically exposed to a high level of radiation, thus it is important to understand the effect that radiation has on the performance of the detector. In an experiment, particles that penetrate the silicon sensor can have non-ionizing energy loss through interaction with atoms of the crystalline structure. This interaction can damage both the silicon bulk and in the interface with the  $SiO_2$  layer, which is an isolating, protective layer in the structure of the Si sensor, located close to the substrate surface. The resulting radiation damage effects are thus classified as bulk effects or surface effects. Usually the bulk effects are the main contribution of the performance deterioration of silicon sensors while surface effects tend to be important for the embedded electronics in the silicon detector. The

bulk effects will be described in the following section.

Bulk effects are caused by high energetic particles that interact with the nuclei of the silicon atoms and transfer more energy than 25 eV [17] to the nucleus. This can displace the atom from its original position in the lattice which results in a vacancy at that position. The recoiling atom either moves to an interstitial lattice position (thus causing a point-like defect), or travel within the crystal and displace other atoms, creating further point-like defects on the path. If the transferred energy exceeds 2 keV, the atoms lose most of their energy in localised positions, creating cluster defects [18].

#### 2.3.1 The NIEL Scaling Hypothesis

Since particles of different types and energies cause different bulk defects in the silicon crystal, a useful approach is to parametrize and normalize these effects to compare them. This can be done by expressing the bulk radiation damage with the Non-Ionizing Energy Loss (NIEL) hypothesis[19]. The NIEL hypothesis assumes that the damage of any particle at a given fluence  $\Phi$  (number of particles per unit area) can be scaled to the one of a reference particle at a certain energy. The usual reference particle is a 1 MeV neutron. The equivalent fluence  $\Phi_{eq}$  can be calculated by:

$$\Phi_{eq} = k\Phi = k \int_{E_{min}}^{E_{max}} \Phi(E) dE, \qquad (2.20)$$

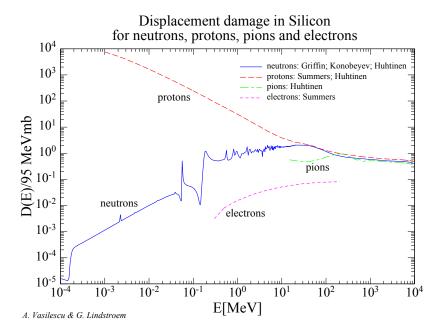

where k is the hardness factor that scales the displacement damage of each particle and energy to the 1 MeV neutron equivalent. The hardness factor can be determined by weighting the fluence with the energy dependent displacement damage cross section D(E) (see Figure 2.9) and normalized to the integrated fluence and the damage cross section of the reference particle (for 1 MeV neutrons:  $D(E_n = (1 \text{ MeV})) =$

95 MeV mb):

$$k = \frac{\int_{E_{min}}^{E_{max}} D(E)\Phi(E)dE}{D(E_n = (1 \text{ MeV})) \int_{E_{min}}^{E_{max}} \Phi(E)dE}$$

(2.21)

The NIEL hypothesis relates the 1 MeV neutron equivalent fluence on devices that

**Figure 2.9:** Displacement damage cross section D(E) as a function of particle energy for electrons, pions, protons and neutrons, normalized to 1 MeV neutrons. Taken from [20].

have been exposed to other fluences with other particles. This allows to study the performance of devices at any point of the lifetime in the experiment. In this thesis, devices have been irradiated with thermal neutrons in the TRIGA Mark II research reactor of the Jožef Stefan Institue (JSI) with a hardness factor of k = 0.9, and with 23 MeV protons at the Karlsruher Institut für Technologie (KIT) irradiation center with a hardness factor of k = 2.6.

#### 2.3.2 Impact on Sensor Performance

The radiation induced impurities in reversely biased silicon sensors have three main effects on the sensor performance: a change in the bulk doping concentration, an increase in the leakage current, and charge trapping.

#### **Doping Concentration**

One result of the radiation damage in the silicon bulk is a change of the effective doping. In a p-type sensors, it can be expressed as  $N_{eff,0} = N_A - N_D$ . After exposing the detector to a fluence  $\Phi$  the effective doping concentration can be expressed through the following parametrization [21]:

$$N_{eff}(\Phi) = N_{eff,0} - N_c \left( 1 - e^{-c\Phi} \right) + g_c \Phi \tag{2.22}$$

Here  $N_c$  and c are parameters that define the size and speed of the acceptor-removal effect which reduces the initial doping concentration.  $g_c$  describes the radiation induced acceptor creation in the bulk. One possibility to measure these parameters is through charge collection studies with a laser, like the study that is presented in section 4.5.

#### Trapping

The charged defects in the silicon bulk can also act as trapping centers for charge carriers during the collection time. This reduces the collected charge Q during the drift time, and can be expressed as a function of the fluence:

$$Q(\Phi) = Q_0 e^{-t_c/\tau} \quad with \quad 1/\tau = \beta_T \Phi \tag{2.23}$$

where  $Q_0$  is the initial charge (i.e. the signal for unirradiated devices),  $t_c$  is the charge collection time and  $\tau$  is the trapping time. The latter is inversely proportional to the fluence by a factor  $\beta_t$  that depends on the charge carrier type and on the radiation type (neutron or charged hadrons) [22].

#### Leakage Current

The defects induced by radiation create new energy levels in silicon. If these levels are between the band gap, they increase the probability for electrons to be excited to the conduction band and thus act as a generation center. This results in an increase of the leakage current  $I_{leak}$  in the depleted volume V that is proportional to the fluence:

$$I_{leak}(\Phi) - I_{leak}(0) = \alpha \Phi V \tag{2.24}$$

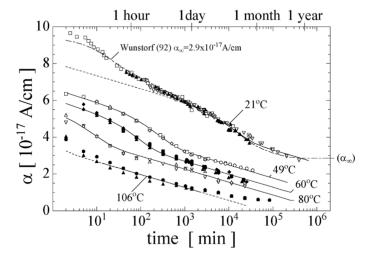

Here the proportionality factor  $\alpha$  is the current-related damage rate which varies with time and temperature, as shown in Figure 2.10. The leakage current in the sensor also strongly depends on the operational temperature, as shown in Equation 2.14. On the other hand, irradiated devices can have a self-heating effect due to the increased leakage current. The increase of leakage current generates an increase in the temperature of the device in a feedback loop that is called *thermal runaway*, which can destroy the device. In order to prevent this, irradiated silicon sensors have to be cooled to reduce the leakage current and the consequent power consumption.

Figure 2.10: Change of the current-related damage parameter  $\alpha$  with the annealing time for different temperatures. From [23].

#### Annealing

The radiation induced defects that are created in the silicon bulk are not static, but they can move within the crystal structure, where they react with other defects or impurities or form new defect structures. This process is called annealing. The evolution is temperature dependent and can be accelerated by increasing the temperature of the silicon sensor, or slowed down by cooling it [23].

As seen in Figure 2.10, the effect of annealing is always beneficial in evolution of the current-related damage parameter  $\alpha$ , thus reducing the increased leakage current due to radiation damage.

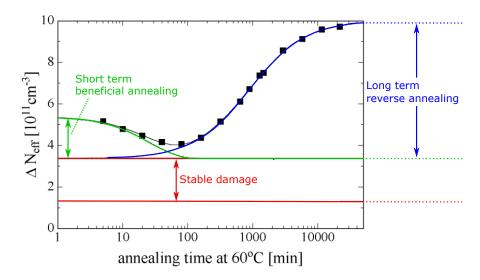

The effect of annealing on the effective doping concentration  $N_{eff}$  is initially beneficial as well, where  $N_{eff}$  is reduced, thus leading to a larger depletion depth at the same bias voltage, see Equation 2.11. Afterwards, a long term reverse annealing sets in that increases  $N_{eff}$  again to higher values, as seen in Figure 2.11.

**Figure 2.11:** Change of the effective doping concentration  $N_{eff}$  at 60 °C for a wide range of annealing times of a pad diode at a fluence of  $1.4 \cdot 10^{13} \, \text{n}_{\text{eq}}/\text{cm}^2$ . Adapted from [23].

# Chapter 3

# The ATLAS Experiment

The European Organization for Nuclear Research (CERN), located in Geneva (Switzerland), has the largest and most powerful hadron collider to date, the Large Hadron Collider (LHC). The LHC accelerates and collides protons at an unparalleled collision energy and luminosity, which allows to study the frontiers of particle physics.

The proton-proton (p-p) collisions happen at certain interaction points, where the experiments are located in order to record the products of the collisions. One of these experiments is the ATLAS experiment, that is composed of several detector systems. This chapter describes the ATLAS experiment at the LHC with a focus on the pixel detector.

# 3.1 The Large Hadron Collider

The LHC [24] is contained in a circular tunnel with a circumference of 27 km and is the last stage of a sequence of accelerators at CERN that ultimately collides protons of a center of mass energy of up to 14 TeV.

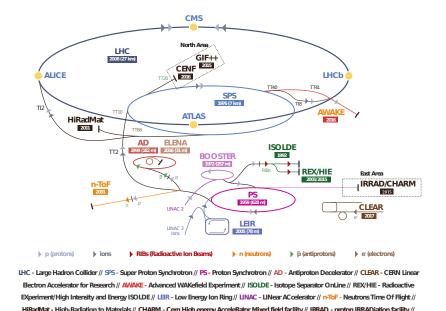

A scheme of the CERN accelerator complex is shown in Figure 3.1. Protons are obtained from an hydrogen bottle, where they are extracted and ionized and after-

wards accelerated in bunches in the LINear ACcelerator (LINAC) 2 linear accelerator to an energy of 50 MeV. Afterwards, they are further accelerated in the proton synchrotron booster to 1.4 GeV before being sent to the Proton Synchrotron (PS) accelerator where they reach an energy of 25 GeV. The next step is the CERN Super Proton Synchrotron (SPS) where the protons reach an energy of 450 GeV from where they are injected into the LHC.

In the LHC, the protons are accelerated in bunches of  $10^{11}$  particles in two independent beam-pipes in opposite directions to energies of up to 7 TeV. Bunches are separated temporally by 25 ns. The bunches are then crossed at the four interaction points, leading to a center-of-mass energy ( $\sqrt{s}$ ) of up to 14 TeV. Each interaction point hosts one of the main experiments at the LHC: ATLAS [25], CMS [26], ALICE [27] and Large Hadron Collider beauty (LHCb) [28]. Both ATLAS and CMS are multipurpose experiments, while ALICE is designed for heavy-ion physics and LHCb investigates b-quark physics.

The LHC is shut down periodically in order to improve and maintain its performance. The next long shutdown will take place between 2025 and 2027 and is a major upgrade to the LHC, increasing the luminosity by about a factor by a factor five to seven with respect to the nominal luminosity to  $5 \cdot 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. Due to the big change in luminosity, this future phase of the LHC is called HL-LHC. The experiments will have to be upgraded in order to cope with the new requirements of the HL-LHC, namely larger occupancy and pile-up level and the increased radiation level. In the following, the current ATLAS experiment will be presented, as well as the HL-LHC upgrade plan for the Inner Detector, which is the intended application of the silicon pixel detectors investigated in this thesis.

GIF++- Gamma Irradiation Facility // CENF- CErn Neutrino platform

Figure 3.1: Overview of the CERN accelerator complex. Taken from [29].

### 3.2 Overview of the ATLAS Experiment

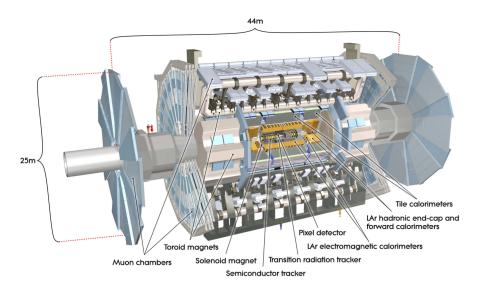

The ATLAS experiment is the largest general-purpose particle detector at the LHC, placed at one of the proton-proton interaction points, roughly 100 m underground. The detector has a cylindrical shape with a shell structure and forward-backward symmetry in the direction of the beams. It has a length of 42 m, a height of 25 m and weighs roughly 7000 tonnes (see Figure 3.2). ATLAS is composed of several sub-detectors, each with its specific purpose to reconstruct the particles arising from the proton-proton collisions. They are: the Inner Detector (ID) (section 3.3), the electromagnetic and hadronic calorimeters (section 3.4) and the muon spectrometer (section 3.5). In addition, a magnetic system (section 3.6) with fields of up to 4 T surrounds the ID. The ID system measures the trajectories of charged particles produced in the p-p collisions. With the help of the magnetic field surround the ID, also their momenta can be determined. The energy of electrons and photons can be measured in the electromagnetic calorimeter, where they are absorbed. Mesons and baryons travel further outside and interact in the hadronic calorimeter, generating

a particle shower whose energy is measured and allows to determine the energy of the underlying particle. Muons travel even further away from the center and reach the muon spectrometers, where they are tagged and their momentum measured. Due to their low interaction probability, neutrinos do not leave any signal in the ATLAS detector. However, due to energy and momentum conversion, their properties can be determined through missing transverse energy  $(E_t^{miss})$  and missing transverse momentum  $(p_t^{miss})$ .

In order to give a better description of the ATLAS experiment, a common coordinate system is required. The origin of the coordinate system is the nominal center of the p-p collisions, while the direction of one of the beams defines the z-axis. The x-y plane is transverse to the beam direction, with the x-axis pointing to the center of the LHC ring and the y-axis pointing upwards towards the surface (and a right handed system defines the positive z axis direction). In addition, the angles of a spherical coordinate system are used: the azimuthal angle  $\phi$  is measured around the beam axis, while the polar angle  $\theta$  is the angle from the beam axis. This allows to define the pseudorapidity by  $\eta = -\log(\tan(\theta/2))$ . Other important parameters are the transverse momentum  $(p_T)$ , the transverse energy  $(E_T)$  and the missing transverse energy  $(E_T)$  that are defined in the x-y plane.

#### 3.3 Inner Detector

The ID is the innermost detector system of ATLAS. It measures the trajectory of the charged particles produced in the proton-proton collisions with high precision. Their tracks are used to extrapolate the particle trajectory to their origin and associate them to the original collision (primary vertex) or to a subsequent decay (secondary vertex). The ID uses the 2 T solenoidal magnetic field of the ATLAS barrel solenoid (see section 3.6) to determine the particle momentum and charge polarity.

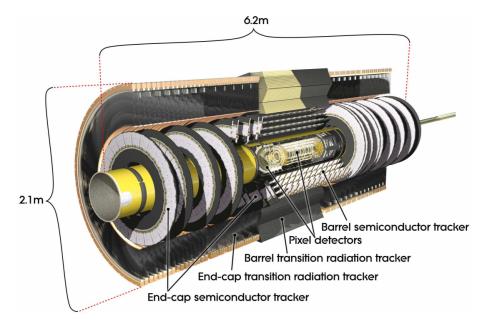

Figure 3.3 shows the sub-detectors of the ID. From inner-most to outer-most they

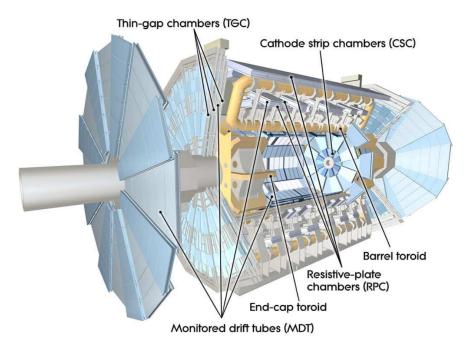

**Figure 3.2:** Cut-away view of the ATLAS detector. The detector has a height of 25 m, a length of 44 m and weighs roughly 7000 tonnes. Taken from [25].

are: the Pixel Detector [30] with the Insertable B-Layer (IBL) [31], the SemiConductor Tracker (SCT) [32] and the Transition Radiation Tracker (TRT) [33]. The ID has a length of 6.2 m, a height of 2.1 m and has a coverage in the pseudorapidity region of  $|\eta| < 2.5$ .

Figure 3.3: Cut-away view of the ATLAS ID. Taken from [25].

#### 3.3.1 Pixel Detector

The Pixel Detector originally consisted of three barrel layers of pixelated silicon sensors at a radius of 5.1, 8.9 and 12.3 cm from the beam axis with a length in z of 80 cm. In 2015 an additional inner barrel layer was installed, called IBL [31], at a radius of 3.2 cm with a length in z of 66.4 cm. Additionally, three end-cap discs are present on both ends of the Pixel Detector at |z| = 49.5, 58.0 and 65.0 cm with a radial extension of 8.9 cm < R < 15.0 cm.

The sensors in the three outer layers of the Pixel Detector and the end-caps are n-in-n planar sensors with a pixel size of  $50 \,\mu\text{m} \times 400 \,\mu\text{m}$  bump-bonded to the FE-I3 readout chip [34]. A group of 2 x 8 readout chips bump-bonded to a single sensor form a pixel module, that is connected through a flexible printed circuit board to communicate with the ATLAS Data Acquisition (DAQ).

The innermost layer, the IBL, was installed in 2015 in order to improve the impact parameter resolution, which is critical in the identification of relatively long-lived particles like b hadrons (b-tagging). Additionally, it guarantees a high detection efficiency of the Pixel Detector after radiation damage. The IBL uses two different pixel sensor technologies: n-in-n planar (75% of the central part) and n-in-p 3D sensors (25%, at the ends of the barrel). Both IBL sensor types have a pixel size of  $50 \,\mu\text{m} \times 250 \,\mu\text{m}$  and are bump-bonded to the FE-I4 readout chip [35].

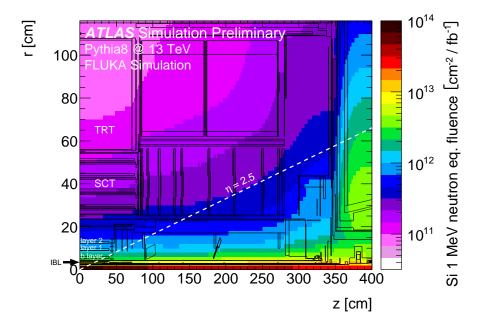

As already mentioned, the Pixel Detector is the detector system of ATLAS closest to the interaction point. This leads to the highest exposition to radiation damage, as seen in Figure 3.4. The IBL was designed to withstand an integrated luminosity of  $250\,\mathrm{fb^{-1}}$  [31], which is the estimated accumulated luminosity before the ID is replaced for the HL-LHC upgrade. The luminosity corresponds to a total fluence of  $5\cdot10^{15}\,\mathrm{n_{eq}/cm^2}$ .

Figure 3.4: Simulations of the 1 MeV neutron equivalent fluence per  $fb^{-1}$  of integrated luminosity in the ATLAS ID. The minimum-bias p-p events are simulated at 13 TeV center of mass energy and a predicted inelastic cross section of 78.4 mb. Particle tracking and interactions with material are simulated with the FLUKA 2011 code using the Run 2 geometry description of the ATLAS detector. Taken from [36].

#### 3.3.2 SemiConductor Tracker

The SCT [37, 38] is composed by four barrel layers and nine end-caps per side of p-in-n microstrip detectors. The barrels are placed at a radius of 30.0, 37.3, 44.7 and 52.0 cm with a length of 149 cm. Two layers of silicon strip sensors are placed per layer, at a small stereo angle of 40 mrad, thus allowing 2D information to the track position. The nine end-caps are distributed at different distances from the interaction point, in a range from 85 cm < |z| < 272 cm, with an outer radius of 56 cm and different inner radii from 27 cm to 44 cm, where the end-caps closer to the interaction point have smaller radii. This allows an instrumented coverage for the SCT in the pseudorapidity region of  $|\eta| < 2.5$ . The pitch of the strips in the barrel region is 80 µm, while in the end-cap sensors range from 50.9 to 90.4 µm.

#### 3.3.3 Transient Radiation Tracker

While the Pixel Detector and the SCT are based on silicon sensors, the TRT [39, 40] is a gas detector. It consists of 4 mm diameter strawtubes filled with an ionizing gas mixture (xenon (70%), carbon dioxide (27%) and oxygen (3%)). The center of the straw-tubes is a 31 µm diameter gold-plated tungsten anode wire, that has an electric potential difference of 1500 V to the tube walls. This allows to collect the ionization charge of a particle and thus measure the track position with a resolution of 130 µm per straw. The TRT barrel has a total of 52544 straws of 1.44 m length along the beam direction in the radii between 56 cm < R < 107 cm. The end-caps are made of 122880 straws each, that are distributed along the beam axis with a coverage of 85 cm < |z| < 271 cm and 64 cm < R < 100 cm.

#### 3.4 Calorimeters

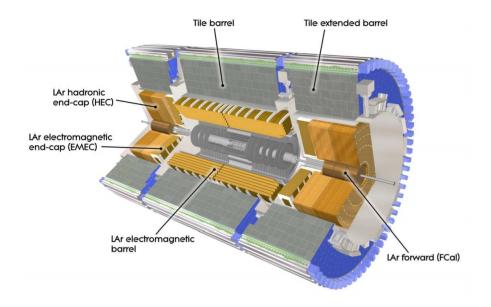

While the Inner Detector measures the trajectory of the charged particles, the purpose of a calorimeter is to measure the energy of impinging particles, usually by stopping a particle completely and measuring the signals that depend on the deposited energy. There are two types of calorimeters. Homogeneous calorimeters are sensitive in the whole detector volume to the particles and all the deposited energy contributes to the signal. Sampling calorimeters, as used in ATLAS, have two different layers, absorbing and sensitive parts. This design allows a more compact detector, however it requires a precise calibration in order to obtain the particle energy from the measured signal. The ATLAS calorimeter system has a total of three sub-detectors, surrounding the ID: the Electromagnetic, the Hadronic and the Forward calorimeters, shown in Figure 3.5. The calorimeter system covers the pseudorapidity region  $|\eta| < 4.9$ .

Figure 3.5: Cut-away view of the ATLAS calorimeter system. Taken from [25].

#### 3.4.1 Electromagnetic Calorimeter

The Electromagnetic CAL orimeter (ECAL) is the closest calorimeter sub-system to the interaction point. It absorbs electrons and photons in the energy range  $50\,\mathrm{MeV} < E < 3\,\mathrm{TeV}$  to measure their energy and impinging direction. Additionally it is part of the reconstruction of hadronic jets that already start their shower in the volume of the ECAL.

The ECAL is made of lead absorber planes and Liquid Argon (LAr) [41] detectors that are placed in accordion shaped layers, covering a pseudorapidity range of  $|\eta| < 3.2$ . The detector is divided in a barrel (covering  $|\eta| < 1.475$ ) and two end-cap wheels per side (1.375  $< |\eta| < 2.5$  and 2.5  $< |\eta| < 3.2$ ). When particles pass the LAr calorimeter, they ionize the argon, creating a charge that is collected by copper layers in the center of the LAr sections that act as readout electrodes.

The ECAL barrel is divided in three layers, where the thickness of each layer is characterized in units of radiation length  $X_0$ , which is the thickness after which the particle energy is reduced by a factor 1/e: The inner layer has a thickness of 4.3  $X_0$ ,

the middle layer 16  $X_0$  and the outer layer 2  $X_0$ . The end-caps have a thickness in total of 24  $X_0$ . This allows a full confinement of the electromagnetic showers both in the barrel layers and in the end-caps.

#### 3.4.2 Hadronic Calorimeter

Particles that escape the ECAL are measured in the Hadronic CALorimeter (HCAL). Those are usually high energy jets from quark and gluon hadronization. The HCAL absorbs all the remaining particles from the collisions, except for muons, that are detected in the muon spectrometer, and neutrinos, that do not deposit energy in any sub-detector of ATLAS. The HCAL has two parts, the Tile Calorimeter (TileCal) in the central region and the Hadronic End-Cap Calorimeter (HEC) in the forward region.

The TileCal [42] consists of steel as absorber medium and scintillating tiles of polystyrene as active region. Particles traversing the scintillating tiles generate photons, that are collected by Photomultiplier Tubes (PMTs). The TileCal covers the pseudorapidity range of  $|\eta| < 1.7$ , where the central barrel covers  $|\eta| < 1.0$  and the extended barrels cover  $0.8 < |\eta| < 1.7$ .

The HEC uses copper as absorber medium and LAr as active medium. It covers a pseudorapidity range of  $1.5 < |\eta| < 3.2$  in the form of two wheels on each side.

#### 3.4.3 Forward Calorimeter

The Forward CALorimeter (FCAL) [43] consists of one electromagnetic and two hadronic calorimeters. Its purpose is to increase the acceptance of the calorimeter in the forward direction at low radii, covering a pseudorapidity of  $3.1 < |\eta| < 4.9$ . All layers of the FCAL use LAr as a detection medium. In the inner (electromagnetic) part copper is used as an absorber medium, while the outer (hadronic) layer

uses tungsten.

## 3.5 Muon Spectrometer

Due to their large mass muons pass the electromagnetic and hadronic calorimeters without being stopped. In order to tag muons and determine their momentum a dedicated Muon Spectrometer is placed around the calorimeters. The ATLAS Muon Spectrometer [44] consists of four sub-detectors (see Figure 3.6), covering the pseudorapidity range of  $|\eta| < 2.7$ : the Monitored Drift-Tube (MDT) chamber, the Cathode Strip Chamber (CSC), the Resistive Plate Chambers (RPCs) and the Thin Gap Chambers (TGCs).

Figure 3.6: Cut-away view of the ATLAS muon system. Taken from [25].

#### 3.5.1 Monitored Drift-Tube Chambers

The main part of the Muon Spectrometer is the MDT [45] sub-system that uses drift chambers to get a precise muon momentum resolution by measuring the muons' track curvature in the magnetic field of the toroid magnets (described in section 3.6). Each drift chamber element consists of 400 µm thick aluminum drift tubes with a diameter of 3 cm that are filled with a mixture of argon (93%) and carbon dioxide (7%) under 3 bar pressure with a varying length between 0.9 m and 6.2 m. The MDT has in total 1150 chambers with up to 354000 drift tubes and achieves a position resolution of 30/40 µm for 6/8 layer chambers. The chambers are distributed in three barrel layers, located at radii of 4.5, 8 and 10 m from the beam axis in addition to three end-cap layers at |z| of approximately 7.5, 14 and 21.5 m, leading to a coverage of the pseudorapidity of  $|\eta| < 2.7$ .

New MDT tubes with half the diameter (1.5 cm) were installed during the 2016/17 winter shut-down, thus leading to an improved muon momentum reconstruction [46].

#### 3.5.2 Cathode Strip Chambers

The CSC [47] consists of multi-wire proportional chambers with segmented cathodes and are placed in two end-caps at  $|z| = 7 \,\mathrm{m}$ , covering a pseudorapidity range of  $2.0 < |\eta| < 2.7$ . Its purpose is to improve the muon momentum resolution in the forward direction, reaching a position resolution of 60 µm. Each end-cap has 16 chambers of four layers that are filled with a mixture of argon (80%) and carbon dioxide (20%).

#### 3.5.3 Resistive Plate Chambers

The RPCs [48] are used together with the TGC to provide a muon trigger, but also perform a position measurement in the non-bending direction in the barrel region of the Muon Spectrometer. The RPC system consists of very high resistive parallel plates at a distance of 2 mm with a gas in between that gets ionized by traversing muons. The gas is a mixture of  $C_2H_2F_4$  (94.7%), Iso- $C_4H_{10}$  (5.0%) and  $SF_6$  (0.3%) and the parallel plates are made of phenolic-melaminic plastic laminate biased at

9.6 kV, thus working in a valanche mode. The RPCs cover the pseudorapidy range of  $|\eta| < 1.05$ .

#### 3.5.4 Thin Gap Chambers

The TGCs [44] consist of multi-wire proportional chambers, covering the forward region of ATLAS in the pseudorapidty range  $1.05 < |\eta| < 2.4$ . Their purpose is to improve the muon trigger in combination with the RPCs, but also to assist the muon tracking of the MDT. The chambers have  $50 \,\mu m$  thick anode wires inside, with a distance of 1.8 mm to the next wire and 1.4 mm to the cathodes. Each chamber is filled with a mixture of carbon dioxide (55%) and n-C<sub>5</sub>H<sub>12</sub> and achieves a spatial resolution of 1 mm and a time resolution of 5 ns.

### 3.6 Magnet System

The ATLAS magnet system [49] consists of four superconducting magnets. One solenoid magnet that surrounds the ID aligned with the beam axis with an axial magnetic field of 2 T allows the measurement of the momentum of charged particles. In addition, a barrel and two end-cap toroids are present, producing a magnetic field of up to 4 T in order to bend the muon tracks to determine their momentum.

# 3.7 Inner Detector Upgrade for the HL-LHC

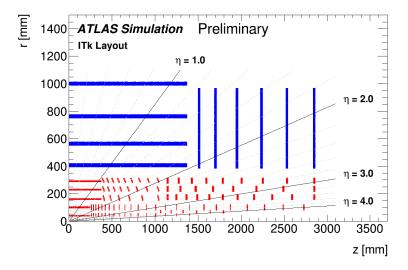

The LHC will be upgraded during the Long Shutdown 3 (LS3) in 2024-2026 in preparation for the HL-LHC era. The goal of the HL-LHC upgrade is to have an increased dataset of 4000 fb<sup>-1</sup> approximately by the year 2036 after having collected 400 fb<sup>-1</sup> in the LHC era. In order to achieve such a big dataset in a reasonable time scale, the luminosity of the accelerator has to be increased.

The HL-LHC will have an increased peak luminosity, leading to a higher average inelastic p-p collision per bunch crossing (from  $\sim 50$  to  $\sim 200$ ). The energy of the particles in the beam will not be changed during the upgrade. This does not extend the LHC physics program in the energy frontier, but it allows to significantly reduce the statistical uncertainties of many Standard Model parameters and enables the study of more rare physics processes [50]. Since the performance of many of the subdetectors of ATLAS will degrade significantly in the HL-LHC era, a replacement of the detectors is required. Due to the harsher radiation environment and the higher number of tracks per bunch crossing, the requirements for the HL-LHC on the ATLAS detector systems have been increased in order to have a similar performance as during the LHC period [51].

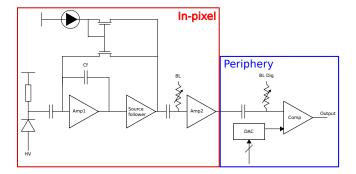

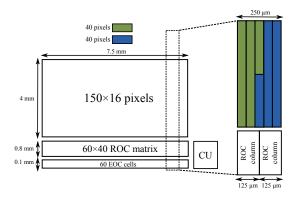

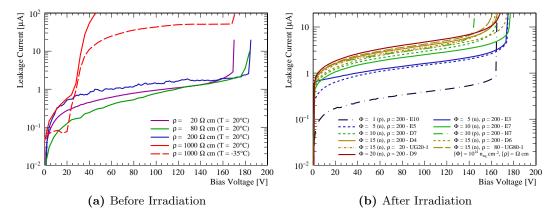

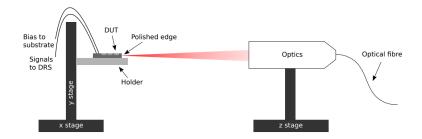

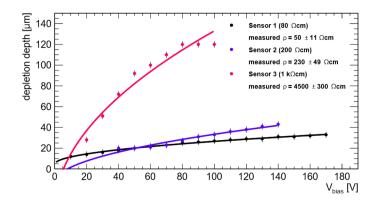

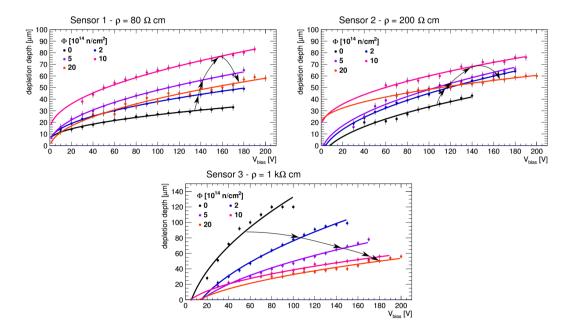

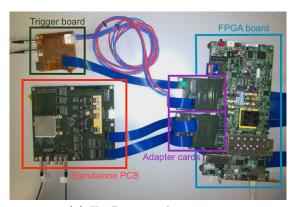

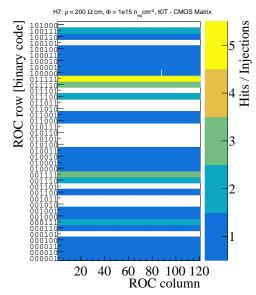

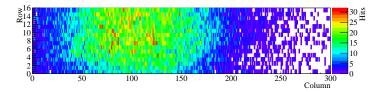

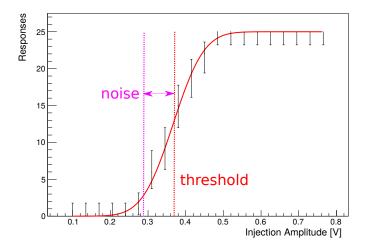

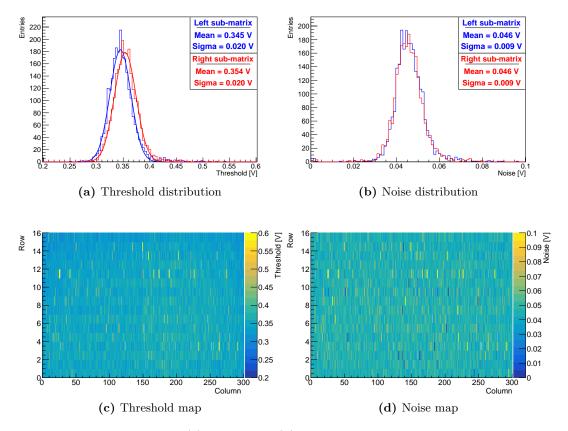

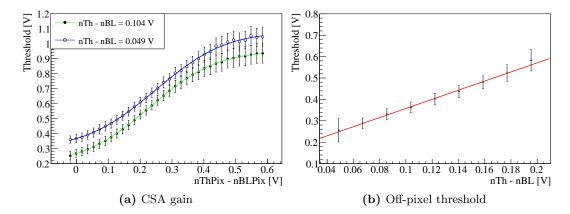

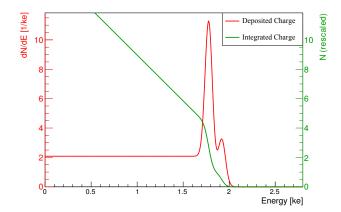

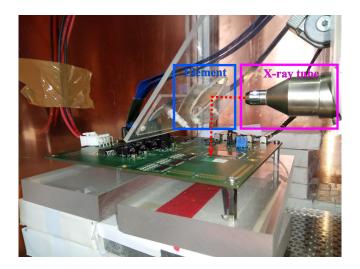

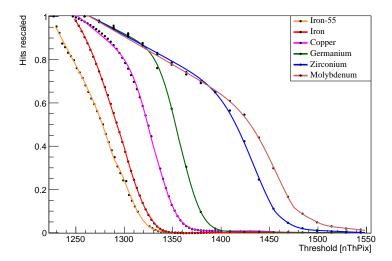

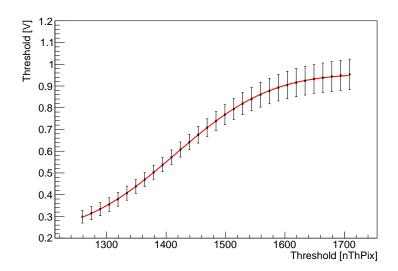

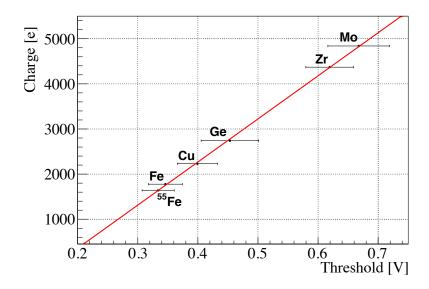

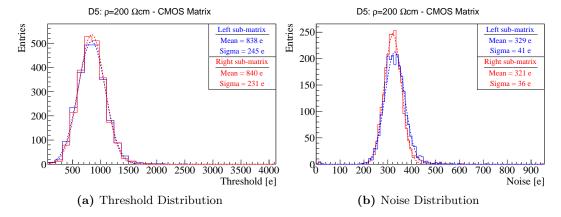

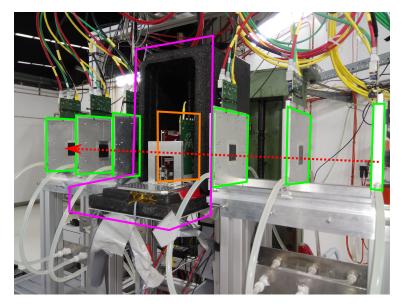

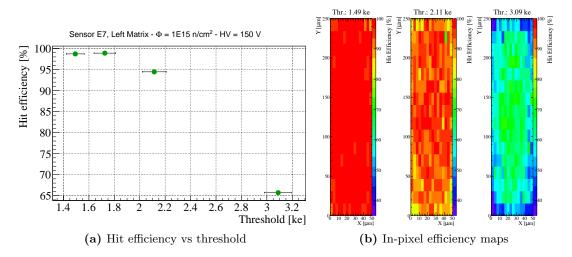

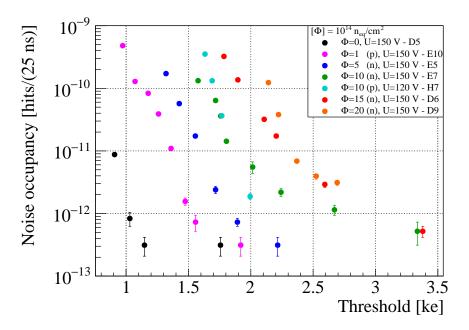

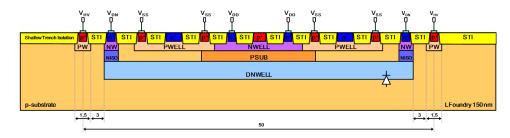

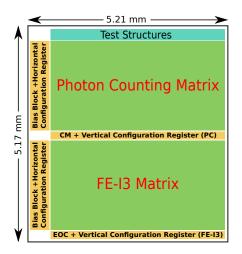

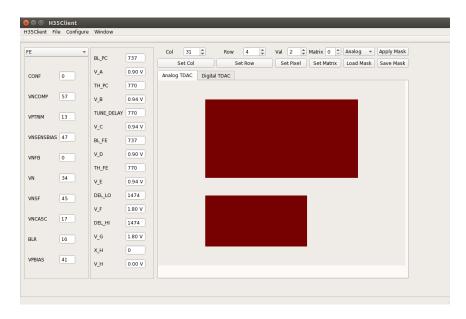

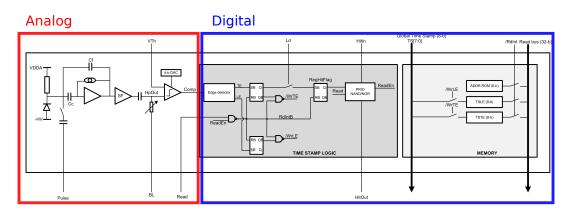

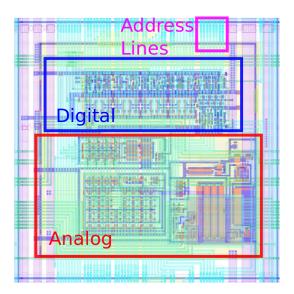

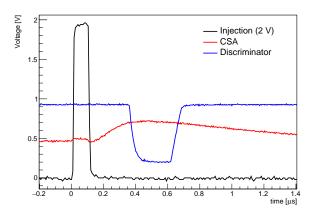

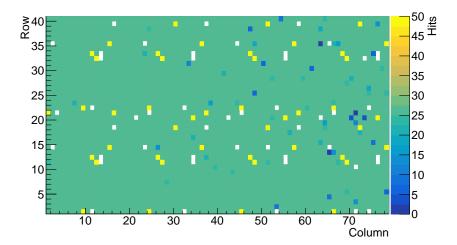

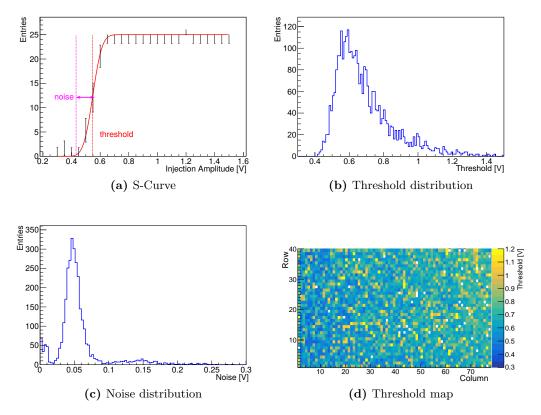

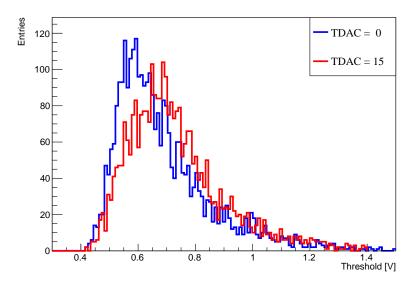

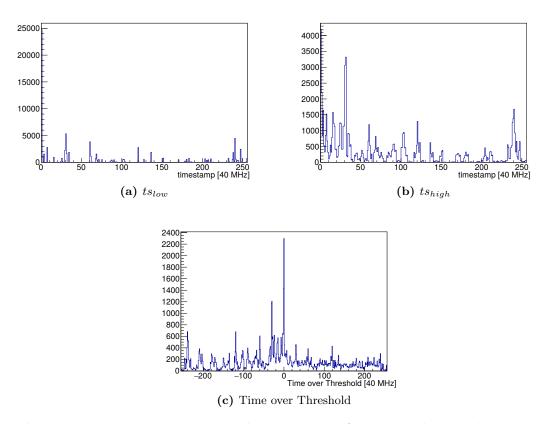

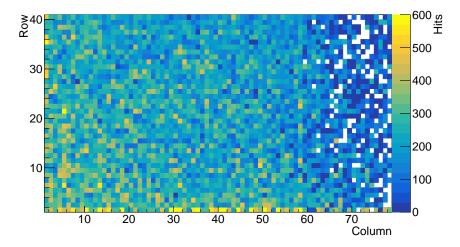

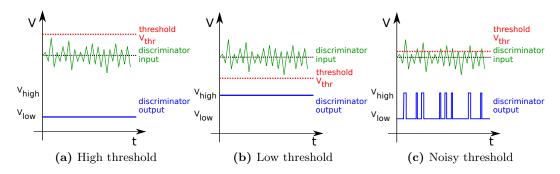

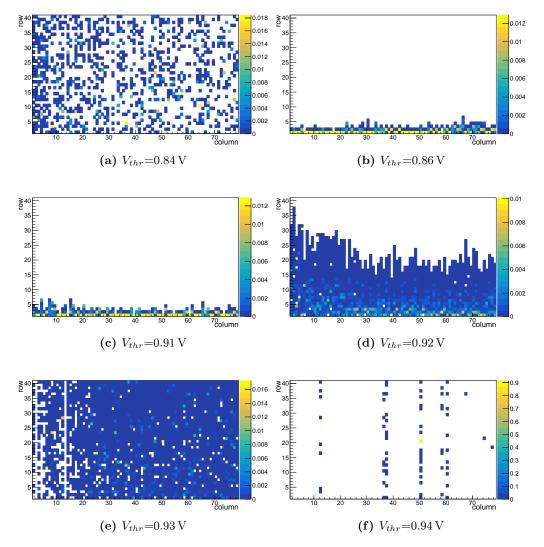

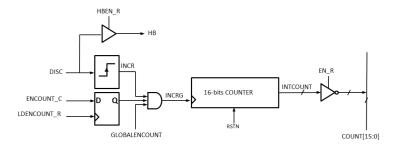

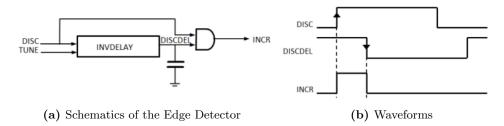

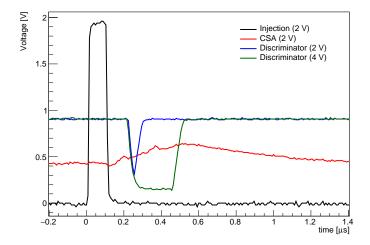

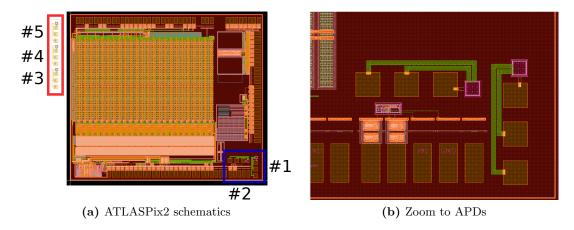

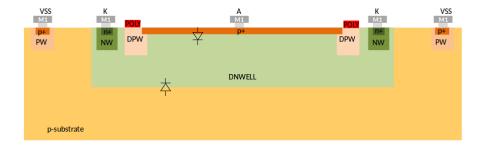

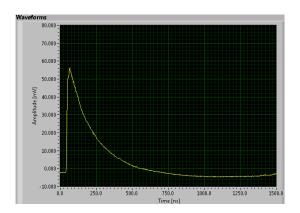

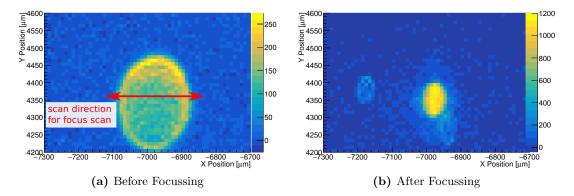

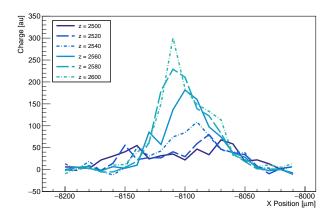

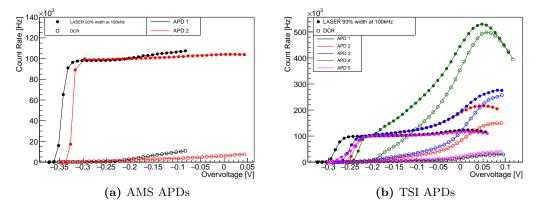

The plan is to replace the forward calorimeters and muon wheels in order to withstand the increased radiation damage, where the barrel calorimeters and muon systems will not be replaced, since they are expected to handle the increased luminosity without a major performance degradation.