#### COMPACT DC MODELLING OF SHORT-CHANNEL EFFECTS IN ORGANIC THIN-FILM TRANSISTORS

#### Prüfer Jakob Markus

**ADVERTIMENT**. L'accés als continguts d'aquesta tesi doctoral i la seva utilització ha de respectar els drets de la persona autora. Pot ser utilitzada per a consulta o estudi personal, així com en activitats o materials d'investigació i docència en els termes establerts a l'art. 32 del Text Refós de la Llei de Propietat Intel·lectual (RDL 1/1996). Per altres utilitzacions es requereix l'autorització prèvia i expressa de la persona autora. En qualsevol cas, en la utilització dels seus continguts caldrà indicar de forma clara el nom i cognoms de la persona autora i el títol de la tesi doctoral. No s'autoritza la seva reproducció o altres formes d'explotació efectuades amb finalitats de lucre ni la seva comunicació pública des d'un lloc aliè al servei TDX. Tampoc s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant als continguts de la tesi com als seus resums i índexs.

**ADVERTENCIA.** El acceso a los contenidos de esta tesis doctoral y su utilización debe respetar los derechos de la persona autora. Puede ser utilizada para consulta o estudio personal, así como en actividades o materiales de investigación y docencia en los términos establecidos en el art. 32 del Texto Refundido de la Ley de Propiedad Intelectual (RDL 1/1996). Para otros usos se requiere la autorización previa y expresa de la persona autora. En cualquier caso, en la utilización de sus contenidos se deberá indicar de forma clara el nombre y apellidos de la persona autora y el título de la tesis doctoral. No se autoriza su reproducción u otras formas de explotación efectuadas con fines lucrativos ni su comunicación pública desde un sitio ajeno al servicio TDR. Tampoco se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al contenido de la tesis como a sus resúmenes e índices.

**WARNING**. Access to the contents of this doctoral thesis and its use must respect the rights of the author. It can be used for reference or private study, as well as research and learning activities or materials in the terms established by the 32nd article of the Spanish Consolidated Copyright Act (RDL 1/1996). Express and previous authorization of the author is required for any other uses. In any case, when using its content, full name of the author and title of the thesis must be clearly indicated. Reproduction or other forms of for profit use or public communication from outside TDX service is not allowed. Presentation of its content in a window or frame external to TDX (framing) is not authorized either. These rights affect both the content of the thesis and its abstracts and indexes.

# **Compact DC Modelling of Short-Channel Effects in Organic Thin-Film Transistors**

JAKOB PRÜFER

DOCTORAL THESIS 2021

#### Jakob Prüfer

Compact DC Modelling of Short–Channel Effects in Organic Thin–Film Transistors

#### DOCTORAL THESIS

Supervised by Prof. Dr. Benjamín Iñíguez and Prof. Dr.-Ing. Alexander Kloes

Department of Electronic, Electrical and Automatic Control Engineering

Universitat Rovira i Virgili

Tarragona 2021

#### Statement of Supervision

# Department of Electronic, Electric and Automatic Engineering (DEEEA)

Av. Paisos Catalans 26, Campus Sescelades

43007, Tarragona, Spain Phone: +34 977 558524 Fax: +34 977 559605

I STATE that the present study, entitled: "Compact DC Modelling of Short–Channel Effects in Organic Thin–Film Transistors", presented by Jakob Prüfer for the award of the degree of the Doctor, has been carried out under my supervision at the Department of Electronic, Electrical and Automatic Control Engineering of this university, and that it fulfills all the requirements to be eligible for the European Doctorate Award.

Tarragona, Spain, December 22, 2021

Prof. Dr. Benjamín Iñíguez, Doctoral Thesis Supervisor

Abranch Uli

Prof. Dr.-Ing. Alexander Kloes, Doctoral Thesis Co-Supervisor

## Statement of Authorship

#### Research Group Nanoelectronics / Device Modeling

Wiesenstrasse 14

35390, Giessen, Germany Phone: +49 641 309-1968 Fax: +49 641 309-2901

I STATE that this document has been composed by myself and describes my own work, unless otherwise acknowledged in the text. Parts that are direct quotes or paraphrases are identified as such. It has not been accepted in any previous application for a degree. All sources of information have been specifically acknowledged.

Giessen, Germany, December 31, 2021

Jakob Prüfer, M. Sc.

# Contents

| Lis | t of F  | ublications                                    | ix    |

|-----|---------|------------------------------------------------|-------|

| Lis | t of S  | ymbols                                         | xiii  |

| Lis | st of A | cronyms                                        | xxiii |

| 1   | Intro   | duction                                        | 1     |

|     | 1.1     | Introduction to Organic Electronics            | 2     |

|     | 1.2     | The Thesis Structure                           | 3     |

| 2   | Devi    | e Physics                                      | 5     |

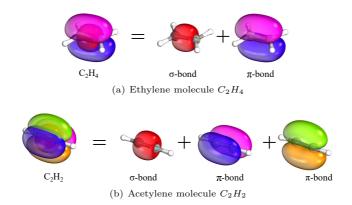

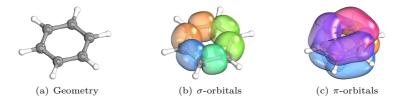

|     | 2.1     | Organic Chemistry                              | 5     |

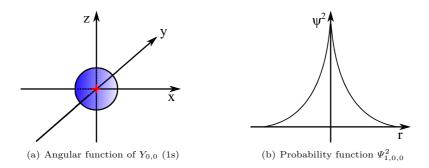

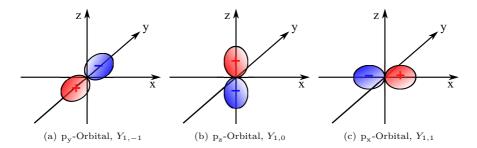

|     |         | 2.1.1 Atomic Orbitals and Multi-Electron Atoms | 5     |

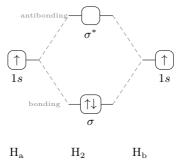

|     |         | 2.1.2 Molecular Orbital Theory                 | 8     |

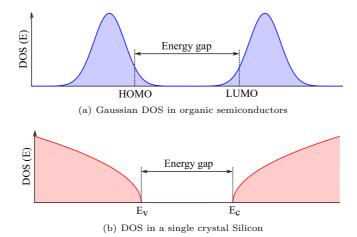

|     |         | 2.1.3 Organic Semiconductors                   | 9     |

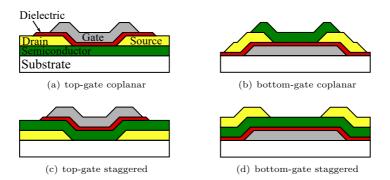

|     | 2.2     | Organic Thin-Film Transistors                  | 12    |

|     |         | 2.2.1 Architecture, Materials and Processing   | 13    |

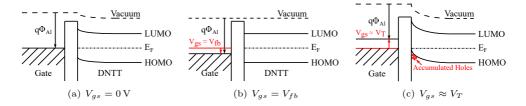

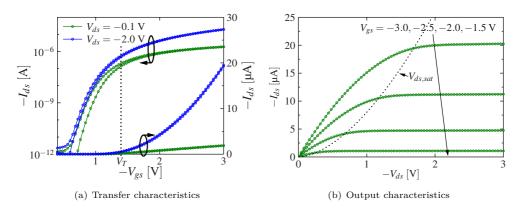

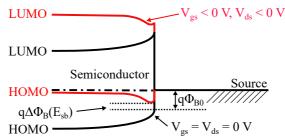

|     |         | 2.2.2 Operation Principle                      | 14    |

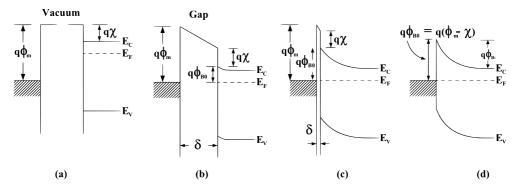

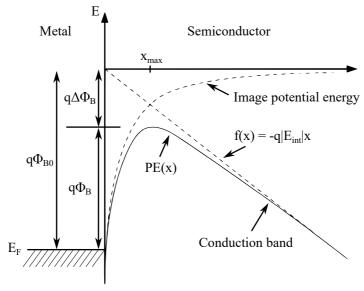

|     |         | 2.2.3 Metal-Semiconductor Contacts             | 16    |

|     | 2.3     | Short-Channel Effects in Organic TFTs          | 19    |

|     |         | 2.3.1 Contact Effects                          | 20    |

|     |         | 2.3.2 Threshold Voltage Roll-Off               | 20    |

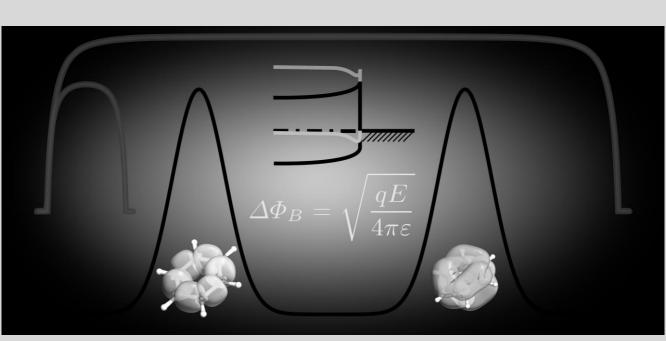

|     |         | 2.3.3 Drain-Induced Barrier Lowering           | 23    |

|     |         | 2.3.4 Subthreshold Slope Degradation           | 24    |

| 3   | Mat     | ematical Basics                                | 27    |

|     | 3.1     | Poisson's and Laplace's Equation               | 27    |

|     | 3.2     | Decomposition Strategy                         | 28    |

|     | 3.3     | Complex Potential Theory                       | 29    |

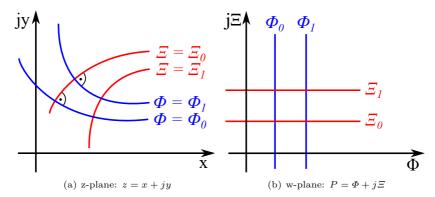

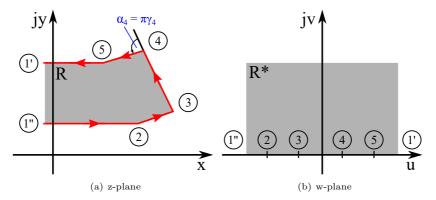

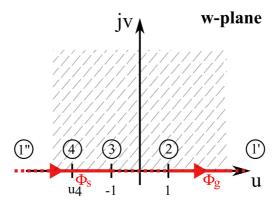

|     | 3.4     | Conformal Mapping                              | 31    |

|     |         | 3.4.1 Conformal Mapping of a Potential         | 31    |

|      | Cont                                                                                                  | ents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25   | 3.4.2 Schwarz-Christoffel Transformation                                                              | 32<br>33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

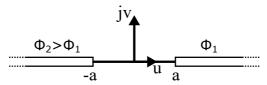

| 5.5  | Totelital Solution of a Geometry with Two Electrodes                                                  | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Gene | eric Charge-Based Compact DC Model                                                                    | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

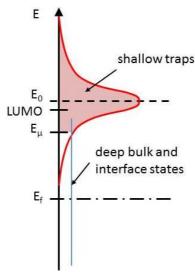

| 4.1  | Trap-Based Modelling                                                                                  | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.2  | Threshold Voltage Modelling Approach                                                                  | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.3  |                                                                                                       | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                                                                                       | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | ·                                                                                                     | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.6  | Trap-related Hysteresis Effect                                                                        | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

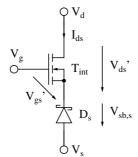

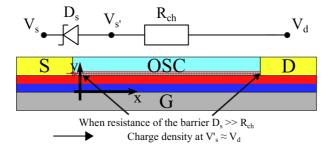

| Mod  | elling of Contact Effects                                                                             | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

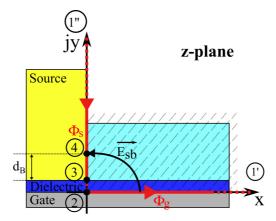

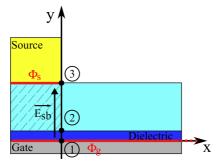

| 5.1  | Modelling of the Schottky Barrier at the Source Contact                                               | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.1.1 Decomposition of Poisson's Equation                                                             | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.1.2 Particular Solution of the Space Charges                                                        | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.1.3 Boundary Conditions                                                                             | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.1.4 Electric Field at the Schottky Barrier                                                          | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.1.5 Current Calculation and Model Implementation                                                    | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

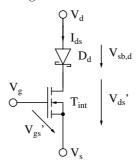

| 5.2  | Modelling of the Schottky Barrier at the Drain Contact $\ \ldots \ \ldots \ \ldots$                   | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Mod  | elling of Short Channel Effects                                                                       | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

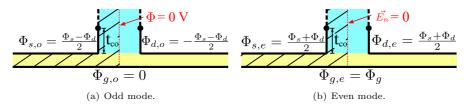

|      |                                                                                                       | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

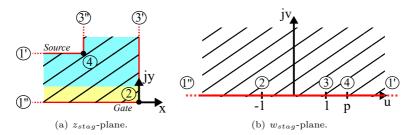

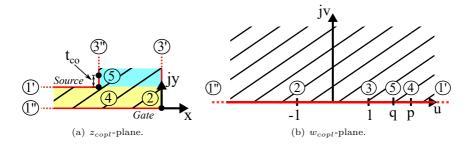

| 6.2  | -                                                                                                     | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.3  | Adapting a Potential Solution                                                                         | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

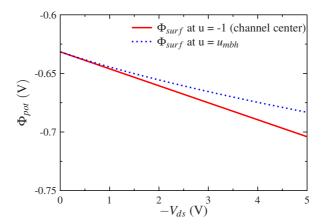

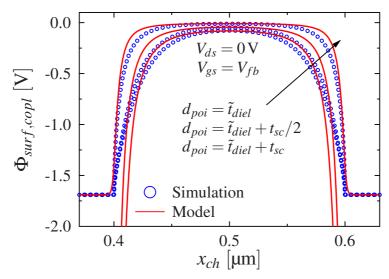

| 6.4  | Surface Potential                                                                                     | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.5  | Model Definition                                                                                      | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

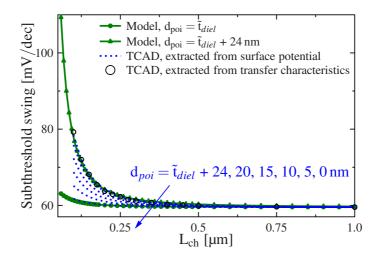

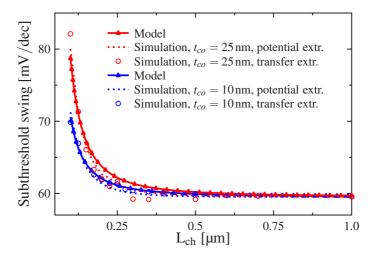

|      | 6.5.1 Subthreshold Swing                                                                              | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

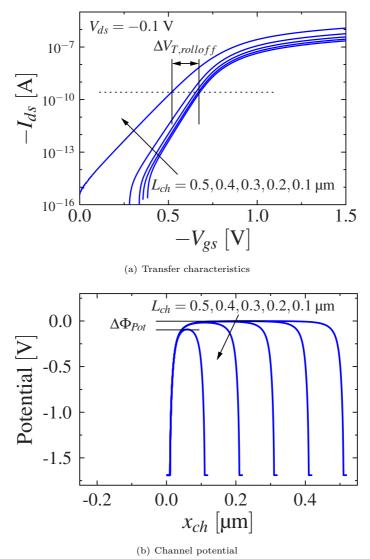

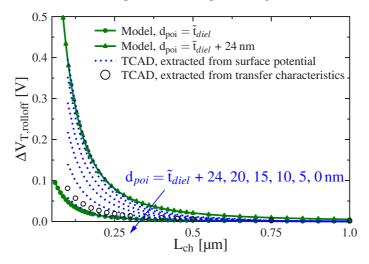

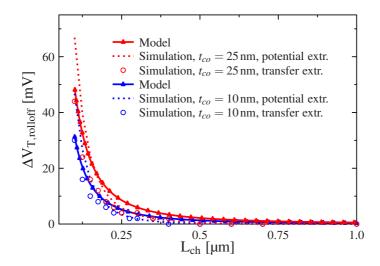

|      | 6.5.2 Threshold Voltage Roll-Off                                                                      | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

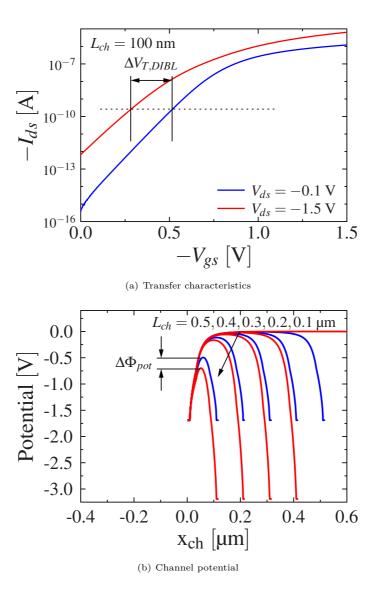

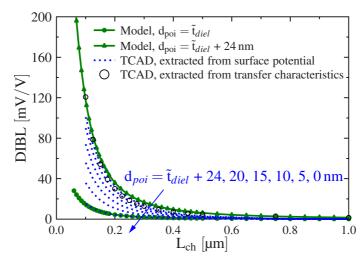

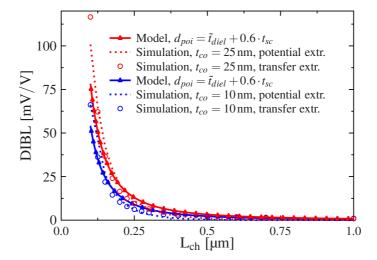

|      | 6.5.3 Drain-induced Barrier Lowering                                                                  | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

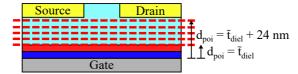

| 6.6  | Channel Location                                                                                      | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.7  | Implementation into Current Model                                                                     | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Resi | ults and Verification                                                                                 | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

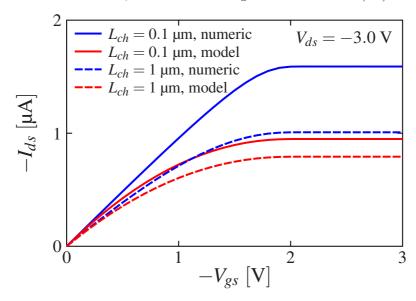

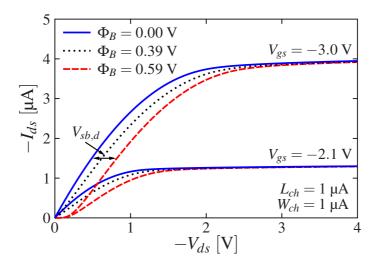

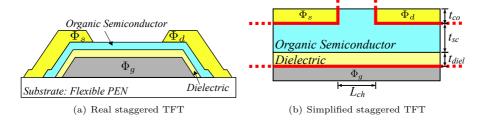

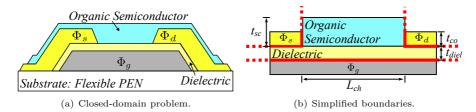

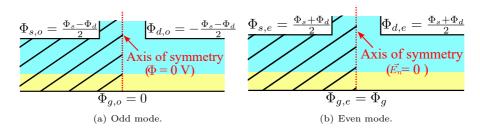

|      |                                                                                                       | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

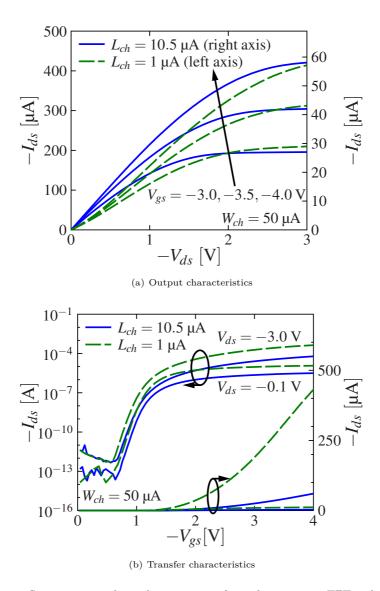

|      | ·                                                                                                     | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                                                                                       | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | <del></del>                                                                                           | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

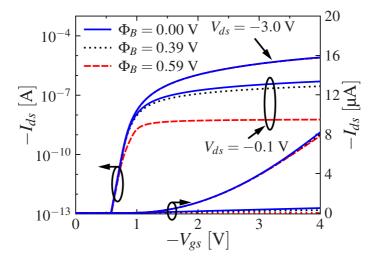

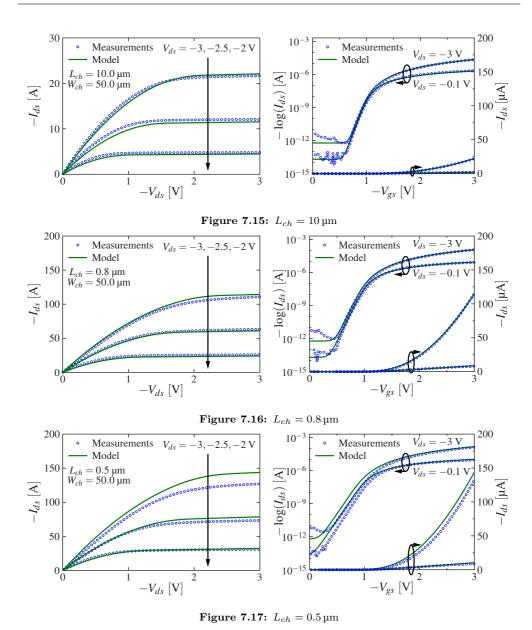

|      | Verification with Measurement Data                                                                    | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

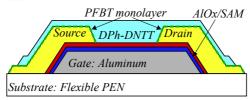

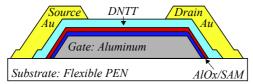

| 7.2  |                                                                                                       | 9111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7.2  |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

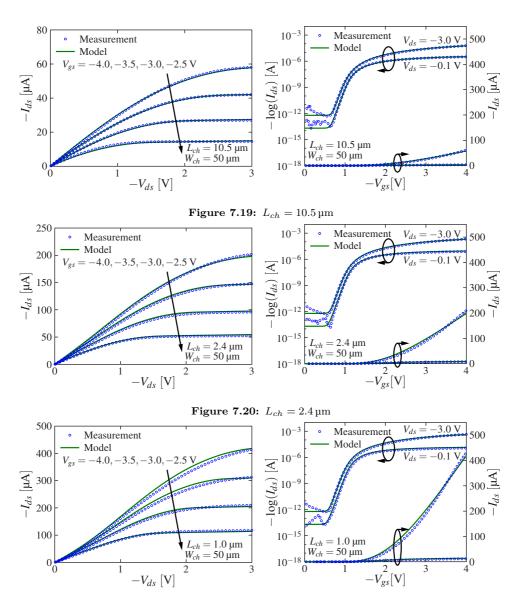

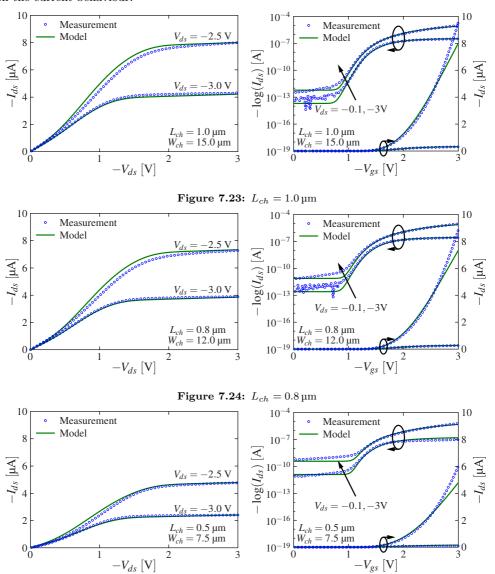

| 7.2  | 7.2.1 Coplanar Architecture: Short-Channel Models                                                     | 90<br>92<br>95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>Mod<br>5.1<br>5.2<br>Mod<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5 | 3.4.2 Schwarz-Christoffel Transformation 3.5 Potential Solution of a Geometry with Two Electrodes  Generic Charge-Based Compact DC Model 4.1 Trap-Based Modelling 4.2 Threshold Voltage Modelling Approach 4.3 Channel Lenght Modulation 4.4 Constant Contact Resistance Model 4.5 Power-Law Mobility Model 4.6 Trap-related Hysteresis Effect  Modelling of Contact Effects 5.1 Modelling of the Schottky Barrier at the Source Contact 5.1.1 Decomposition of Poisson's Equation 5.1.2 Particular Solution of the Space Charges 5.1.3 Boundary Conditions 5.1.4 Electric Field at the Schottky Barrier 5.1.5 Current Calculation and Model Implementation 5.2 Modelling of Short Channel Effects 6.1 Definition and Simplification of the Potential Problems 6.2 Conformal Mapping Functions 6.3 Adapting a Potential Solution 6.4 Surface Potential 6.5 Model Definition 6.5.1 Subthreshold Swing 6.5.2 Threshold Voltage Roll-Off 6.5.3 Drain-induced Barrier Lowering 6.6 Channel Location 6.7 Implementation into Current Model  Results and Verification 7.1 Verification by TCAD Simulation Data 7.1.1 Electrostatic Potential 7.1.2 Staggered Architecture 7.1.3 Coplanar Architecture |

| Co | ontents                | vi  |

|----|------------------------|-----|

|    |                        |     |

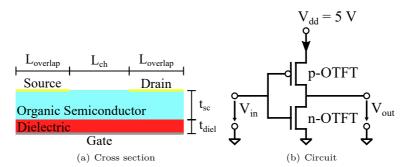

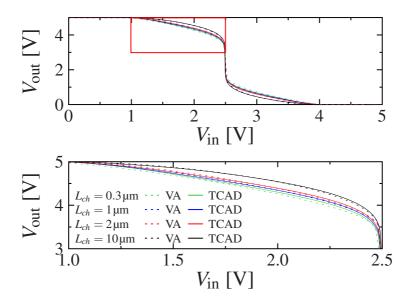

|    | 7.3 Circuit Simulation | 100 |

| 8  | Conclusion             | 103 |

| Re | eferences              | 107 |

viii Contents

#### List of Publications

#### Journals

Jakob Prüfer, Jakob Leise, James W. Borchert, Hagen Klauk, Ghader Darbandy, Aristeidis Nikolaou, Benjamín Iñíguez, Thomas Gneiting and Alexander Kloes, "Modelling the Short-Channel Effects in Coplanar Organic Thin-Film Transistors," in *IEEE Transactions* on *Electron Devices*, submitted and under review with mandatory revisions.

DOI: XXXX

Jakob Prüfer, Jakob Leise, Aristeidis Nikolaou, James W. Borchert, Ghader Darbandy, Hagen Klauk, Benjamín Iñíguez, Thomas Gneiting and Alexander Kloes, "Compact Modeling of Nonlinear Contact Effects in Short-Channel Coplanar and Staggered Organic Thin-Film Transistors," in *IEEE Transactions on Electron Devices*, vol. 68, issue 8, pp. 3843–3850, Aug. 2021.

DOI: 10.1109/TED.2021.3088770

Jakob Prüfer, Jakob Leise, Ghader Darbandy, Aristeidis Nikolaou, Hagen Klauk, James W. Borchert, Benjamín Iñíguez, Thomas Gneiting and Alexander Kloes, "Compact Modeling of Short-Channel Effects in Staggered Organic Thin-Film Transistors," in *IEEE Transactions on Electron Devices*, vol. 67, issue 11, pp. 5082–5090, Nov. 2020.

DOI: 10.1109/TED.2020.3021368

#### Conferences

Jakob Prüfer, Jakob Leise, Ghader Darbandy, James W. Borchert, Hagen Klauk, Benjamín Iñíguez, Thomas Gneiting and Alexander Kloes "Analytical Model for Threshold-Voltage Shift in Submicron Staggered Organic Thin-Film Transistors," in *International Conference on Mixed Design of Integrated Circuits and Systems (MIXDES) 2019*, pp. 71–75, Rzeszów, Poland, Jun. 2019.

DOI: 10.23919/MIXDES.2019.8787083

#### Co-Authorship

x List of Publications

Jakob Leise, Jakob Prüfer, Ghader Darbandy, Aristeidis Nikolaou, Michele Giorgio, Mario Caironi, Ute Zschieschang, Hagen Klauk, Alexander Kloes, Benjamín Iñíguez and James W. Borchert "Flexible megahertz organic transistors and the critical role of the device geometry on their dynamic performance," in *Journal of Applied Physics*, vol. 130, 125501, Sep. 2021.

DOI: 10.1063/5.0062146

Aristeidis Nikolaou, Jakob Leise, Jakob Prüfer, Ute Zschieschang, Hagen Klauk, Ghader Darbandy, Benjamín Iñíguez and Alexander Kloes "Variability-Aware Characterization of Current Mirrors Based on Organic Thin-Film Transistors on Flexible Substrates," in 28th International Conference on Mixed Design of Integrated Circuits and System (MIXDES), pp 56-60, Jun. 2021.

DOI: 10.23919/MIXDES52406.2021.9497595

Alexander Kloes, Jakob Prüfer, Jakob Leise, Aristeidis Nikolaou, Ghader Darbandy and Hagen Klauk "Compact Model for Short-Channel Organic Thin-Film Transistors with Extension for Non-Quasistatic Circuit Simulation and Variability Analysis," in ECS Meeting Abstracts, MA2021-01 1064, 2021.

DOI: 10.1149/MA2021-01321064mtgabs

Aristeidis Nikolaou, Jakob Leise, Jakob Prüfer, Ute Zschieschang, Hagen Klauk, Ghader Darbandy, Benjamín Iñíguez and Alexander Kloes "Noise-Based Simulation Technique for Circuit-Variability Analysis," in *IEEE Journal of the Electron Devices Society*, vol. 9, pp. 450–455, Dec. 2020.

DOI: 10.1109/JEDS.2020.3046301

Jakob Leise, Jakob Prüfer, Aristeidis Nikolaou, Ghader Darbandy, Hagen Klauk, Benjamín Iñíguez and Alexander Kloes "Macromodel for AC and Transient Simulations of Organic Thin-Film Transistor Circuits Including Nonquasistatic Effects," in *IEEE Transactions* on *Electron Devices*, vol. 67, issue 11, pp. 4672–4676, Nov. 2020.

DOI: 10.1109/TED.2020.3018094

Aristeidis Nikolaou, Ghader Darbandy, Jakob Leise, Jakob Prüfer, James W. Borchert, Michael Geiger, Hagen Klauk, Benjamín Iñíguez and Alexander Kloes "Charge-Based Model for the Drain-Current Variability in Organic Thin-Film Transistors Due to Carrier-Number and Correlated-Mobility Fluctuation," in *IEEE Transactions on Electron Devices*, vol. 67, issue 11, pp. 4667–4671, Nov. 2020.

DOI: 10.1109/TED.2020.3018694

Jakob Leise, Jakob Prüfer, Ghader Darbandy, Masoud Seifaei, Yiannos Manoli, Hagen Klauk, Ute Zschieschang, Benjamín Iñíguez and Alexander Kloes "Charge-Based Compact Modeling of Capacitances in Staggered Multi-Finger OTFTs," in *IEEE Journal of the Electron Devices Society*, vol. 8, pp. 396–406, Mar. 2020.

DOI: 10.1109/JEDS.2020.2978400

Aristeidis Nikolaou, Jakob Leise, Jakob Prüfer, Ute Zschieschang, Hagen Klauk, Ghader Darbandy and Alexander Kloes "Noise Based Variability Approach for DC Statistical Analysis of Organic TFT Based Circuits," in *IEEE Latin America Electron Devices* Conference (LAEDC) 2020, pp. 1–4, Feb. 2020.

DOI: 10.1109/LAEDC49063.2020.9073014

Ghader Darbandy, Christian Römer, Jakob Leise, Jakob Prüfer, James W. Borchert, Hagen Klauk and Alexander Kloes "Characterization of the Charge-Trap Dynamics in Organic Thin-Film Transistors," in *International Conference on Mixed Design of Integrated Circuits and Systems (MIXDES) 2019*, pp. 76–80, Rzeszów, Poland, Jun. 2019.

DOI: 10.23919/MIXDES.2019.8787105

Jakob Leise, Jakob Prüfer, Ghader Darbandy and Alexander Kloes "Charge-Based Compact Modeling of Capacitances in Staggered OTFTs," in *Latin American Electron Devices Conference (LAEDC) 2019*, pp 1-4, Armenia, Colombia, Feb. 2019.

DOI: 10.1109/LAED.2019.8714746

# List of Symbols

# Latin Alphabet

| Symbol            | Description                                                                        | Unit                                 |

|-------------------|------------------------------------------------------------------------------------|--------------------------------------|

| $\hat{H}$         | Hamilton operator                                                                  | [-]                                  |

| $\hat{E}$         | Eigenvalues of the wave functions                                                  | $[{\rm cm}^{-3/2}]$                  |

| q                 | Elementary charge                                                                  | [As]                                 |

| a                 | Parameter of the potential solution of the two-electrode geometry                  | [cm]                                 |

| $a_{stag,e}$      | Parameter $a$ in $P_{stag,e}$                                                      | [cm]                                 |

| $a_{stag,o}$      | Parameter $a$ in $P_{stag,o}$                                                      | [cm]                                 |

| $a_{copl,e}$      | Parameter $a$ in $P_{copl,e}$                                                      | [cm]                                 |

| $a_{copl,o}$      | Parameter $a$ in $P_{copl,o}$                                                      | [cm]                                 |

| $A^*$             | Richardson constant                                                                | $[\mathrm{Acm}^{-2}\mathrm{K}^{-2}]$ |

| $AlO_x$           | Aluminium oxide                                                                    | [-]                                  |

| $C_{diel}$        | Gate-dielectric capacitance                                                        | [F]                                  |

| $C_D$             | Depletion-layer capacitance                                                        | [F]                                  |

| $C_2H_4$          | Ethylene molecule                                                                  | [-]                                  |

| $C_2H_2$          | Acetylene molecule                                                                 | [-]                                  |

| $d_B$             | Representative barrier position                                                    | [cm]                                 |

| $D_d$             | Diode at the drain contact that models the Schottky barrier                        | [-]                                  |

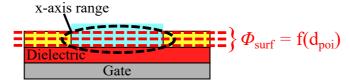

| $d_{poi}$         | Point of interest at which the potential is calculated by the short-channel models | [cm]                                 |

| $d_{poi,swing}$   | Point of interest of the subthreshold-swing-degradation model                      | [cm]                                 |

| $d_{poi,rolloff}$ | Point of interest of the threshold-voltage roll-off model                          | [cm]                                 |

| $d_{poi,DIBL}$    | Point of interest of the DIBL model                                                | [cm]                                 |

xiv List of Symbols

| $D_s$          | Diode at the source contact that models the Schottky barrier                    | [-]                  |

|----------------|---------------------------------------------------------------------------------|----------------------|

| $DOS_{Gauss}$  | Gaussian density of states distribution                                         | $[\mathrm{cm}^{-3}]$ |

| DIBL           | Drain-induced barrier lowering effect                                           | [V/V]                |

| E              | Energy                                                                          | [eV]                 |

| $ec{E}$        | Electric field vector within the region of interest                             | [V/cm]               |

| $E_c$          | Energy level of the conduction band                                             | [eV]                 |

| $E_{copl,w,e}$ | Electric field of the coplanar even mode in the $w_{copl}$ -plane               | [V/cm]               |

| $E_{copl,w,o}$ | Electric field of the coplanar odd mode in the $w_{copl}$ -plane                | [V/cm]               |

| $E_{copl,z,e}$ | Electric field of the coplanar even mode in the $z_{copl}$ -plane               | [V/cm]               |

| $E_{copl,z,o}$ | Electric field of the coplanar odd mode in the $z_{copl}$ -plane                | [V/cm]               |

| $E_{Fi}$       | Intrinsic Fermi level                                                           | [eV]                 |

| $E_F$          | Fermi level                                                                     | [eV]                 |

| $E_g$          | Energy gap between $E_c$ and $E_v$                                              | [eV]                 |

| $E_{int}$      | Electric field at the metal-semiconductor interface                             | [V/cm]               |

| $E_{sb,copl}$  | Electric field at the Schottky barrier at the source contact in a coplanar TFT  | [V/cm]               |

| $E_{sb,stag}$  | Electric field at the Schottky barrier at the source contact in a staggered TFT | [V/cm]               |

| $E_{stag,w,e}$ | Complex electric field of the staggered even mode in the $w_{stag}$ - plane     | [V/cm]               |

| $E_{stag,w,o}$ | Complex electric field of the staggered odd mode in the $w_{stag}$ - plane      | [V/cm]               |

| $E_{stag,z,e}$ | Complex electric field of the staggered even mode in the $z_{stag}$ - plane     | [V/cm]               |

| $E_{stag,z,o}$ | Complex electric field of the staggered odd mode in the $z_{stag}$ - plane      | [V/cm]               |

| $E_v$          | Energy level of the valence band                                                | [eV]                 |

| $E_w$          | Complex electric field in the w-plane (Schottky barrier model)                  | [V/cm]               |

| $E_x$          | Electric field within the region of interest in x-direction                     | [V/cm]               |

| $E_y$          | Electric field within the region of interest in y-direction                     | [V/cm]               |

| $E_z$          | Electric field in the z-plane (Schottky barrier model)                          | [V/cm]               |

| $E_0$          | Mean value of the Gaussian DOS                                                  | [eV]                 |

| $E_{\mu}$      | Transition energy between shallow traps and tail states                         | [eV]                 |

| F                   | Electrical force between two charges at the metal-semiconductor interface                                    | [qN/V]               |

|---------------------|--------------------------------------------------------------------------------------------------------------|----------------------|

| f                   | Particular function of Poisson's equation                                                                    | $[\mathrm{cm}^{-3}]$ |

| $f_e$               | Fermi-Dirac statistic function                                                                               | [-]                  |

| $f_{hys}$           | Fitting parameter of the trap-related hysteresis shift                                                       | [-]                  |

| $g_m$               | Transconductance of a transistor                                                                             | [S]                  |

| $\hbar$             | Reduced Planck constant                                                                                      | [eVs]                |

| $H_{a/b}$           | Hydrogen atoms                                                                                               | [-]                  |

| $H_2$               | Hydrogen molecule                                                                                            | [-]                  |

| $I_{ds}$            | Drain-source current                                                                                         | [A]                  |

| $I_{ds,bl}$         | Drain-source current calculated by a compact dc model a Schottky barrier height of zero at the drain contact | [A]                  |

| $I_{sb}$            | Current over a Schottky barrier                                                                              | [A]                  |

| $I_{sb,d}$          | Current density over the Schottky barrier at the drain contact                                               | [A]                  |

| $I_{sb,s}$          | Current density over the Schottky barrier at the source contact                                              | [A]                  |

| $I_{s,s}$           | Thermionic emission current of the Schottky diode at the source contact                                      | [A]                  |

| $I_{s,d}$           | Thermionic emission current of the Schottky diode at the drain contact                                       | [A]                  |

| $I_{TE}$            | Thermionic emission current                                                                                  | [A]                  |

| k                   | Boltzmann constant                                                                                           | $[{ m eV/K}]$        |

| l                   | Azimuthal quantum number                                                                                     | [-]                  |

| $L_c$               | Contact length in staggered TFTs                                                                             | [cm]                 |

| $L_{ch}$            | Channel length of a transistor                                                                               | [cm]                 |

| $L_{inj}$           | Current injection length at the source contact                                                               | [cm]                 |

| $L_{overlap}$       | Overlap length between the gate and the source/drain contacts in staggered TFTs $$                           | [cm]                 |

|                     |                                                                                                              |                      |

| $L_T$               | Transfer length in staggered TFTs                                                                            | [cm]                 |

| $L_T$ $m$           | Transfer length in staggered TFTs  Magnetic quantum number                                                   | [cm]<br>[-]          |

|                     | 0 00                                                                                                         |                      |

| m                   | Magnetic quantum number                                                                                      | [-]                  |

| $m \ m_e$           | Magnetic quantum number Mass of an electron                                                                  | [-]<br>[kg]          |

| $m$ $m_e$ $m_{max}$ | Magnetic quantum number  Mass of an electron  Maximum magnetic quantum number                                | [-]<br>[kg]<br>[-]   |

xvi

$N_{st}$ Equivalent shallow trap density  $[cm^{-3}]$  $[cm^{-3}]$  $N_{st0}$ Total states of the Gaussian DOS  $N'_{t}$  $[{\rm cm}^{-2}/({\rm eV})]$ Density of deep traps in the organic semiconductor per energy  $N'_{t,max}$ Number of tail states within the HOMO-LUMO energy gap  $[cm^{-2}]$  $[cm^{-2}]$  $N'_{t0}$ Amount of filled states per gate area PComplex potential function in the z-plane [V]  $\tilde{P}$ Complex potential function in the w-plane [V] Specific contact resistivity  $[\Omega]$  $p_c$  $P_{copl}$ Potential solution of the staggered TFT in the  $w_{copl}$ -plane [V] Complex Potential solution of the coplanar even mode in the [V] $P_{copl,e}$  $w_{conl}$ -plane Complex Potential solution of the coplanar odd mode in the [V]  $P_{copl,o}$  $w_{copl}$ -plane PEPotential energy at the metal-semiconductor interface [eV] Potential solution of the coplanar TFT in the  $w_{stag}$ -plane [V]  $P_{stag}$ Complex Potential solution of the staggered even mode in the [V]  $P_{stag,e}$  $w_{stag}$ -plane [V] $P_{stag,o}$ Complex Potential solution of the staggered odd mode in the  $w_{stag}$ -plane  $P_w$ Complex potential solution in the w-plane (Schottky barrier [V]model) Atomic p-orbital in x-direction [-] $p_x$ Atomic p-orbital in y-direction [-] $p_{v}$ Atomic p-orbital in z-direction [-] $p_z$ Coordinate of point 5 in the  $w_{copl}$ -plane [cm]qFitting parameter of the coordinate of point 5 in the  $w_{copl}$ -[-] $q_{co}$  $Q'_m$  $[cm^{-3}]$ Mobile charge-carrier density  $[As/cm^3]$  $Q'_{m,d}$ Mobile charge-carrier density at the drain contact  $Q'_{m,s}$ Mobile charge-carrier density at the source contact  $[As/cm^3]$  $Q'_{m,s/d,OFF}$ Mobile charge-carrier density in the off state at the drain or  $[As/cm^3]$ source contacts  $Q'_t$  $[As/cm^3]$ Charge-carrier density in tail states RRegion of interest of a potential problem [-]

List of Symbols

| r                      | Radial distance of an electron to the nucleus                             | [cm]                   |

|------------------------|---------------------------------------------------------------------------|------------------------|

| $R_c$                  | Constant contact resistance                                               | $[\Omega]$             |

| $R_{c,total}$          | Total contact resistance                                                  | $[\Omega]$             |

| $R_{ch}$               | Channel resistance                                                        | $[\Omega]$             |

| $R_{n,l}$              | Radial function of the wave function                                      | $[\mathrm{cm}^{-3/2}]$ |

| $R_{sb,s}$             | Field-dependent resistance of the Schottky barrier at the source contact  | $[\Omega]$             |

| $R_{sh}$               | Sheet resistance of the semiconductor layer                               | $[\Omega]$             |

| s                      | Spin quantum number                                                       | [-]                    |

| S                      | Subthreshold swing                                                        | [V/dec]                |

| $S_{obs}$              | Observed subthreshold swing in current-voltage characteristics            | [V/dec]                |

| $S_{sc,copl}$          | Degraded subthreshold swing in short-channel coplanar TFTs                | [V/dec]                |

| $S_{sc,stag}$          | Degraded subthreshold swing in short-channel staggered TFTs               | [V/dec]                |

| $S_{total}$            | Subthreshold swing degraded by short-channel and trap-<br>related effects | [V/dec]                |

| T                      | Temperature                                                               | [K]                    |

| $t_{air}$              | Thickness of the air region above the organic semiconductor               | [cm]                   |

| $t_{ch}$               | Thickness of the transistor channel                                       | [cm]                   |

| $t_{co}$               | Thickness of the source and the drain contacts                            | [cm]                   |

| $t_{diel}$             | Thickness of the gate dielectric layer                                    | [cm]                   |

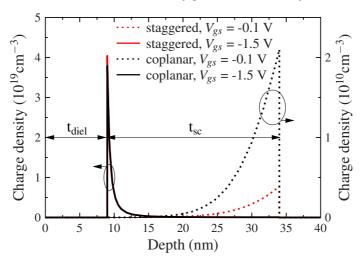

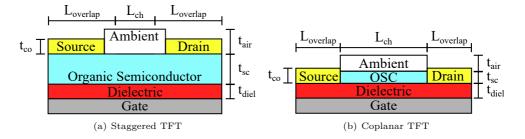

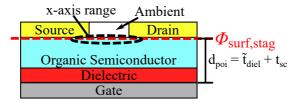

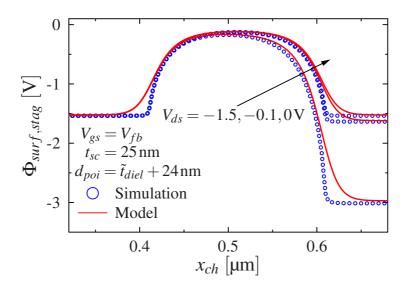

| $	ilde{t}_{diel}$      | Stretched thickness of the gate dielectric layer                          | [cm]                   |