# ACCELERATION OF AUTOMATIC SPEECH RECOGNITION FOR LOW-POWER DEVICES

Dennis Pinto Rivero

Doctor of Philosophy

Department of Computer Architecture Universitat Politècnica de Catalunya

Advisors: Jose-Maria Arnau, Antonio González

April, 2022 Barcelona, Spain

# Abstract

Machine learning approaches are transforming the landscape of computing and beyond. Among them, *Automatic Speech Recognition (ASR)* is specially eye-catching. Ingrained in the public imagination as the cornerstone of human-machine interaction, speech recognition is set to become a game-changing technology with potential for broad adoption among the general public. Fueled by the remarkable accuracy obtained by current ASR systems, it will likely disrupt, sooner than later, how we interact with all kinds of machines. Today, we are experiencing the early stages of this disruption as can be seen in examples such as smart speakers and AI assistants, dictation engines embedded in virtual keyboards and devices for real-time language translation.

It requires discipline to avoid getting carried away by the promises of a once science-fiction technology. The prospects are, indeed, existing. However, before ASR can momentarily drop the jaws of users in awe and then slowly fade into the background of amazing technologies taken for granted, there are still many challenges ahead. ASR engines are powered by extremely expensive algorithms in terms of computational cost. Decoding a second of speech takes in the order of billions of arithmetic operations. In contrast, devices such as smartphones, smartwatches and other wearables, which are likely the perfect fit for ASR, generally rely on small batteries and operate with very low power. Hence, they often lack the computing power necessary for real-time ASR. Consequently, the current approach to decode speech consists of performing ASR in powerful server computers, relegating the edge device to the role of merely capturing the audio signal. However, given the limitations of this approach, it is seen by many as a workaround until ASR can be completely deployed on the edge.

In this thesis, we study the challenges preventing ASR deployment on edge devices and propose innovations to tackle them, hopefully moving the technology a step forward to the future. First, we characterize state-of-the-art hybrid DNN-HMM. In Hybrid DNN-HMM, the transcription is obtained by searching for the most likely sequence in a large graph that contains every possible transcription. The signal is broken down into frames and then a neural network analyzes each of them. The neural network computes a score for each node of the graph. These scores represent how well each node matches the audio frame. After analyzing the bottlenecks of this ASR system, by characterizing its execution on a representative low-power platform, we propose a heterogeneous platform that contains an accelerator to perform the DNN inference and another accelerator to perform the graph search. This approach results in 4.5x faster execution and 4.3x less energy consumption when compared to a baseline CPU-GPU low-power platform.

To further improve the performance of ASR, we then look into the run-time properties specific to ASR. When ASR is executed on the edge, it is generally expected to decode audio in a streaming way, generating and expanding a partial transcription while the user is still speaking. In this case, the ASR system analyzes the signal frames one at a time. During each of these decoding steps, it generates a set of partial transcriptions or transcription hypotheses. These hypotheses are expanded during the decoding step by appending new symbols. Additionally, some hypotheses converge into a single hypothesis while others diverge into a multitude of different hypotheses. This creates a difference between decoding steps. During some decoding steps, the system contains many hypotheses whereas, in other steps, the number of hypotheses may be significantly lower. We determine that the number of hypotheses, which can be understood as the confidence of the ASR decoder, can be leveraged by reducing the arithmetic precision of the computations during high confidence steps and increasing it during low confidence steps. According to our results, our technique provides 19.5% reduction in execution time while also reducing the energy consumption by about 16.9%, compared to the heterogeneous platform previously described, with degradation of accuracy below 1%.

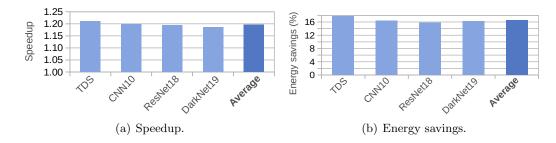

Hybrid DNN-HMM ASR systems provide outstanding transcription accuracy even in challenging benchmarks. However, Hybrid DNN-HMM ASR is not the only approach to ASR. End-to-end ASR systems have recently reached state-of-the-art accuracy. The assumptions ingrained in endto-end systems are more relaxed than those of hybrid systems and the mechanism to train them is more automatic and requires less expert knowledge. For these reasons, many believe that end-toend systems hold a powerful edge over hybrid systems. For us, that makes them worth studying. These systems are based on large neural networks that are trained to generate the set of hypotheses by themselves. These systems generally include a graph search, as well, but a simpler one. Along with learning how to recognize signal frames, the neural network is trained to learn lexical and language relationships between sounds. Neurons in state-of-the-art neural networks are often activated with a ReLU function, which generates, during run-time, abundant zeros. We design Mixture-of-Rookies, a prediction scheme to detect at run-time when a neuron is going to generate a zero. This technique is embedded in a neural network accelerator that avoids computing the neurons when they are predicted to generate a zero. We estimate that this approach can provide a speedup of 1.21x while consuming 17.7% less energy than a baseline accelerator, for a specific end-to-end system. Furthermore, as many neural networks used for other applications contain ReLU, we evaluate our technique with different neural networks and determine that it can provide significant benefits across the board.

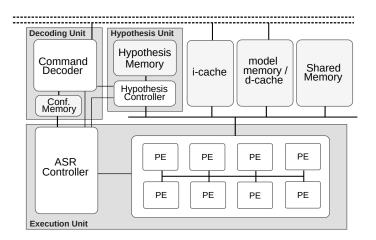

After proposing the previous optimizations, we tackle a different challenge of ASR deployment in low-power devices. ASR is a fast-changing technology and can be expected to continue changing fast as more innovations are proposed. Furthermore, there are many alternative approaches to ASR. Beyond the high-level categories of Hybrid or end-to-end, there are minor variations with often significant impact on transcription accuracy. As more research is conducted, new techniques will keep fine-tuning the algorithms and models for specific use-cases, resulting in a rich collection of alternative systems and techniques for speech recognition. However, this creates an additional challenge for computer architects. An accelerator designed to execute a very specific ASR system will provide huge performance gains but, at the same time, restrict the platform to execute a single ASR system. Furthermore, it risks becoming quickly obsolete, once new ASR techniques hit the market. To tackle this challenge, we propose ASRPU, a programmable ASR accelerator that, taking inspiration from GPUs, enables efficient execution of a wide range of ASR systems and provides a convenient programming model that enables ASR systems to be easily implemented. Our results show that ASRPU can execute state-of-the-art ASR in real-time while consuming less than 1.8 W. According to our estimations, the entire accelerator fits in about 12  $\rm mm^2$  when built from 32 nm cell nodes.

The proposals in this thesis represent innovative ways in which computer architecture can push forward the adoption of ASR by the broad public. All these techniques make the execution of ASR systems more amenable for low-power devices, enabling the deployment of state-of-the-art ASR on the edge.

# Resumen

Las soluciones basadas en aprendizaje automático están transformando el mundo de la computación. Entre estas, el reconocimiento automático de voz resalta al formar parte del imaginario popular como la forma ideal de interacción con las máquinas. El reconocimiento de voz va de camino a convertirse en una tecnología revolucionaria.

Sin embargo, antes de que los sistemas de reconocimiento de voz puedan utilizarse de manera generalizada, hay muchos desafios que resolver. Los motores de reconocimiento de voz consisten en algoritmos extremadamente caros a nivel computacional. Decodificar un segundo de audio requiere del orden de miles de millones de operaciones aritméticas por segundo. En contraste, los dispositivos que encajan mejor con applicaciones de reconocimiento de voz, como smartphones y weareables, generalmente operan a muy bajo consumo y conectados a una batería, por lo que suelen carecer de la capacidad para ejecutar los sistemas de reconocimiento de voz a tiempo real. Consequentemente, la mayoría de las veces, los algoritmos de reconocimiento de voz se ejecutan en servidores y el dispositivo de bajo consumo tan solo se emplea para capturar el audio y comunicarse con el servidor. Los problemas de seguridad y privacidad, junto con otras limitaciones de este procedimiento, llevan a que mucha gente lo vea como una solución temporal. Idealmente, el reconocimiento de voz sería realizado en el propio dispositivo.

En esta tesis, estudiamos los desafíos que impiden el despliege de los sistemas de reconocimiento de voz en dispositivos de bajo consumo y proponemos innovaciones para solucionarlos. Primero, caracterizamos un sistema estado-del-arte basado en el modelo "hybrid HMM-DNN ASR" ejecutado en una plataforma de bajo consumo. En este tipo de sistemas, la transcripción se obtiene buscando la secuencia con mayor probabilidad en un grafo de decodificación que contiene todas las transcripciones posibles. La señal primero se divide en "frames" y una red neuronal los analiza para obtener una distribución de probabilidad sobre unidades acústicas, llamada "score" acústico. Después de analizar el sistema, proponemos una plataforma heterogénea que contiene una CPU y varios chips específicos para acelerar la búsqueda en el grafo de decodificación y la inferencia de la red neuronal. Al comparar la ejecución en esta plataforma con la ejecución en un sistema base, hemos comprobado que la plataforma heterogénea resulta en una mejora de 4.5x en tiempo de ejecución y una reducción de 4.3x en el consumo de energía.

Para seguir mejorando el rendimiento de esta plataforma, proponemos una técnica que aprovecha una propiedad dinámica de los sistemas de reconocimiento de voz que llamamos "decoder confidence". A medida que el sistema de reconocimiento va decodificando un audio, este va generando transcripciones alternativas o "hipótesis". Para esta técnica, asumimos que cuando el sistema considera un número bajo de hipótesis su "confianza" es alta, y cuando considera un número alto de hipótesis, su "confianza" es baja. Usando esta información, ajustamos la precisión numérica empleada durante la inferencia de la red neural, ahorrando tiempo de ejecución y energía cuando la precisión es menor, principalmente al reducir los accessos a memoria principal. En nuestros experimentos, esta técnica resulta en una reducción del 19.5% en tiempo de ejecución y una redución del 17.7% en consumo energético, con un aumento del porcentaje de errores en la transcripción inferior al 1%.

En nuestro siguiente trabajo estudiamos un sistema de reconocimiento de voz del tipo "end-toend". Estos sistemas consisten en una red neural más grande y completa que genera directamente las transcripciones. Debido a la simplicidad del entrenamiento de estos sistemas comparado con los sistemas "hybrid", junto a otras ventajas que presentan, los sistemas "end-to-end" han ganado popularidad en los últimos años y muchos de ellos ya alcanzan resultados estado-del-arte. En esta técnica, aprovechamos que la mayoría de estos sistemas emplean funciones ReLU como activación para las capas internas de la red neuronal. Esta función de activación genera un abundante número de ceros en tiempo de ejecución. En esta técnica, proponemos un predictor, llamado "Mixture-ofrookies" que detecta de antemano cuando la ejecución de una neurona va a resultar en cero. Cuando se da el caso, en vez de ejecutar la neurona, escribimos un cero a su salida, ahorrándonos los cálculos y accesos a memoria que requiere el cálculo de la misma. Para probar que esta técnica se puede aplicar a otros ámbitos, probamos su efectividad en otras redes neuronales de reconocimiento de imágenes, aparte de la red neuronal para reconocimiento de voz. A través de los experimentos que hemos realizado, estimamos que esta técnica proporciona un "speedup" de 1.21x y una redución del 17.7% en consumo de energía de media.

Tras proponer las optimizaciones anteriores, decidimos enfrentarnos a un desafio diferente. En nuestro último trabajo, diseñamos un accelerador específico para reconocimiento de voz que sea capaz de ejecutar el sistema completo. Nuestro enfoque consiste en proporcionar la máxima flexibilidad, que le permita ejecutar cualquier sistema de reconocimiento de voz, mientras aprovechamos características comunes a la mayoría de sistemas para optimizar su ejecución mediante unidades hardware especializadas. Este acelerador, llamado ASRPU, consiste en un conjunto de unidades de cómputo programables y una serie de unidades específicas y controladores, junto a una jerarquía de memoria optimizada para reconocimiento de voz. De acuerdo con nuestros modelos, una configuración de 1.8W y 12mm<sup>2</sup> puede ejecutar sistemas de reconocimiento de voz estado-del-arte en tiempo real.

# Keywords

Automatic Speech recognition, Real-Time, Hardware Accelerator, Low-Power Architecture, Edge computing.

# Acknowledgements

I wish to start this dedication by acknowledging and expressing my gratitude to Prof. Antonio González and Dr Jose María Arnau, my advisors, for the role that they played during these years. Thank you for your continuous support and patience and for sharing your extensive knowledge and deep insight. I am very thankful for the opportunity to start my research career at ARCO and for providing me with financial support, for all the fruitful ideas and all the insightful discussions we had.

Again, thank you for the opportunity to work in such an open and creative environment. Your endless enthusiasm and optimism were truly essential to me.

To all the people from the ARCO group. To the professors Jordi, Juan Luis and Llorençs. Thank you for the support throughout these years and the interesting discussions during the group meetings. To Andreas, Franyell and Marc, the post-docs of the group. I am truly thankful for all the interesting conversations we had and the moments we shared. Your paths have been an inspiration for me.

To my wonderful collegues at ARCO: Reza, Martí, Albert, David, Diya, Raúl, Pedro, Jorge, Mohammad, Bahareh, Mojtaba, Rodrigo, Aurora, Imad and Nitesh. I can not emphasize enough how thankful I am for all the good times we shared, for those conversations during lunch, for sharing the toll during the long hours at the lab before deadlines, for the beers (and Fantas) that we had and for those that we could not have, for sharing with me your experiences and your amazing knowledge and insight. I always feel impressed by your achievements and endurance and humbled by how nice and generous your all are. I wish you the best of luck. I am sure that you all will do great at anything you pursue.

To my dear friends, Borja and Germán, and the good times we shared playing online and keeping in touch despite the distance. You always manage to put a smile on my face. Sebas, I want to especially thank you for your support and encouragement during all these years. We have shared so much of our lives and influenced each other so deeply that I can only regard you and Katy as family. I also want to thank my friends Juanlu and Cris for the great moments we shared in Barcelona. It is amazing how life keeps bringing us together again and again. I am sure we will continue to nurture our friendship for many years to come.

To my family. My dear sisters, Sheyla and Yanira, with whom I shared many great memories. Thank you for being there, encouraging me to pursue my dreams. Growing up together with you and learning together how to live and how to be good persons is the best experience I could ask. To my loving mother, Trinidad, who always stood by my side, believing in me. You taught me the value of being a good person, of accepting and understanding others, no matter what. You are always on the other side of the phone when I most need it. When life feels discouraging and lonely, the memories I have of my childhood with you really spar a beam of light. To my grandparents, Juan and María. You are examples of endurance, patience and good-will. You inspired me to become who I am today. I always looked up to you and I will always continue to do so.

Finally, I admittedly own more than I can give back to my dearest companion, my fiancée, Mengting. For your continuous support, patience and understanding. For your endless love and care. For encouraging me to be brave and confident. You have stood by my side during all these years and for that, I am most grateful and humbled.

The love of my family and friends shaped my identity and my view of the world and for that I could not be more grateful to them. Thank you.

This thesis is dedicated to my mother for her endless love, support and encouragement.

# Contents

| 1 | Intr | oducti | ion                                        | 23 |

|---|------|--------|--------------------------------------------|----|

|   | 1.1  | Motiva | ation                                      | 23 |

|   | 1.2  | Proble | em Statement, Objectives and Contributions | 25 |

|   |      | 1.2.1  | A Heterogeneous System for low-power ASR   | 27 |

|   |      | 1.2.2  | Leverage Run-time Decoding Confidence      | 28 |

|   |      | 1.2.3  | Detect and Remove Ineffectual Computations | 29 |

|   |      | 1.2.4  | A Programmable Architecture for ASR        | 31 |

|   | 1.3  | Relate | d Work                                     | 32 |

|   |      | 1.3.1  | Early Proposals                            | 32 |

|   |      | 1.3.2  | Beam Search Acceleration                   | 33 |

|   |      | 1.3.3  | DNN Acceleration                           | 34 |

|   | 1.4  | Docum  | nent Organization                          | 35 |

| 2 | Bac  | kgrou  | nd on Automatic Speech Recognition         | 37 |

|   | 2.1  | Auton  | natic Speech Recognition                   | 37 |

|   |      | 2.1.1  | Feature Extraction                         | 38 |

|   | 2.2  | Hybrid | d HMM-DNN                                  | 39 |

|   |      | 2.2.1  | Time-Delay Neural Network (TDNN)           | 41 |

|   |      | 2.2.2  | Decoding Graph                             | 42 |

|   |      | 2.2.3  | Viterbi Decoding                           | 43 |

|   | 2.3  | End-to | p-End ASR                                  | 44 |

# CONTENTS

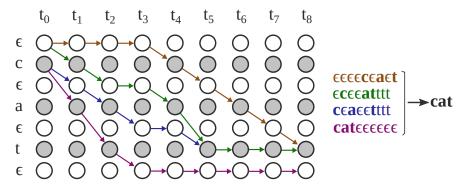

|   |     | 2.3.1   | Connectionist Temporal Classification (CTC) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 45 |

|---|-----|---------|------------------------------------------------------------------------------------------------|----|

|   |     | 2.3.2   | Time-Depth Separable Neural Network (TDS)                                                      | 45 |

|   |     | 2.3.3   | Decoding                                                                                       | 46 |

|   | 2.4 | LM Re   | -scoring                                                                                       | 46 |

| 3 | Exp | erimer  | atal Methodology                                                                               | 49 |

|   | 3.1 | CPU a   | nd GPU                                                                                         | 49 |

|   | 3.2 | Hardw   | are models                                                                                     | 50 |

|   | 3.3 | Progra  | mming frameworks                                                                               | 51 |

|   | 3.4 | ASR B   | enchmarks                                                                                      | 52 |

| 4 | A L | ow-pov  | ver Heterogeneous Platform for ASR                                                             | 53 |

|   | 4.1 | TDNN    | system                                                                                         | 53 |

|   |     | 4.1.1   | Recognition Accuracy                                                                           | 54 |

|   |     | 4.1.2   | Memory                                                                                         | 55 |

|   | 4.2 | Hardw   | are Platform                                                                                   | 55 |

|   |     | 4.2.1   | DNN accelerator                                                                                | 56 |

|   |     | 4.2.2   | Viterbi Accelerator                                                                            | 57 |

|   | 4.3 | Experi  | mental Results                                                                                 | 59 |

|   |     | 4.3.1   | Execution Time                                                                                 | 61 |

|   |     | 4.3.2   | Power Consumption                                                                              | 63 |

| 5 | Lev | erage I | Run-time Beam Search Confidence                                                                | 65 |

|   | 5.1 | Analys  | is of Bottlenecks                                                                              | 65 |

|   |     | 5.1.1   | Energy Bottleneck                                                                              | 65 |

|   |     | 5.1.2   | Performance Bottleneck                                                                         | 66 |

|   |     | 5.1.3   | Optimize DNN inference                                                                         | 66 |

|   | 5.2 | Dynam   | nic DNN Precision                                                                              | 67 |

|   |     | 5.2.1   | Dynamic Threshold Computation                                                                  | 70 |

# CONTENTS

|   |     | 5.2.2 Changes to the DNN Accelerator            | 71  |

|---|-----|-------------------------------------------------|-----|

|   |     | 5.2.3 Changes to the Beam Search Accelerator    | 73  |

|   | 5.3 | Experimental Results                            | 73  |

|   |     | 5.3.1 Performance Gains of Dynamic Precision AM | 73  |

|   |     | 5.3.2 Effect on Accuracy                        | 75  |

| 6 | Pre | icting ReLU outputs to Skip DNN Computations    | 77  |

|   | 6.1 | TDS System                                      | 77  |

|   | 6.2 | ReLU Activations in DNNs                        | 78  |

|   | 6.3 | ReLU Output Predictor                           | 79  |

|   | 6.4 | DNN Accelerator with ReLU Output Predictor      | 86  |

|   |     | 6.4.1 Control Unit                              | 87  |

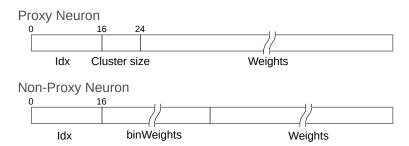

|   |     | 6.4.2 DNN Format                                | 88  |

|   |     | 6.4.3 Compute Units                             | 89  |

|   |     | 6.4.4 Binary Prediction Unit                    | 89  |

|   | 6.5 | Results                                         | 89  |

| 7 | Pro | rammable Low-Power Architecture for ASR         | 93  |

|   | 7.1 | Architecture of ASRPU                           | 93  |

|   |     | 7.1.1 Decoding on ASRPU                         | 94  |

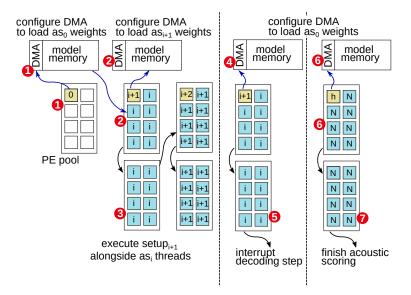

|   |     | 7.1.2 Setup Thread                              | 95  |

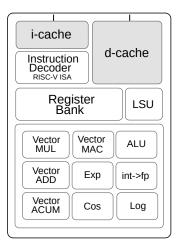

|   |     | 7.1.3 Execution Unit                            | 96  |

|   |     | 7.1.4 Processing Elements                       | 97  |

|   |     | 7.1.5 Hypothesis unit                           | 98  |

|   |     | 7.1.6 Memory Hierarchy                          | 98  |

|   |     | 7.1.7 Command Decoder                           | 99  |

|   | 7.2 | Case Study                                      | 99  |

|   |     | 7.2.1 The Main Process                          | 100 |

# CONTENTS

|   |     | 7.2.2  | Acoustic Scoring          | . 101 |

|---|-----|--------|---------------------------|-------|

|   |     | 7.2.3  | Hypothesis Expansion      | . 101 |

|   | 7.3 | Evalua | ation                     | . 102 |

|   |     | 7.3.1  | Methodology and Scope     | . 102 |

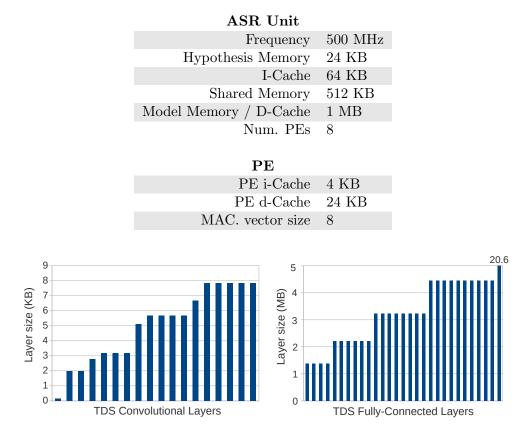

|   |     | 7.3.2  | Accelerator Configuration | . 102 |

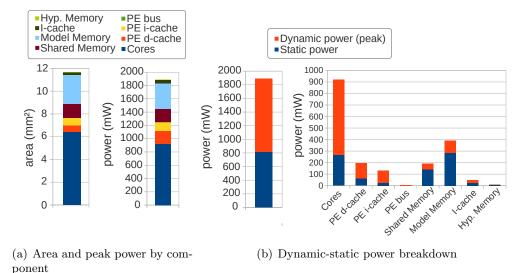

|   |     | 7.3.3  | Area and Power            | . 103 |

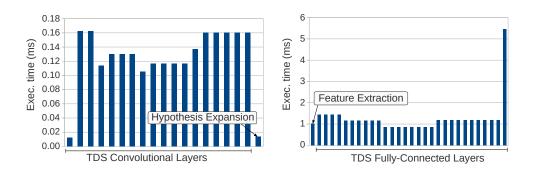

|   |     | 7.3.4  | Performance               | . 104 |

|   |     |        |                           |       |

| 8 | Con | clusio | ns and Future Work        | 107   |

|   | 8.1 | Conclu | usions                    | . 107 |

|   | 8.2 | Contri | butions                   | . 109 |

|   | 8.3 | Future | e Work                    | . 110 |

# List of Figures

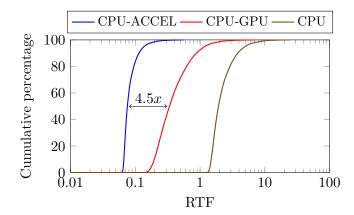

| <ul> <li>1.3 Performance of all the utterances in the librispeech test and dev sets decoded by the Kaldi TDNN ASR system on three architectures: CPU, CPU-GPU and CPU-ACCEL. The left-most plot shows the time it took to decode each utterance, where the right-most figure shows the Real Time Factor (RTF). The RTF is the decoding time divided by the utterance time (lower means better)</li></ul>                                       | 1.1 | Word Error Rate (WER) of different ASR systems on the librispeech test-clean and test-other benchmarks [7].                                                                                                                                                 | 24 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>the Kaldi TDNN ASR system on three architectures: CPU, CPU-GPU and CPU-ACCEL. The left-most plot shows the time it took to decode each utterance, where the right-most figure shows the Real Time Factor (RTF). The RTF is the decoding time divided by the utterance time (lower means better)</li></ul>                                                                                                                             | 1.2 | transformed into features, and then into acoustic scores. The decoder combines the acoustic scores with the decoding graph to obtain the most likely transcription for                                                                                      | 26 |

| <ul> <li>1.5 Number of hypotheses expanded at each frame during the decoding of 10 seconds of speech</li></ul>                                                                                                                                                                                                                                                                                                                                 | 1.3 | the Kaldi TDNN ASR system on three architectures: CPU, CPU-GPU and CPU-ACCEL. The left-most plot shows the time it took to decode each utterance, where the right-most figure shows the Real Time Factor (RTF). The RTF is the decoding                     | 27 |

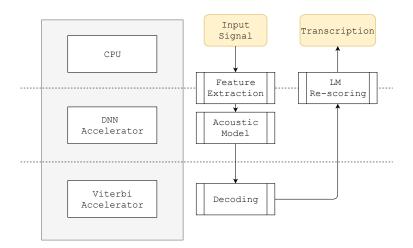

| <ul> <li>speech</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.4 | ASR pipeline on the proposed hardware platform.                                                                                                                                                                                                             | 28 |

| <ul> <li>1.7 Architecture of ASRPU</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                   | 1.5 |                                                                                                                                                                                                                                                             | 30 |

| <ul> <li>2.1 Algorithm to compute Mel-Frequency Cepstral Coefficient (MFCC)</li></ul>                                                                                                                                                                                                                                                                                                                                                          | 1.6 | Speedup obtained by the mixture-of-rookies technique on a set of DNN tasks                                                                                                                                                                                  | 31 |

| <ul> <li>2.2 Relation between linear frequency domain and Mel frequency domain 4</li> <li>2.3 A Time-Delay Neural Network (TDNN) is a chain of Fully connected (FC) layers whose input is a concatenation of several outputs from the previous layer. In this example, each layer depends on the output from the previous layer at t-2, t and t+2. The output of this TDNN at t is computed from the input window (t-8, t+8), which</li> </ul> | 1.7 | Architecture of ASRPU                                                                                                                                                                                                                                       | 32 |

| 2.3 A Time-Delay Neural Network (TDNN) is a chain of Fully connected (FC) layers whose input is a concatenation of several outputs from the previous layer. In this example, each layer depends on the output from the previous layer at t-2, t and t+2. The output of this TDNN at t is computed from the input window (t-8, t+8), which                                                                                                      | 2.1 | Algorithm to compute Mel-Frequency Cepstral Coefficient (MFCC).                                                                                                                                                                                             | 39 |

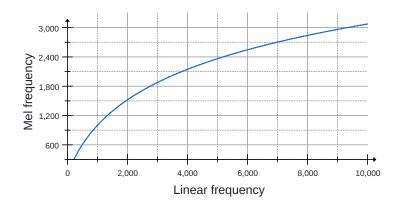

| whose input is a concatenation of several outputs from the previous layer. In this example, each layer depends on the output from the previous layer at t-2, t and t+2. The output of this TDNN at t is computed from the input window (t-8, t+8), which                                                                                                                                                                                       | 2.2 | Relation between linear frequency domain and Mel frequency domain                                                                                                                                                                                           | 40 |

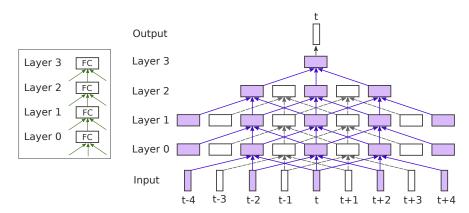

|                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.3 | whose input is a concatenation of several outputs from the previous layer. In this example, each layer depends on the output from the previous layer at t-2, t and t+2. The output of this TDNN at t is computed from the input window $(t-8, t+8)$ , which | 41 |

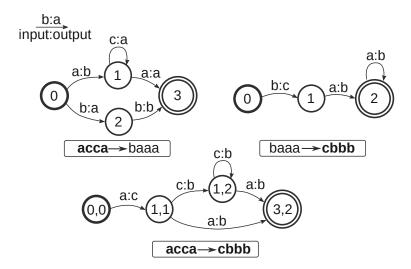

| 2.4 | Example WFST composition between two graphs from Mohri. et al [79]. The button graph is the result of composing the two graphs at the top. Each node in the composed graph is obtained by merging a node from each of the input graphs. For example, the node (1,2) is obtained by merging node 1 from the first graph and node 2 from the second graph.                                                                                                       | 42 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

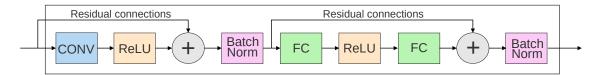

| 2.5 | Time-Depth Separable Neural Network (TDS)                                                                                                                                                                                                                                                                                                                                                                                                                      | 45 |

| 2.6 | CTC paths for the word <i>cat</i> within a sequence of 9 time-steps. The arrows represent example paths. After removing repetitions and blanks (represented by $\epsilon$ , all the paths produce the same word)                                                                                                                                                                                                                                               | 46 |

| 4.1 | High level diagram of the complete system.                                                                                                                                                                                                                                                                                                                                                                                                                     | 56 |

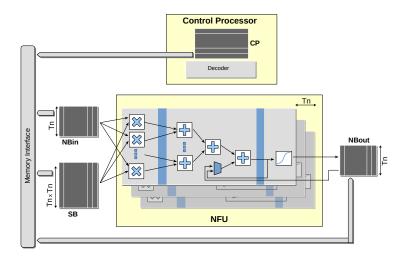

| 4.2 | Architecture of the DNN accelerator based on $DianNao$ [20]. In addition to the Neural Function Unit (NFU), it includes three on-chip buffers to store inputs ( $NBin$ ), weights ( $SB$ ) and outputs ( $NBout$ ). The main configuration parameter is $Tn$ , which sets the number of parallel neurons and parallel synapsis per neuron in the NFU. $Tn$ also determines the port width of the memories                                                      | 57 |

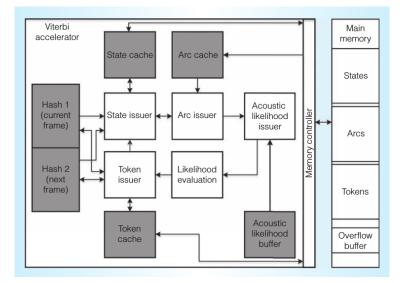

| 4.3 | Architecture of the viterbi accelerator. It consists of: several <i>Issuer</i> components to load/store data from/to the main memory, each with an associated cache memory; an additional module to compute the likelihood of the paths and two <i>hash</i> memories to keep the active tokens for the current and the next frame.                                                                                                                             | 58 |

| 4.4 | Cumulative distribution of the RTF for all utterances in the test set. The plots correspond to the execution of the kaldi system on the 3 hardware architectures: CPU, CPU-GPU and CPU-ACCEL.                                                                                                                                                                                                                                                                  | 61 |

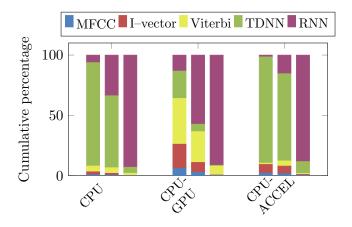

| 4.5 | Execution time breakdown for the different ASR components obtained on the 3 hardware architectures. For each architecture, the three bars represent the utterances at percentiles 0, 50 and 100 in the RTF plot (Figure 4.4).                                                                                                                                                                                                                                  | 62 |

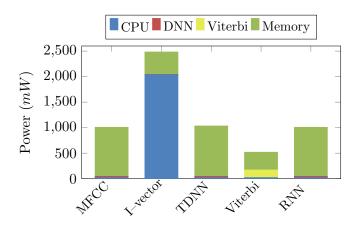

| 4.6 | Power dissipation during the computation of the ASR components. Each bar represents the power dissipated by each ASR component, broken down by hardware subsystem.                                                                                                                                                                                                                                                                                             | 63 |

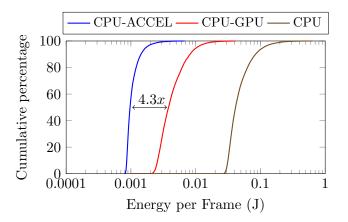

| 4.7 | Cumulative distribution of the energy per frame for decoding for all utterances in the test set. The plot shows the energy for the execution on the 3 hardware platforms: CPU, CPU-GPU and CPU-ACCEL.                                                                                                                                                                                                                                                          | 63 |

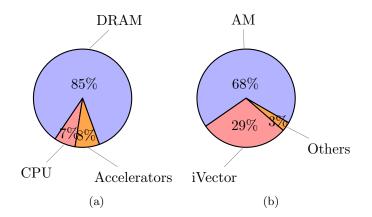

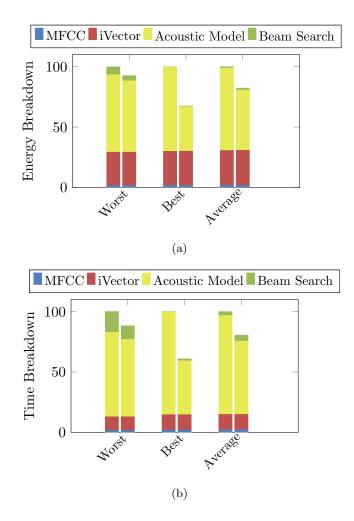

| 5.1 | Breakdown for energy consumption during ASR evaluation on the mobile SoC pre-<br>sented in Section 4. Chart (a) shows the energy breakdown among hardware compo-<br>nents during the AM evaluation. Here, it can be seen how reads and writes from the<br>DRAM are responsible for most of the consumed energy, whereas chart (b) shows the<br>energy breakdown by ASR component, where the clear bottleneck is the Acoustic<br>Model TDNN evaluation, whereas | 66 |

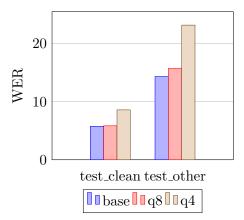

| 5.2  | Comparison of the WER loss respect to the non-quantized model for various levels<br>of quantization. While quantizing to 8 bits has a small impact on WER, more<br>aggressive quantization sensibly degrades accuracy                                                                                                                                                                                                                                                    | 67 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

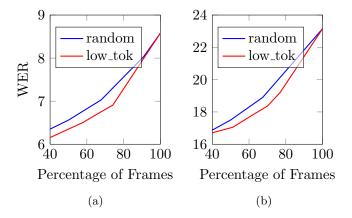

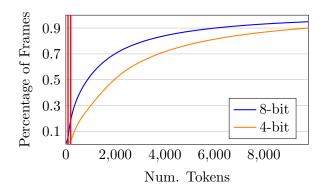

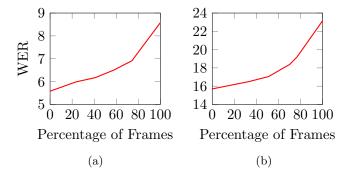

| 5.3  | WER for a varying percentage of frames evaluated at low precision for a) test_clean<br>and b) test_other. The curves represent the cases when the frames for low-precision<br>evaluation are those with less number of tokens (high confidence), and when they<br>are chosen randomly                                                                                                                                                                                    | 68 |

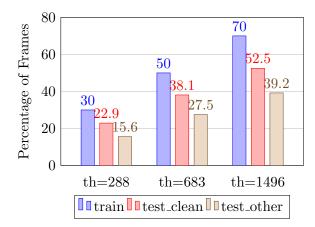

| 5.4  | This plot shows the ratio of frames classified for low precision computation in our technique when using a fixed threshold. To obtain this threshold, the train set is evaluated at high precision. Then, all the frames are sorted according to the number of hypotheses expanded during Beam Search. The threshold value is chosen from the number of hypotheses expanded at different percentiles. As we can see, the desired ratio is not achieved in the test sets. | 69 |

| 5.5  | When low precision is used, the number of tokens expanded during Beam Search generally increases.                                                                                                                                                                                                                                                                                                                                                                        | 69 |

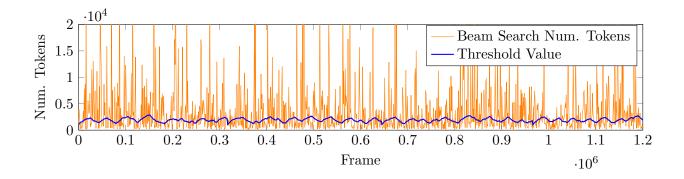

| 5.6  | Threshold value computed by the proposed heuristic compared with the number of tokens expanded by Beam Search. The plot shows a span of 1.2 million frames at $\frac{1}{1000}$ sampling rate                                                                                                                                                                                                                                                                             | 70 |

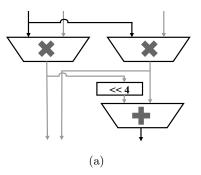

| 5.7  | Schematic of the multiplier unit included in our design. Light grey arrows repre-<br>sent half-precision values. This unit receives two full-precision values, which are<br>interpreted as one full-precision and two half-precision values when operating in<br>half-precision mode                                                                                                                                                                                     | 71 |

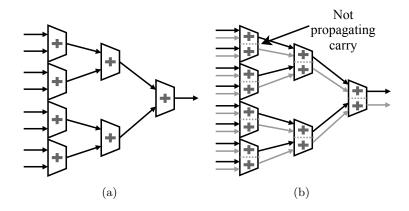

| 5.8  | Schematic of a basic add-tree $(5.8(a))$ and our duplex add-tree when operating in half-precision mode $(5.8(b))$ . In the latter, each arrow represents a half-precision value.                                                                                                                                                                                                                                                                                         | 72 |

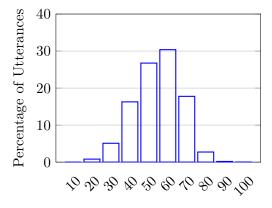

| 5.9  | Frequency of utterances (vertical axis) grouped by the percentage of their frames computed at low precision (horizontal axis).                                                                                                                                                                                                                                                                                                                                           | 74 |

| 5.10 | Energy consumption (a) and execution time (b) normalized to the baseline. The bars in each plot represent: Worst Utterance, Best Utterance and Test Set Average for the baseline and proposed scheme respectively.                                                                                                                                                                                                                                                       | 75 |

| 5.11 | Sensitivity analysis of the percentage of frames set as target for low precision evalu-<br>ation. The curves represent the WER obtained when some percentage of frames is<br>evaluated in low precision for test_clean (a), and test_other (b)                                                                                                                                                                                                                           | 76 |

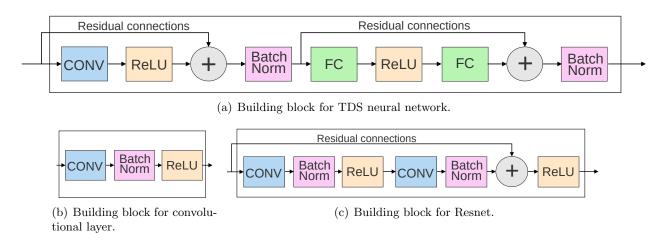

| 6.1  | Building blocks for different DNNs                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78 |

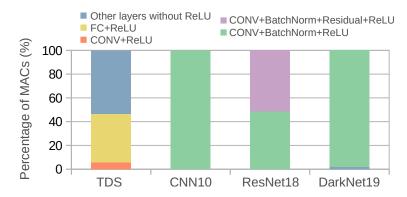

| 6.2  | Percentage of MACs in each type of layer for a set of DNN aplications                                                                                                                                                                                                                                                                                                                                                                                                    | 79 |

| 6.3  | ReLU inputs for binarized neuron (x-axis) versus ReLU inputs for base precision neuron (y-axis)                                                                                                                                                                                                                                                                                                                                                                          | 81 |

# LIST OF FIGURES

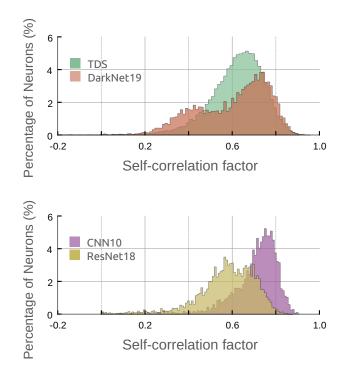

| 6.4  | Distribution of neurons according to the Pearson correlation coefficient of the binary<br>and base-precision ReLU inputs                                                                                                                                                                                              | 2 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 6.5  | Effect of the correlation-based threshold on accuracy loss and percentage of opera-<br>tions saved for different DNNs                                                                                                                                                                                                 | 3 |

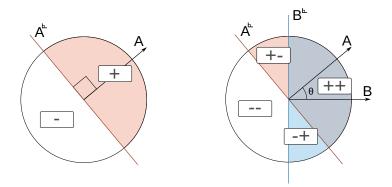

| 6.6  | The line perpendicular to $A$ partitions the circle into 2 sectors. Given a random $C$ , the sign of $C \cdot A$ is determined by the partition in which $C$ falls. If another vector $B$ is added (right figure), the circle is partitioned into 4 sectors, which determine the signs of $C \cdot A$ and $C \cdot B$ | 1 |

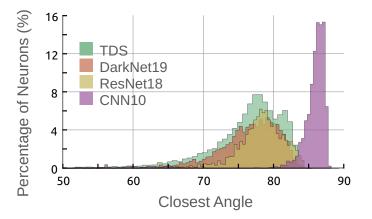

| 6.7  | Distribution of angles between each neuron and its closest neuron                                                                                                                                                                                                                                                     | 5 |

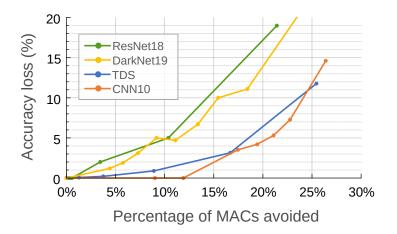

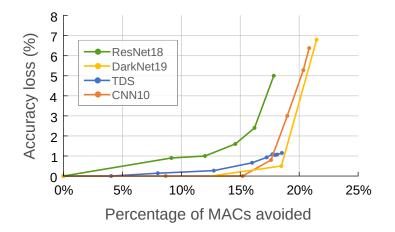

| 6.8  | Accuracy loss versus percentage of computations avoided for the hybrid <i>Mixture-of-</i><br><i>Rookies</i> predictor                                                                                                                                                                                                 | 3 |

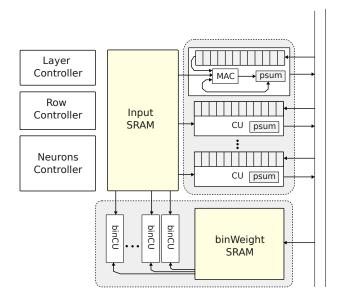

| 6.9  | Accelerator with support for <i>Mixture-of-Rookies</i> ReLU output predictor                                                                                                                                                                                                                                          | 7 |

| 6.10 | Format to store the DNN in external memory                                                                                                                                                                                                                                                                            | ) |

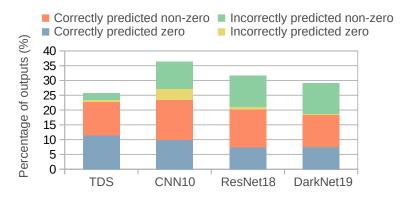

| 6.11 | Percentage of outputs that are correctly and incorrectly predicted as zero or nonzero<br>by our <i>Mixture-of-Rookies</i> predictor                                                                                                                                                                                   | ) |

| 6.12 | Performance and energy savings achieved by our <i>Mixture-of-Rookies</i> ReLU output predictor compared to the baseline                                                                                                                                                                                               | ) |

| 7.1  | Architecture of ASRPU                                                                                                                                                                                                                                                                                                 | 1 |

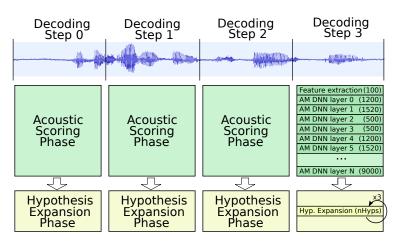

| 7.2  | ASR process executed on ASRPU                                                                                                                                                                                                                                                                                         | 1 |

| 7.3  | Threads in the PE pool                                                                                                                                                                                                                                                                                                | 7 |

| 7.4  | Processing Element (PE)                                                                                                                                                                                                                                                                                               | 3 |

| 7.5  | Size (KB) of each layer of the TDS DNN included in the ASR system. The left plot shows the convolutional layers whereas the right plot shows the fully-connected layers103                                                                                                                                            | 3 |

| 7.6  | The left bar plots show the component-level breakdown of area and peak power of ASRPU. The right plots show the distribution of static and dynamic power 104                                                                                                                                                          | 1 |

| 7.7  | Execution time for the TDS ASR system running in ASRPU                                                                                                                                                                                                                                                                | 1 |

# List of Tables

| 4.1 | WER obtained by different state-of-the-art systems on the Librispeech Corpus | 54  |

|-----|------------------------------------------------------------------------------|-----|

| 4.2 | Memory requirements for the models of the ASR system                         | 55  |

| 4.3 | Characteristics of the CPU                                                   | 59  |

| 4.4 | Characteristics of the GPU                                                   | 59  |

| 4.5 | Parameters for the DNN accelerator                                           | 59  |

| 4.6 | Parameters for the Viterbi accelerator                                       | 60  |

| 7.1 | Commands provided by the command decoder                                     | 100 |

| 7.2 | Configuration parameters of the accelerator                                  | 103 |

# Introduction

This chapter introduces the motivations and objectives behind this thesis. The first section provides our motivation to study automatic speech recognition, outlining the importance of lowpower speech recognition for future computing systems. The next section describes the scope of our work and our contributions. The following section provides a discussion of related work, particularly, describing those works aimed at accelerating DNN inference and Beam Search, the main components of speech recognition systems. The final section describes the organization of this document.

# 1.1 Motivation

Around the 1960s, the first graphic interfaces started appearing (with examples such as *Sketch*pad and Stanford's *On-Line System*). During the 1980s, *Apple* and *Microsoft*, among others, popularized graphical interfaces, promoting the widespread adoption of computers among the regular public. Before that, mostly trained professionals and researchers had access to computers, which were operated via written commands. From that point forward, written commands remained only as specialized interfaces for professionals and highly knowledgeable individuals. Graphic interfaces expanded the use cases of computers and made them easier to use and understand.

Similarly, the current expansion of machine perception technologies will make it straightforward to interact with computers and machines, further expanding their range of use cases. Machine perception refers to those technologies that allow computers to interpret sensory data in a way similar to humans. It includes a broad range of technologies, such as robotic vision, tactile perception and automatic speech recognition.

Among the technologies within the machine perception space, Automatic Speech Recognition

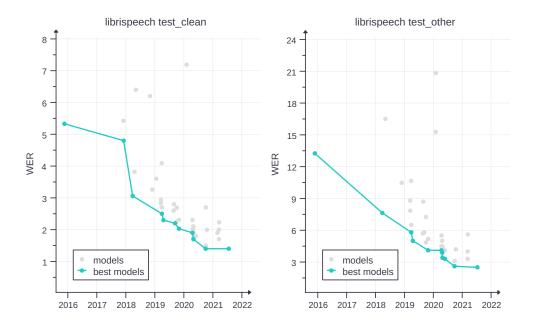

Figure 1.1: Word Error Rate (WER) of different ASR systems on the librispeech test-clean and test-other benchmarks [7].

(ASR) is probably the one with more potential to shape future human-machine interactions. We can currently see the impact of these technologies. Speech-based virtual assistants are very popular devices. Most people are already familiar with Microsoft's Cortana [2], Amazon's Alexa [1] or Apple's Siri [6]. Dictation engines, such as Google's Text-To-Speech are built in many smartphone keyboards, online translation tools and search engines [95]. Furthermore, from an economic perspective, the Global speech and voice recognition market is expected to experience very promising growth during the next few years. In a Fortune Business Insights report [8] published in 2019, authors forecast a 19.8% Compound Annualized Grow Rate in the period from 2019 to 2026.

This unprecedented expansion of ASR is powered by an outstanding increase, during the last few years, in the accuracy of speech decoders. Figure 1.1 [7] shows the *Word Error Rate (WER)* reported in various papers published between 2016 and 2021. DeepSpeech2 [12], published in 2016, obtains a WER of 5.33, i.e. one decoding error per 19 words in the ground truth, whereas in Chang et. al [126], published in 2021, the authors achieve an impressive WER of 1.4, i.e. 1 error per every 71 words, with a *Conformer*-based system.

That level of accuracy is partially responsible for opening ASR for many mainstream uses, as seen by the proliferation, during the last decade, of consumer products based on ASR. In addition to highly accurate, speech recognition must also be fast and reliable. However, given the high compute intensity of ASR, most speech decoding is currently performed on servers [103, 64, 49], which results in unreliable ASR-based services (network connection is not always available) and high latency (specially word-to-word latency). Besides, speech data is personal and must be handled cautiously. Sending speech files to servers raises privacy concerns in a society that is increasingly worried about the handling of personal data by big technology companies. Many advocate for on-edge ASR as the solution to these problems. However, on-edge decoding does not come without challenges. Edge devices, such as home computers, smartphones and even smart appliances, generally lack the hardware resources and data volumes required to exploit the huge parallelism found in ASR algorithms. Furthermore, streaming decoding, which is a desirable feature for ASR, given the extremely low word-to-word latency it provides, introduces additional challenges by further limiting the amount of parallelism in ASR algorithms. Due to these challenges, it is often unfeasible to deploy highly accurate ASR decoders in edge devices. Nowadays, it is common to deploy smaller and less demanding decoders for on-edge ASR, despite being less accurate.

In this thesis, we aim to improve the performance and efficiency of automatic speech recognition algorithms when constrained to the limited resources of low-power edge devices. We focus on the hardware architecture, generally assuming a heterogeneous architecture with several accelerators in addition to the CPU and a memory hierarchy, and propose innovations to increase performance and reduce energy consumption.

# 1.2 Problem Statement, Objectives and Contributions

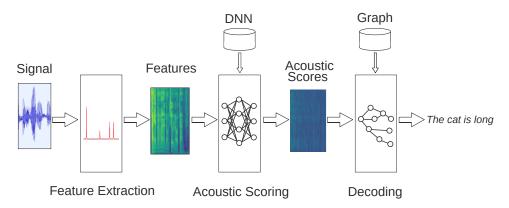

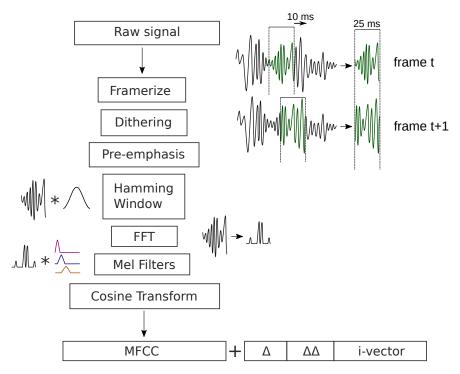

ASR is usually performed in three major steps (Figure 1.2). (1) First, the signal is broken down into overlapping fragments and transformed into a sequence of *feature frames*. (2) Each of these frames is classified into acoustic tokens by an *Acoustic Model (AM)*. For most current systems, the AM is a *Deep Neural Network (DNN)*. The classification of the signal into acoustic units performed by the DNN is not rigid. Instead, the AM classifies the feature frames by generating, for each of them, a vector of probabilities. (3) The last stage, *decoding*, generates a transcription from the acoustic scores. The simplest approach to obtain the transcription takes the tokens with the highest probability on each frame and chains them together. However, more sophisticated approaches, e.g. integrating a lexicon and/or a language model, generally result in better accuracy. When a lexicon or a language model is included, the best scoring transcription can not be obtained by simply taking the single best token for each frame. Instead, a search algorithm, such as *Viterbi Beam Search*, traverses the graph of possible transcriptions (*lattice*) to find the token sequence with the best overall score.

Usually, to maximize efficiency, the input utterance is first captured from beginning to end and then processed. This allows the hardware to maximize data reuse. However, this results in high word-to-word latency because no output is generated until the entire utterance is captured and processed. To achieve low word-to-word latency, the input utterance is processed frame-by-frame (*streaming decoding*), generating partial transcriptions in real-time. Streaming decoding introduces an additional challenge by severely limiting the amount of data reuse available for the hardware. Furthermore, because memory access is the main bottleneck in ASR, the difference in performance between the two options is significant [107].

As previously mentioned, accuracy has kept steadily increasing during the last few years. However, the increase in accuracy is accompanied by an increase in model size, which generally results in higher compute intensity. *Contextnet* [45] is a 31.4M parameter DNN that achieves 2.4 WER on librispeech test\_clean, a speech recognition benchmark, and 2.1 WER when scaled up to 112.7M pa-

Figure 1.2: Diagram of a generic Automatic Speech Recognition system. First, a raw signal is transformed into features, and then into acoustic scores. The decoder combines the acoustic scores with the decoding graph to obtain the most likely transcription for the input signal.

rameters. Similarly, The Conformer [39] network achieves 2.3 and 2.1 WER on the same benchmark with 30.7M and a 118.8M parameters, respectively. Synnaeve et.al [106] train 3 types of networks: a 500M parameter ResNet that achieves 2.67 WER, a 500M Time-Depth Separable (TDS) network that achieves 2.35 WER and a 296M parameter Transformer [108] network that achieves 2.25 WER. Baevski et. al [15] train a 317M parameter transformer network that reach 2.2 WER. SpeechStew [19], a 100M parameter DNN, achieves 2 WER, xu et. al [115] achieve 1.7 WER with a 300M parameter network and zhang et. al [126] achieve 1.5 WER with a 1B parameter network.

Another challenge for on-edge ASR comes from the ample diversity of algorithms. Hybrid systems rely on a complex decoding graph formed by composing several independent WFST graphs, including HMMs. On the other hand, E2E systems rely on DNNs and simplify drastically the decoding graph, or even avoid it altogether. The main types of end-to-end systems are those based on *Connectionist Temporal Classification (CTC)* [37] and those based on *seq2seq*[18]. The main difference among them resides in the way they expand hypotheses and compute hypothesis scores.

One of the consequences of these three factors: the fast pace of innovation, high computational cost and vast heterogeneity, is that performing ASR on edge devices is challenging. Consequently, ASR is usually performed on servers, which provide more than enough compute power for the task and where ASR systems can be updated easily. ASR is so computationally expensive that common mobile SoCs are ill-equipped to perform highly accurate decoding within reasonable latency. Hardware acceleration helps in reducing energy cost and latency [120, 107], but, besides high energy-efficiency, the architecture must be flexible enough to accommodate the heterogeneity of current and future systems, while being easily programmable.

In this thesis, we analyze state-of-the-art ASR systems and propose low-power architectural solutions to reduce energy consumption and increase its performance on edge devices. The following paragraphs summarize the different problems we studied and the solutions we proposed to tackle them.

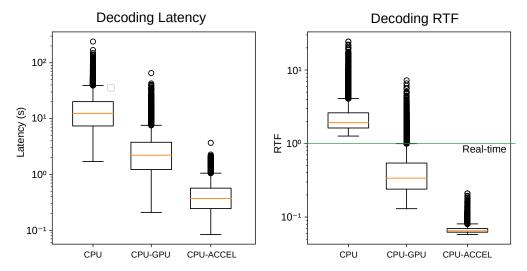

Figure 1.3: Performance of all the utterances in the librispeech test and dev sets decoded by the Kaldi TDNN ASR system on three architectures: CPU, CPU-GPU and CPU-ACCEL. The left-most plot shows the time it took to decode each utterance, where the right-most figure shows the Real Time Factor (RTF). The RTF is the decoding time divided by the utterance time (lower means better).

#### 1.2.1 A Heterogeneous System for low-power ASR

Speech decoding on low-power edge devices is challenging. Figure 1.3 shows the latency for the execution of an ASR system on a Tegra TX1, first on CPU, and then using GPU acceleration. When the ASR is executed on the CPU, all utterances are decoded slower than in real-time, with some of them requiring an order of magnitude longer than real time to decode. When the DNN is accelerated in the mobile GPU, the performance increases significantly, with most utterances decoded in real-time. However, since the GPU only accelerates the DNN, those utterances dominated by the Viterbi Search are not benefited much by the GPU. Consequently, the distribution of latency is broadened. Some utterances are decoded in as little as 0.2 RTF whereas others take up to 7 times real-time.

The decoder is a Hybrid HMM-DNN system implemented in Kaldi [85]. The Acoustic Model DNN in this system is a TDNN network [84]. Decoding is performed over a large graph that combines HMMs, to model tri-phones; a lexicon, to map phonemes to words and a grammar (Language Model) composed of around 200k words. This graph is referred to as *HCLG* graph. In order to alleviate the bottlenecks, we enhance the previous platform with accelerators for the DNN inference and the Beam Search. This heterogeneous SoC contains an ARM CPU, 4 GB of DRAM memory, an accelerator for DNN inference and an accelerator for the Beam Search. The Beam Search accelerator is a scaled-down version of the accelerator proposed on [120].

By offloading the most compute-demanding components of the ASR system to specifically designed accelerators, we overcome the inefficiencies of general-purpose hardware, such as CPUs and GPGPUs. In this case, the CPU is kept idle during the computation of the DNN inference and the Beam Search, saving large amounts of energy and accelerating the decoding process. Similarly, the accelerators are much smaller than the mobile GPU included in the Jetson TX1 board, which results in significant energy savings. Compared to the CPU-GPU platform, the utterances are

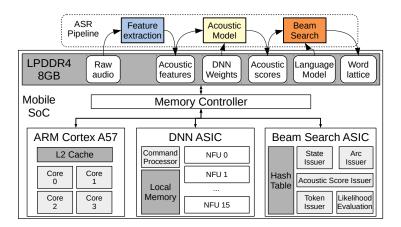

Figure 1.4: ASR pipeline on the proposed hardware platform.

decoded 4.5x faster on the proposed platform, keeping the latency below 0.5 RTF for all the utterances in the test set. Additionally, the energy consumption per second of decoded audio is reduced by 4.3x compared to the CPU-GPU system.

## 1.2.2 Leverage Run-time Decoding Confidence

Figure 1.4 shows the ASR pipeline executed in our platform. Feature extraction computes the MFCC vectors from raw audio. The acoustic model TDNN performs inference over those MFCC vectors to obtain the acoustic scores, which are combined with the scores obtained from the Language Model (The HCLG graph) to obtain a word lattice. This word lattice can then be re-scored with an additional language model. However, the improvement in accuracy provided by the language model re-scoring step is modest when compared to the significant overhead incurred. For that reason, instead of performing LM re-scoring, we obtain the transcription directly from the lattice.

At this point, the AM DNN inference is the main bottleneck of the system, accounting for, on average, 82% of the execution time and 68.3% of the energy consumption. A popular solution to improve the performance of DNN inference is to decrease the arithmetic precision of the MAC operations. The arithmetic precision used during training is normally 32 bit Floating Point, but it can be reduced down to 8 bit integer. However, reducing it further has a significant effect on accuracy.

In streaming ASR, instead of decoding the entire utterance all at once, or in big batches, the utterance is decoded in small batches of input frames. This leads to higher energy consumption due to lower data reuse, but significantly improves word-to-word latency. During streaming ASR, a small batch of inputs is processed with the AM. Then, the decoder expands the hypotheses, consuming the available acoustic scores. At this point, the best scoring partial hypotheses can be shown in the screen to provide the user with real-time decoding feedback. Additionally, other software components that consume the speech input can start processing the partial transcription in order to decrease response latency.

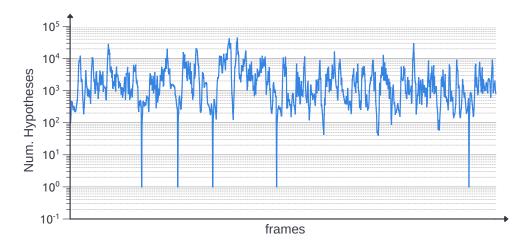

We make a few observations regarding Streaming ASR: First, the number of hypotheses varies drastically during decoding (Figure 1.5), and second, low accuracy affects different frames differently. Specifically, frames with few hypotheses to expand are less sensitive to low arithmetic precision than frames with higher number of hypotheses to expand. We call the relative number of hypotheses on each frame *run-time decoding confidence*. Frames with many hypotheses have *low confidence* whereas frames with few hypotheses have *high confidence*.

We propose a technique that leverages the previous observation to improve performance and reduce energy consumption. The main idea is to reduce the arithmetic precision for the AM inference when the confidence of the decoder is high. For that purpose, we keep two AM DNNs in memory: The first one is quantized to 8 bits and is used during low-confidence frames. The second DNN is quantized to 4 bits and is reserved for high-confidence frames. To efficiently implement this technique in the hardware, we design dual-precision multiplication and add-tree units, which can operate in both 8-bit and 4-bit precision. They are included in the DNN inference accelerator instead of the regular arithmetic units.

To decide which acoustic model to use for each audio frame, we measure the number of hypotheses generated during the previous decoding step and compare it with a threshold. This threshold is set by measuring the number of hypotheses generated during the decoding of a sub-set of the librispeech train set. We first manually set a threshold that would result in 50% of the frames being scored with the low-precision AM, while the other 50% would be decoded with the highprecision AM. However, we observe that the percentage of frames evaluated at low-precision does not match the expected 50%. This is mainly because changing the precision during acoustic scoring has an impact on decoding, as well. Those frames when the DNN inference for acoustic scoring is performed in low precision, tend to generate less confident scores, which in turn results in more hypotheses being generated (less overall decoding confidence). Because of this, a fixed threshold is not a convenient solution. Instead, we introduce a mechanism to update the threshold in run-time. This mechanism increases or decreases the threshold depending on the average number of frames evaluated in low (and high) precision to keep a fixed ration.

We implemented this technique in the heterogeneous system from the previous section, obtaining further savings in energy and increased performance. Supporting the proposed scheme requires changes in the DNN accelerator, which has to support 8 bit and 4 bit DNN inference and the Viterbi accelerator, which has to register the number of hypotheses expanded during each decoding step and update the threshold.

According to our experimental results, this technique results in 16.9% less energy consumption and a 18.5% reduction in execution time, compared to the baseline platform without run-time adaptation. By restricting low-precision arithmetic operations to high-confidence frames, we can keep the accuracy loss below 1% for test\_clean and 1.35% for test\_other.

#### 1.2.3 Detect and Remove Ineffectual Computations

Modern DNNs often contain layers activated with *Rectified Linear Unit (ReLU)* functions [12, 48, 39, 66]. The ReLu activation function [62] is like a high-pass filter. When a neuron generates a positive value, it is passed to the next layer unmodified. When it generates a negative value, it

Figure 1.5: Number of hypotheses expanded at each frame during the decoding of 10 seconds of speech.

is clipped to 0. This results in many zeroes being generated.

For example, when decoding with the TDS DNN [84], a DNN for end-to-end ASR, we observed than more than 80% of the outputs of the neurons are clipped to zero. Given that the DNN accounts for the majority of the dissipated energy and execution time, this creates a huge opportunity for optimization.

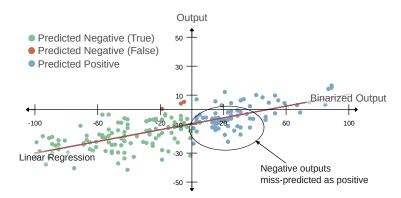

Several works in the literature propose prediction schemes to detect these zeroes and avoid ineffectual computations. These predictors detect before whether the input of the ReLU will be positive or negative. If the output is predicted to be negative, the neuron is not computed. Instead, a zero is written to memory. There are three main approaches to predict ReLU outputs: Those based on self correlation [71, 102, 17], i.e. correlation between a neuron and the same neuron computed in lower arithmetic precision, those based on spatial correlation [98, 97], i.e. correlation among neurons in the same layer and those based on sub-sampling [10].

In this work, we propose a novel prediction scheme for ReLU activated neurons. Our predictor is composed of two components and the output of a neuron is only predicted to be negative when both components agree on that. The two components are: (1) A spatial-correlation predictor that groups neurons that tend to generate negative values for the same inputs. For every input, it first computes the output of a representative neuron for each group and predicts that the rest of the neurons in the group will have the same outcome. (2) A self-correlation predictor looks at neurons that correlate well with the 1-bit quantized version of themselves. For those neurons, it first computes the output with 1-bit precision. The sign in the resulting value, adjusted to account for shifts in the correlation line, is taken as a prediction for the sign of the value computed with high prediction.

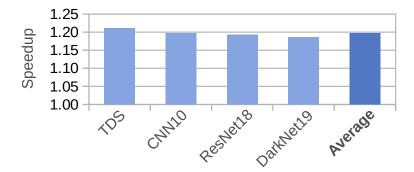

Figure 1.6 shows the results obtained in our experiments with this technique.

Figure 1.6: Speedup obtained by the mixture-of-rookies technique on a set of DNN tasks.

#### 1.2.4 A Programmable Architecture for ASR

One important challenge for hardware-accelerated ASR comes from the fact that the ASR system space is heterogeneous and it is evolving fast. Consequently, Hardware support for speech recognition must be flexible enough to support many different implementations. Otherwise, it risks becoming obsolete very soon.

However, most proposals in the literature are specific for certain implementations. In this work, we propose ASRPU, a parallel programmable architecture for ASR. This architecture divides the ASR process into two phases: (1) Acoustic Scoring, to transform the raw signal into acoustic score vectors and (2) Hypothesis expansion, to generate new hypotheses from the hypotheses generated during the previous step.

Acoustic Scoring is implemented by the programmer. The programmer writes a set of programs that are launched in sequence by an ASR controller. The programmer can specify how many parallel threads should be launched for each program or it can be determined during run-time via a special *setup* program that is launched right before each program from the sequence. Hypothesis Expansion is implemented by a single program, which is executed several time to expand all the hypotheses generated by the previous decoding step.

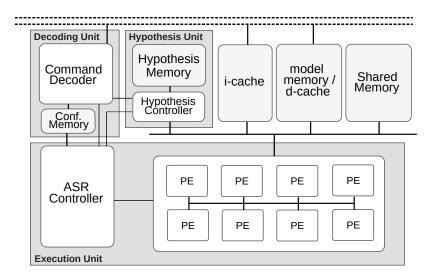

Figure 1.7 shows the architecture of the proposed accelerator. It is divided in three major components. The execution units contains the programming elements that execute the kernel threads, the hypotheses unit sorts and prunes the hypotheses generated by the hypothesis expansion threads and the decoding unit decodes commands and configures the accelerator. The ASRPU accelerator contains a d-cache shared among all the PEs. During the execution of the acoustic scoring phase, this memory serves the purpose of a model memory. The programmer can configure the accelerator to prefetch the model data into this memory.

We implemented a state-of-the-art end-to-end ASR system and estimated how long it will take ASRPU to execute it. When configured in a 1.8W setup, the accelerator can execute the ASR system in 2x real-time. This level of performance and the low power consumption makes ASRPU an excellent candidate to include in edge devices.

Figure 1.7: Architecture of ASRPU

# 1.3 Related Work

The literature on hardware acceleration for ASR includes a wide variety of proposals. Some works propose chips that handle the entire ASR process whereas others assume that the ASR process is executed by the CPU and propose accelerators to offload the most compute-demanding components. In this section, we provide a review of related works, focusing on chips for ASR, accelerators for beam search and DNN inference and techniques to improve the performance of those accelerators.

## 1.3.1 Early Proposals

Early proposals related to hardware acceleration for ASR were mostly focused on HMM-GMM decoders [77, 70, 24]. These systems, generally implemented in CMU's Sphinx, contain vocabularies with less than 100k words (e.g. 5k/20k-word Wall Street Journal, 64K-word Broadcast News,...). More recently, Tabani et. al. [107] proposed an accelerator for the PocketSphinx system, configured with a 130k word vocabulary and trained with the librispeech benchmark. PocketSphinx is a version of CMU Sphinx aimed at portability. The accelerator is a  $0.94mm^2$ , 110mW chip and provides a reduction of 5.89x in decoding time and 241x in energy consumption compared to a mobile GPU baseline. Early HMM-GMM ASR system used to be very popular. However, ASR has gone a long way since then and now most of the ASR systems are either Hybrid HMM-DNN or end-to-end. These systems are primarily limited by the performance requirements of large DNNs and decoding graphs, instead of GMM calculations. In our work, we focus on the challenges of modern ASR architectures. Large DNNs require billions of MAC operations per second and exhibit huge opportunities for parallelization, shifting the performance and energy bottlenecks to the memory access. Also, increasingly large decoding graphs require efficient and adaptable accelerators to handle them. The proposals in this work are aimed at accelerating modern Hybrid and end-to-end

systems. Hence, we propose techniques that do not assume a specific system, but instead leverage untapped properties of ASR systems in general, such as run-time confidence, to alleviate their bottlenecks.

More modern proposals to accelerate HMM-DNN systems include the work by Price et al. [90]. That work proposes a chip that performs from *Voice Activity Detection* (*VAD*) and audio capture, to Viterbi-based decoding. The area of the chip is  $13.18mm^2$ , and consumes 11.27mW (not including power from off-chip components, such as main memory, which is the main bottleneck according to our models) while running a 145k word vocabulary benchmark. That work focuses on a single ASR system, which is thoroughly accelerated. However, the current landscape contains plenty of different ASR systems. Furthermore, breakthroughs in the ASR field are not uncommon. Consequently, the main limitation of that work is the rigid design of the chip, that severely restricts its applicability, as it assumes that the DNN fits in the internal memory and only requires a rather limited set of operations. During our work, we abstract away many specific details of the ASR system, designing architectures that support a wide range of systems. For example, in chapters 5 and 6, we propose techniques to leverage run-time decoder confidence and activation sparsity, which can be observed in many ASR systems, and implemented in most accelerator architectures. Finally, in chapter 7, we propose a programmable accelerator that makes very few assumptions about the design of the ASR system.

#### 1.3.2 Beam Search Acceleration